1

Изобретение относится к импульсной технике и может быть использовано в измерительной технике и автоматике.

Известен делитель частоты следования импульсов, содержащий счетчик, два элемента совпадения, элемент ИЛИ и генератор дополнительной частоты, изменение коэффициента деления которого основано на исключении входных импульсов и добавлении между входными импульсами сигналов дополнительной частоты, смещенных относительно входных импульсов I.

Однако необходимость введения дополнительной частоты приводит к низкому быстродействию.

Наиболее близким по технической сущности к изобретению является делитель частоты следования импульсов с переменным коэффициентом деления, содержащий делитель частоты, опорный генератор, блок управления, содержащий калибратор, элемент ИЛИ, элементы совпадения, первые входы которых соединены с выходом опорного генератора, вторые входы первого и второго элемента совпадения - с выходом калибратора, второй вход третьего элемента совпадения - с выходом второго элемента совпадения, а выход третьего элемента совпадения соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого разряда делителя частоты, а выход - с входом второго разряда делителя частоты, при этом второй вход второго элемента совпадения подклкУ чен к щине знака коррекции, вход калибратора - к шине разрешения коррекции, а выход первого элемента И соединен с входами первого разряда делителя частоты 2.

Целью изобретения является повышение быстродействия.

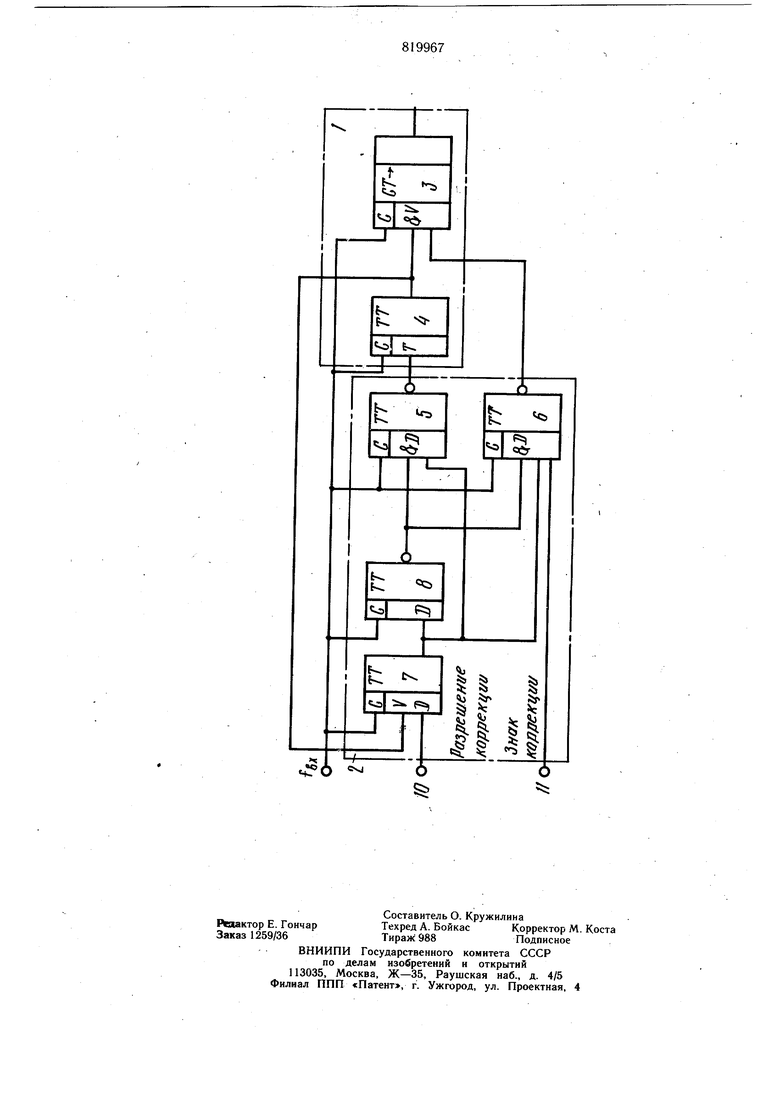

Достигается это тем, что в управляемый делитель частоты следования импульсов, содержащий делитель частоты, состоящий из Т-триггера и счетчика импульсов, и блок управления, первый, второй и третий входы которого подключены соответственно к входной щине, щинам разрещения коррекции и знака коррекции, а первый и второй выходы соответственно к счетным входам Т-триггера и счетчика импульсов делителя частоты, четвертый вход- блока управления соединен с выходом Т-триггера и дополнительным счетным входом счетчика импульсов делителя частоты, входы синхронизации которых подключены к входной шине, при этом блок управления содержит DV- триггер, 8О-тр/иггеры и О-триггер, входы синхронизации которых подключены к входной шине и являются первым входом блока удравления, управляюший вход DV-триггера, являющийся четвертым входом блока управления соединен с выходом Т-триггера делителя частоты, информационный вход, являющийся вторым входом блока управления, - с шиной разрешения коррекцйи. а выход - с информационным входом Dтриггера и первыми информационными входами первого и второго 8О-триггеров, вторые информационные входы которых соединены с инверсным выходом D-триггера, а инверсные выходы первого и второго 8Uтриггеров, являющиеся первым и вторым выходами блока управления соединены соответственно со счетным входом Т-триггера и дополнительным счетным входом счетчика импульсов делителя частоты, при этом третий информационный вход второго 8Dтриггера является третьим входом блока управления, На чертеже изображена структурная электрическая схема устройства. Оно содержит делитель 1 частоты, блок 2 управления, счетчик 3 импульсов, Т-триггер 4, 8О-триггеры 5, 6, DV-триггер 7; Dтриггер 8, шина 9 входная, шина 10 разрешения коррекции, шина 11 знака коррекции. При отсутствии сигнала на шике 10 устройство выполняет функции делителя частоты с коэффициентом деления Ка. С появлением сигнала а шине 10 DV-триггер 7 осуществляет его привязку к входной частоте f|. в моменты, когда Т-триггер 4 находится в единичном состоянии. Это накладывает ограничение на сигнал «разрешение коррекции, длительность которого должна быть не менее 2,5g- (при скважности входной частоты равно1и двум). Принятый сигнал задерживается на один период входной частоты для дальнейшего выделения из него переднего фронта, который фиксируется в SD-TpHrrepe 5 и при наличии сигнала на шине 11 - в 8D-TpHrrepe 6. Инверсный сигнал с выхода 8D-TpHrrepa 5 осуществляет останов Т-триггера 4. Если же при этом сигнал на шине 11 отсутствует. то на выходе 8D-TpHrrepa 6 присутствует «единица и производится изменение соетояния счетчика 3, что эквивалентно уменьшению коэффициента деления на «единицу (добавление). Наличие сигнала на шине 11 приводит к останову счетчика 3 на Один период входной частоты. Это эквивалентно увеличению коэффициента деления на «единицу (исключение). Введение новых элементов и связей между ними позволяет увеличить быстродействие устройства. Формула изобретения . Управляемый делитель частоты слеДования импульсов, содержащий делитель частоты, состоящий из Т-триггера и счетчика импульсов, и блок управления, первый. второй и третий входы которого подключены соответственно к входной шине, щинам разрещения коррекции и знака коррекции, а первый и второй выходы - соответственно к счетным входам Т-триггера и счетчика импульсов, делителя частоты, отличающийся тем, что, с целью повышения быстродействия, четвертый вход блока управления соединен с выходом Т-триггера и дополнительным счетным входом счетчика импульсов делителя частоты, входы синхронизации которых подключены к входной шине. 2. Делитель по п. 1, отличающийся тем, что блок управления содержит DV-триггер, 8О-триггеры и D-триггер, входы синхронизации которых подключены к входной шине и являются первым входом блока управления, управляющий вход DV-триггера, являющийся четвертым входом блока управления соединен с выходом Т-триггера делителя частоты, информационный вход, являющийся вторым входом блока управления - с щиной разрешения кор-. рекции, а выход - с информационным вхоДом D-триггера и первыми информационными входами первого и второго 8D-тpиггеров, вторые информационные входы которых соединены с инверсным выходом Dтриггера, а инверсные выходы первого и второго 8D-TpHrrepOB, являющиеся первым и вторым выходами блока управления, соединены соответственно со -счетным входом Т-триггера и дополнительным счетным входом счетчика импульсов делителя частоты, при этом третий информационный вход второго 8D-тpиггepa является третьим входом блока управления, Источники информации, принятые во внимание при экспертизе 1. Мартынов Е. М. Синхронизация в системах передачи дискретных сообщений, М., Связь, 1972, с. 15-18. 2. Авторское свидетельство СССР № 455497, кл. Н 03 К 25/04, 23.02.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь пачек импульсов | 1983 |

|

SU1150738A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1709269A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1267601A1 |

| Делитель частоты с переменным коеффициентом деления | 1975 |

|

SU538493A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1989 |

|

SU1677870A1 |

| Часовое устройство с полуавтоматической коррекцией | 1988 |

|

SU1670673A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1982 |

|

SU1115239A2 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1661981A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

Авторы

Даты

1981-04-07—Публикация

1979-05-10—Подача