(5) РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное устройство | 1979 |

|

SU809674A1 |

| Многоканальное резервированное устройство | 1981 |

|

SU991628A1 |

| Резервированное устройство | 1991 |

|

SU1785089A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ РЕЗЕРВИРОВАННОЙ С ПОМОЩЬЮ МАЖОРИТАРНЫХ ЭЛЕМЕНТОВ СИСТЕМОЙ | 2013 |

|

RU2568392C2 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Многоканальное резервированное устройство | 1982 |

|

SU1034209A1 |

| Резервированное устройство | 1979 |

|

SU819995A1 |

| Резервированное устройство | 1991 |

|

SU1830575A1 |

| Мажоритарно-резервированное устройство | 1980 |

|

SU1032600A1 |

| Многоканальное резервированное устройство | 1983 |

|

SU1111263A1 |

Изобретение относитсл к автоматике и вычислительной технике, в частности к схемам с резервированием, Известно резервированное устройство, содержащее элемент ИЛИ, блок эталонного напряжения, три канала резервирования, каждый из которых содержит триггер, резервируемый блок, эле менты И и неравнозначности, первые входы которых соединены с выходами соответствующих резервируемых блоков три входа элемента ИЛИ соединены с выходами элемзнтов . Недостатком этого устройства является низкая помехоустойчивость, так как любой импульс-помеха может выключить резервируемый блок из схемы резервирования. Наиболее близким к предлагаемому изобретению является резервированное устройство, содержащее три канала, выходной элемент ИЛИ, мажоритарный элемент и блок эталонного напряжения первый и второй элементы И 2. Недостатком известного устройства является то, что при отказе одного из резервируемых блоков к выходу устройства подключается любой из оставшихся исправными резервируемый блок, а не тот, который из них более помехоустойчив. Это снижает помехоустойчивость целого резервированного устройства. Цель изобретения - повышение помехоустойчивости резервированного устройства, Поставленная цель достигается тем, что в резервированном устройстве, содержащем выходной элемент ИЛИ, блок эталонного напряжения, мажоритарный элемент , первый и второй элементы -И и три канала резервирования ,, каждый из которых срдержит резервируемый блок, выход которого подключен к одному из входов третьего элемента И, выход каждого из которых присоединен ко входу выходного элемента ИЛИ функциональную цепь, состоящую из

последовательно соединенных элемента неравнознамности, другим входом подключенного к выходу мажоритарного

;элемента, блока текущего среднего значения, элемента сравнения, другим входом подключенного к выходу блока эталонного напряжения, элемента И, другим входом подключенного к выходу первого элемента И, линии задержки и триггера, включенную между выходом резервируемого блока и входом первого элемента И, вы)«5д которого соединен с одним из входов второго элемента И, выход которого соединен со входом выходного элемента ИЛИ, а другой .. вход второго элемента И соединен с

выходом мажоритарного элемента,входы которого подключены к выходам резервируемых блоков, в каждом канале устройства введены элемент ИЛИ и компаратор, управляющий вход которого соединен с единичным выходом триггера предыдущего канала, один из информационных входов подключен к выходу блока текущего среднего значения собственного канала, а другой - к выходу упомянутого блока последующего канала, один из выходов компаратора соединен со входом элемента или собственного канала, другой - со входом элемента или последующего канала, причем выход элемента ИЛИ в каждом канале подключен ко второму входу третьего элемента И.

Это позволяет подключить к выходу устройства более помехоустойчивый, из двух оставшихся исправными, резервируемый блок.

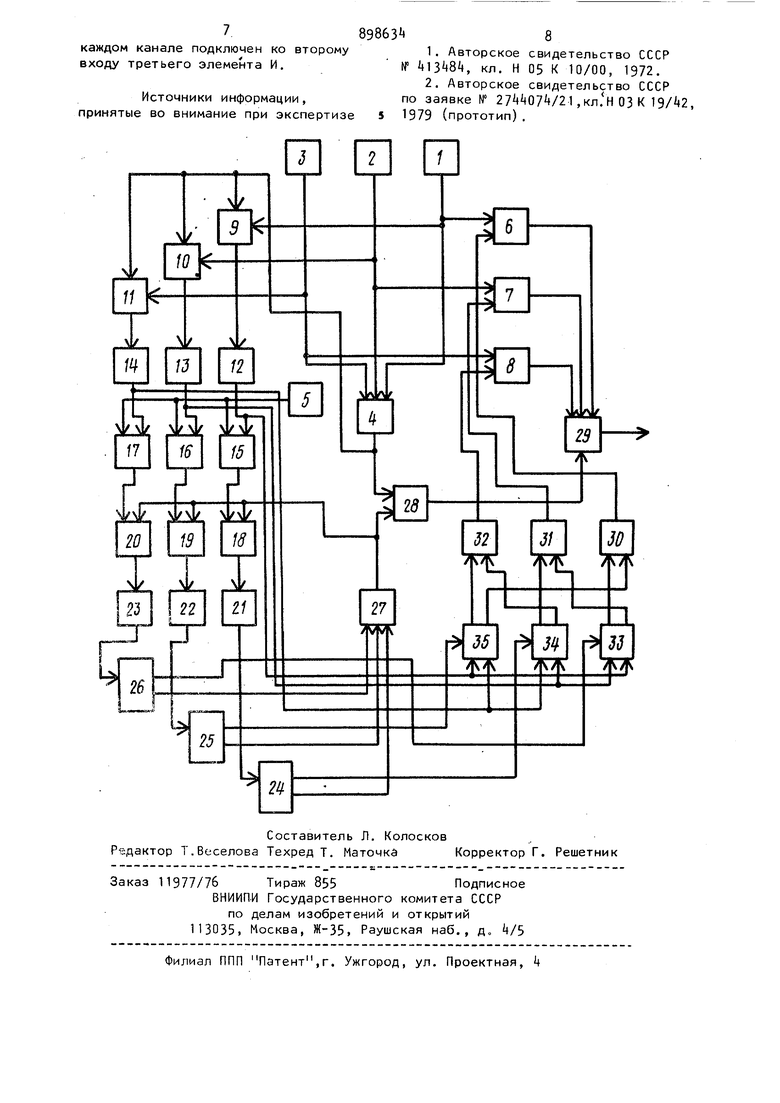

На чертеже представлена блок-схема устройства.

Устройство содержит три резервируемых блока 1-3 выходы которых соединены со входами мажоритарного элемента Ц, блок 5 эталонного напряжения, третьи элементы И 6-8, и функциональНЫ8 цепи, каждая из которых состоит из последовательно соединенных элементов неравнозначности, блоков 12-1 текущего среднего значения,элементоз сравнения , элементов И , линий 21-23 задержки и триггеров . В каждой функциональной цепи вторые входы элементов 9-11 неравнозначности подключены к выходу мажоритарного элемента 4, а вторые входы элементов сравнения 15-17 - к блоку 5 эталонного напряжения. Нулевые выходы триггеров соединены

со входами первого элемента И 27, выход которого подключен к одному из входов второго элемента И 28, а второй вход второго элемента И 28 соединен с выходом мажоритарного элемента k, а выход - ко входу выходного элемента ИЛИ 29, выходы элементов ИЛИ 30-32 в каждом канале подключены сооветственно ко входам третьих элементов И 6-8, Единичный выход триггеров каждого канала подключен к управляющему входу компараторов 33-3 последующего канала, а два информационных входа компараторов 33-35 в каждом канале соединены с выходом блока текущего среднего значения 12-1 собственного канала и с выходом упомянутого блока последующего канала. Один из выходов каждого компаратора соединен со входом каждого элемента ИЛИ 30-32 собственного канала, а другой - со входом каждого элемента ИЛИ 30-32 последующего канала. Выходы второго элемента И 28 и третьих элементов И 6-8 подключены ко входам элемента ИЛИ 29.

Устройство работает следующим образом.

В начальный период работы, пока все резервируемые блоки 1-3 функционируют безотказно (или с редкими случайными сбоями), триггера 2k-26 находятся в исходном нулевом состоянии и элементы И 18-20, 28 находятся в открытом состоянии. Выходные сигналы от резервируемых блоков 1-3 через мажоритарный элемент 4 беспрепятственно проходят элемент И 28, элемент ИЛИ 29 и поступают на выход устройства. При этом мажоритарный элемент эффективно исключает одиночные некоррелированные сбои резервируемых блоков 1-3. Элементы 9-1 неравнозначности в моменты появления сбоев выдают на выход импульсы, однако эти редкие импульсы недостаточны для того, чтобы блоки 12-1 текущего среднего значения накопили потенциал, превышающий потенцил блока 5 эталонного напряжения. Поэтому элементы 15-17 сравнения не срабатывают и устройство продолжает нормально функционировать. При внезапном или параметрическом отказе одного из резервируемых блоков, например блока 1, резко повышается интенсивность ошибок на его выходе, а на выходе элемента неравнозначности 9 появляют5ся выходные импульсы, причем постепенно повышается потенциал на выходе блока 12 текущего среднего значения который в некоторый момент времени превышает потенциал блока 5 эталонного напряжения, в результате чего срабатывает элемент 15 сравнения. Первый импульс с выхода элемента 15 ;сравнения проходит элемент,И 18,заде живается линией 21 задержки и пример но в середине интервала между информационными сигналами переводит триггер 2 в единичное состояние и выходе первого элемента И 27 появляется низкий потенциал, который закры вает элементы И 18-20, т.е. состояние триггеров 24-26 в дальнейшем не может меняться. Закрывается также элемент И 28, прекращая поступление информационных сигналов на выход устройства от мажоритарного элемента k. В тот же момент высокий потенциал с единичного выхода триггера 2 открывает компаратор 3, последний сра нивает выходные сигналы с блоков 13 и 1 текущего среднего значения, и выходной сигнал компаратора 3 появляется на том же выходе, на котором из соответствующих входов потенциал выше. Если в момент сравнения потен{циал на выходе блока 13 текущего сре него значения выше, чем потенциал на выходе блока 14 текущего среднего значения, то соответственно на одном входе компаратора 3 потенциал выше, чем на другом, и выходной сигнал появляется на соответствующем выходе и через элемент ИЛИ 32 поступает на второй вход элемента И 8 и информационные сигналы от заведомо исправного резервируемого блока 3 поступаю на выход устройства. К выходу устрой ства подключается не только заведомо исправный резервируемый блок, но и более помехоустойчивый из оставшихся исправными резервируемых блоков 2 и 3- Так как на выходе блока текущего среднего значения 13 потенциал ;выше, чем на выходе блока 14,значит на выходе резервируемого блока 2 больше ошибочных выходных сигналов, чем на выходе резервируемого блока 3 тем самым резервируемый блок 2 по сравнению с блоком 3 менее помехоустойчив. Поэтому к выходу устройства подключается резервируемый блок 3. Аналогичным образом устройство перестраивается и при отказе любого другого резервируемого блока. + Предложенное устройство по сравнению с известным позволяет повысить помехоустойчивость, так как после отказа одного из резервируемых блоков к выходу устройства подключается не любой из двух оставшихся исправными резервируемый блок, а тот, который более помехоустойчив. Формула изобретения Резервированное устройство, содержащее выходной элемент ИЛИ, блок эталонного напряжения, мажоритарный элемент, первый и второй элементы И и три канала резервирования, каждый из которых содержит резервируемый блок, выход которого подключен к одному из входов третьего элемента И, выход каждого из которых присоединен ко входу выходного элемента ИЛИ, функциональную цепь, состоящую из последовательно соединенных элементов неравнозначности, другим входом подключенного к выходу мажоритарного элемента, блока текущего среднего значения, элемента сравнения, -другим входом подключенного к выходу блока эталонного напряжения, элемента И, другим входом подключенного к выходу первого элемента И, линии задержки и триггера, включенную между выходом резервируемого блока и.входом первого элемента И, выход которого соединен с одним из входов второго элемента И, выход которого соединен со входом выходного элемента ИЛИ, а другой вход второго элемента И соединен с выходом мажоритарного элемента,входы которого подключены к выходам резервируемых блоков, отличающееся тем, что, с целью повышения помехоустойчивости, в каждом канале введены элемент ИЛИ и компаратор, управляющий вход которого соединен с единичным выходом триггера предыдущего канала, один из информационных входов подключен к выходу блока текущего среднего значения собственного канала, а другой - к выходу блока текущего среднего значения последующего канала, один из выходов компаратора соединен со входом элемента ИЛИ собственного канала, другой выход - со входом элемента ИЛИ последующего канала, причем выход элемента ИЛИ в каждом канале подключен ко второму входу третьего элемента И, Источники информации, .J.-- f-..-,,,,,у принятые во внимание при экспертизе 9863 1.Авторское свидетельство СССР № , кл. Н 05 К 10/00, 1972. 2.Авторское свидетельство СССР по заявке № , 03 К , гх IT it/ТП 5 1979 (прототип) .

Авторы

Даты

1982-01-15—Публикация

1980-05-21—Подача