(54) ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель задержки | 1980 |

|

SU930219A2 |

| Цифровой измеритель задержки | 1981 |

|

SU951228A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

| Цифровой измеритель частоты заполнения радиоимпульсов | 1982 |

|

SU1161892A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Цифровой измеритель частоты | 1982 |

|

SU1095089A1 |

| Устройство для цифрового логарифмического преобразования степенных функций времени | 1983 |

|

SU1160406A1 |

| Устройство для распознавания изображений | 1985 |

|

SU1339601A1 |

1- Изобретение относится к радиоизмерениям, в частности к устройствам измерения времени задержки между дву мя узкополосными сигналами, и может быть использовано в радиолокации и гидролокации, а также технике тракторных измерений. Известно устройство для измерения времени запаздывания между двумя сигналами,содержащее многоотводный элемент задержки, М умножителей, под ключенных первыми входами к М отводам-элемента задержки, вторые выходы всех М умножителей объединены, М интеграторов , входы которых подключены к выходам умножителей, а также блок обнаружения, входы которого соединены с соответствующими выходами интеграторов, исследуемые сигналы подаются на вход многоотводного элемента задёржки и на объединенные М входов умножителей. Указанное устройство фор мирует в каждом своём канале дискретные отсчеты корреляционного интеграла, расчитанные для набора фиксированных значений задержек (шаг дискретности, определяется временным интервалом между соседними отводами элемента задержки). Блок обнаружения путем сравнения отсчетов корреляционного интеграла находит наиб;ольший из них и таким образом формирует на своем выходе грубую оценку задержки. Достоинством данного устройстваявляется возможность параллельного ов- зора всего априорного диапазона возможных значений задержки, что обеспечивает получение оценок в реальном масштабе времени l . .. Недостатки измерителя задержки - . большой аппаратурный объем; низкая точность измерений, так как задержка оценивается с точностью до дискреты (временного расстояния между отводами линии задержки). Наиболее близким техническим решением к изобретению является цифровой измеритель задержки, содержащий последовательно соединенные триггер, первый ключ, счетчик,устройство индикации, а также синхронизатор, причем первый выход синхронизатора подключен ко второму управляющему входу первого ключа, второй выход синхронизатора подключен к управлякяаему входу устройства индикации, установочиые, входы триггера соединены с выходами формирователей, входы которых являются сигнальными входами устройства измерения задержки. Достоинствами

стройства являются -малый аппаратурый объем; высокое быстродействие и остаточно высокая при значительном ревнииении сигнала над помехой точность измерения 2.

Недостаток данного измерителя езкое ухудшение точностей измерений и омещенке оценок задержки при низких тношениях сигнал/шум, когда имеют есто аномальные ошибки регистрации нуль (пересечений) моментов перехода фронтов напряжений ограниченных сигналов через нулевой уровень напряжения.

Цель изобретения - повышение помехоустойчивости цифрового измерителя задержки.

Поставленная цель достигается тем, что в устройство, содержащее последовательно соединенные триггер, первый ключ и счетчик, а также синхронизатор и устройство индикации и элемент ИЛИ, причем первый вход синхронизатора подключен к управляющему входу первого ключа, установочные входы триггера соединены с выходами формирователей) входы которых подключены к сигнальным шинам, введены две идентичные цепочки из последовательно соединенных первых постоянных запоминающих устройств(ПЗУ), накапливающих сумматоров и вторых ключей, а также третий ключ, делитель и второе ПЗУ, причем входы обеих цепочек объединены и через третий ключ соединены с -информационным выходом счетчика, выходы цепочек через последовательно соединенные делитель и второе ПЗУ подключены к устройству индикации, причем выходы третьего ключа через элемент ИЛИ подключен к установочному входу счетчика, второй выход синхронизатора соединен с объединенными управляющими входами . вторых ключей, управляю..щий вход третьего ключа подключен к инверсному выходу триггера, а установочные входы накапливающих сумматоров соединены с третьим выходом синхронизатора.

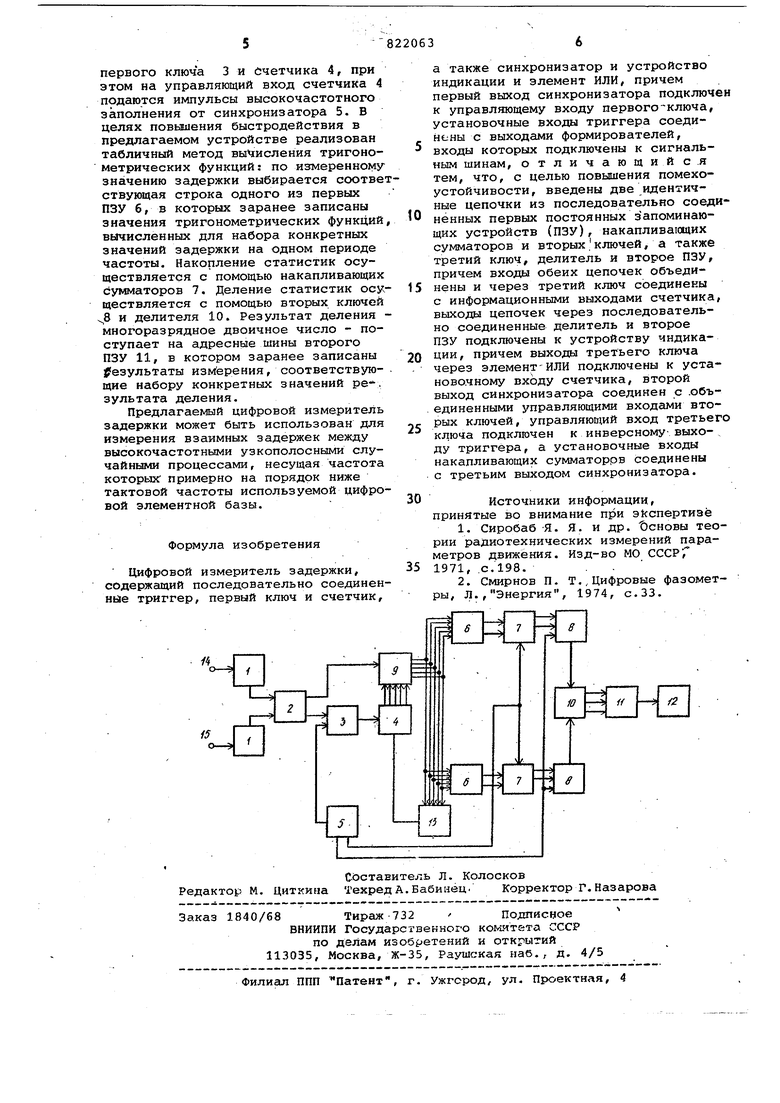

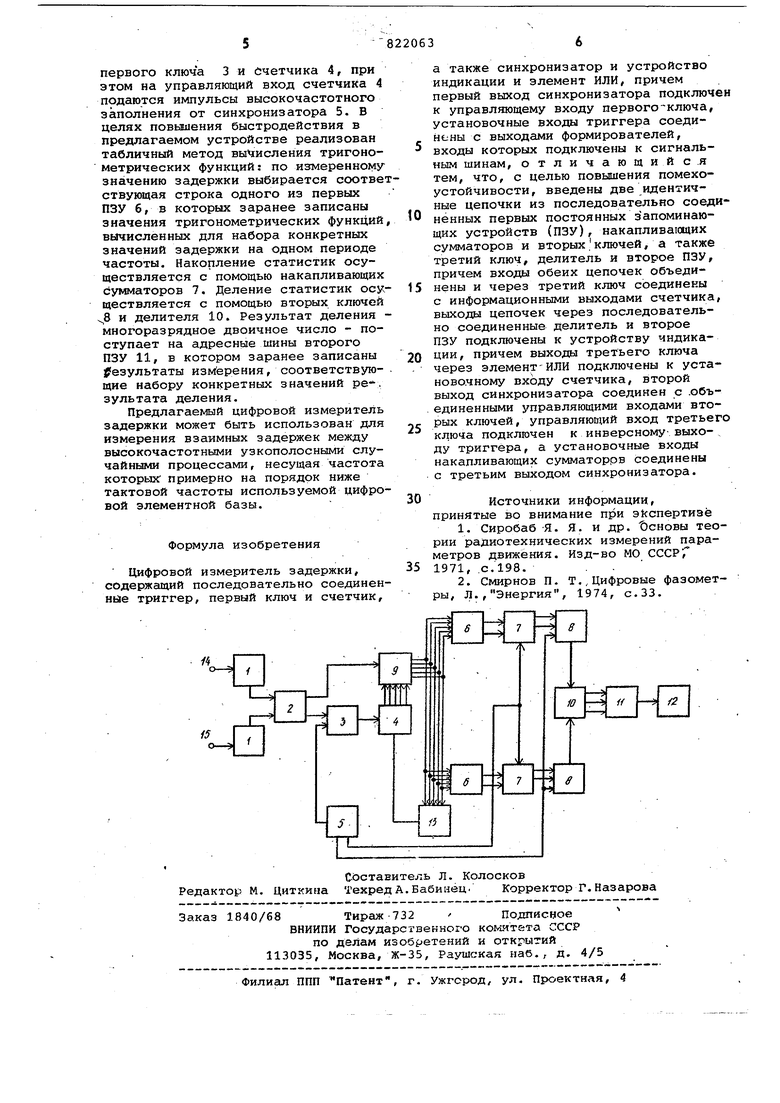

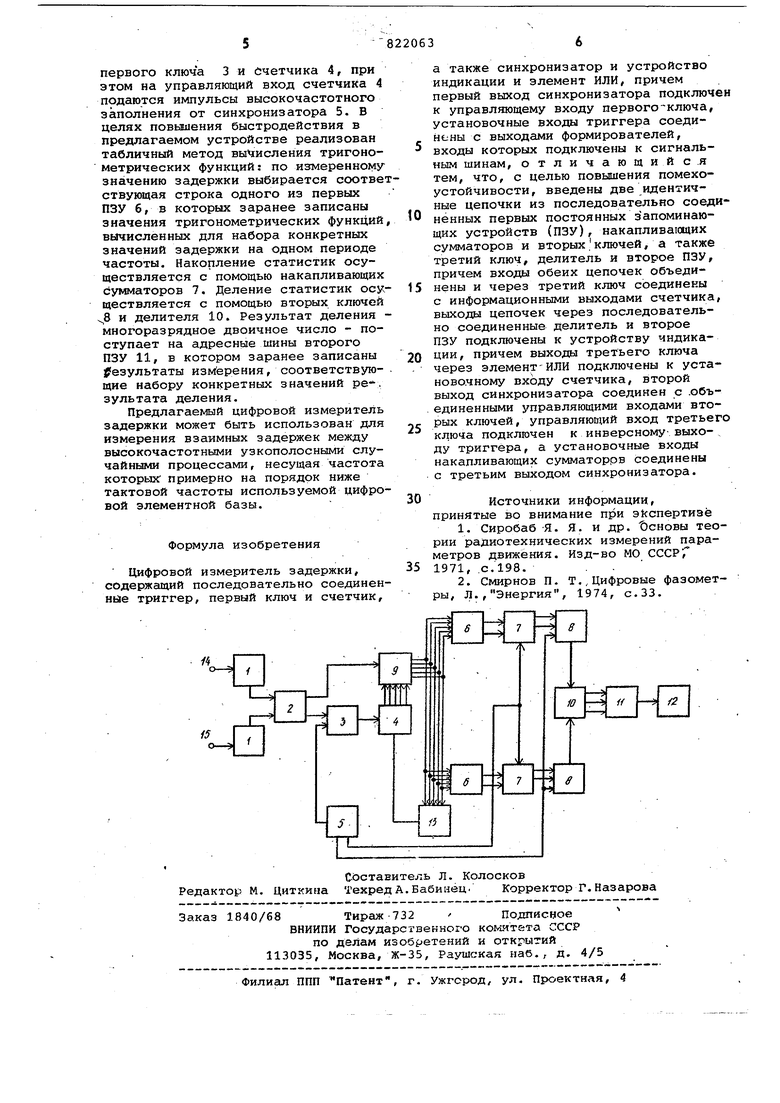

На чертеже представлена структурная схема цифрового измерителя задержки.

Цифровой измеритель задержки содержит формирователь 1, триггер 2, первый ключ 3, счетчик 4, синхронизатор 5, .первые ПЗУ б, накапливающие сумматоры 7, вторые ключи 8, третий ключ 9, делитель 10, вторые ПЗУ 11, устройство 12 индикации, элемент ИЛИ 13, при этом установочные входы триггера 2 подсоединены к выходам формирователей, входы 14 и 15 являются сигнальными входами цифрового измерителя задержки, к управляющему входу первого -ключа 3 подключен первый выход синхронизатора 5, выходы первых ПЗУ б через накапливающие сумматоры 7 и вторые ключи 8 соединены с делителем Ю, выход которого через второе ПЗУ 11 подключен к устройству 12 индикации, выходы , третьего ключа 9 через элемент ИЛИ il3 подключены к установочному входу счетчика 4, второй вход синхронизатора 5 соединен с объединенными управляющими входами вторых ключей 8, управляющий вход третьего ключа 9 подключен к инверсному выходу триггера 2, а установочный вход накапливающих сумматоров 7 соединен с третьим выходом синхронизатора 5.

Устройство работает следующим образом.

Сигналы, взаимную задержку между которыми необходимо измерить, подаются на входе 14 и 15 формирователей 1. Фронты прямоугольных напряя(:ений, сформированных из входных сигналов, опрокидывают триггер 2. На прямрм выходе триггера 2 формируются импульсы положительной полярности, длительность которых равна временному расстоянию между-соседними (последующими) нуль-пересечениями двух узкополосных сигнгшов. Эти импульсы, поступая на вход первого ключа 3, разрешают прохождение импульсов высокочастотного заполнения, вырабатываемых синхронизатором 5, в счетчик 4. Таким образом происходит измерение длительности положительного импульса на прямом выходе триггера 2.

В момент переворота триггера 2 третий ключ 9 открывается управляющим сигналом с инверсного выхода триггера 2, и число, записанное в счетчике 4, поступает на объединенные адресные шины первых ПЗУ б. В это же время происходит установка в нулевое состояние счетчика 4 под воздействием положительного импульса с выхода элемента ИЛИ 13, входы которого объединены со входами первых ПЗУ 6. Числа, считываемые с выходов первых ПЗУ 6, поступают в накапливающие сумматоры 7, где происходит их сложение с содержимым сумматоров. В течение . интервала наблюдения в сумматорах 7 накапливаются статистики, достаточные для однозначного измерения времени задержки между узкопоЛосньами сигналами.

После окончания интервала наблюдения на управляющие входы вторых ключей 8 подается сигнал от синхронизатора 5, в результате чего числа, накопленные в сумматорах 7, поступают на входы делителя 10. Результат деления, воздействуя на адресные шины второго ПЗУ 11, обуславливает выборку числа из соответствующей его строки. Данное число, являющееся результатом измерения, поступает на устройство 12 индикации.

Измерение задержки между ближайшими нуль-пересечениями организуется с помощью формирователей 1 и последовательно соединенных триггера 2,

первого ключа 3 и Счетчика 4, при этом на управляющий вход счетчика 4 подаются импульсы высокочастотного заполнения от синхронизатора 5. В целях повьшения быстродействия в предлагаемом устройстве реализован табличный метод вычисления тригонометрических функций: по измеренному значению задержки выбирается соотвествующая строка одного из первых ПЗУ б, в которых заранее записаны значения тригонометрических функций вычисленных для набора конкретных значений задержки на одном периоде частоты. Накопление статистик осуществляется с помощью накапливающих сумматоров 7, Деление статистик осуществляется с помощью вторых ключей х,8 и делителя 10. Результат деления многоразрядное двоичное число - поступает на адресные шины второго ПЗУ 11, в котором заранее записаны результаты измерения, соответствующие набору конкретных значений ре. зультата деления.

Предлагаемый цифровой измеритель задержки может быть использован для измерения взаимных задержек между высокочастотными узкополосными случайными процессами, несущая частота которых примерно на порядок ниже тактовой частоты используемой цифровой элементной базы.

Формула изобретения

Цифровой измеритель задержки, содержащий последовательно соединенные триггер, первый ключ и счетчик.

а также синхронизатор и устройство индикации и элемент ИЛИ, причем первый выход синхронизатора подключен к управляющему входу первого-ключа, установочные входал триггера соединены с выходами формирователей, входы которых подключены к сигнальным шинам, отличающийся тем, что, с целью повышения помехоустойчивости, введены две идентичные цепочки из последовательно соеди0ненных первых постоянных запоминающих устройств (ПЗУ), накапливающих сумматоров и вторыхключей, а также третий ключ, делитель и второе ПЗУ, причем входы обеих цепочек объеди5нены и через третий ключ соединены с информационными выходами счетчика, выходы цепочек через последовательно соединенные делитель и второе ПЗУ подключены к устройству индикации, причем выходы третьего ключа

0 через элементИЛИ подключены к установочному входу счетчика, второй выход синхронизатора соединен с .объединенными управляющими входами вторых ключей, управляющий вход третьего

5 ключа подключен к инверсному- выходу триггера, а установочные входы накапливающих сумматоррв соединены с третьим выходом синхронизатора.

0

Источники информации, принятые во внимание при 3kcnepTHae

5 1971, .С.198. . .

Авторы

Даты

1981-04-15—Публикация

1979-05-10—Подача