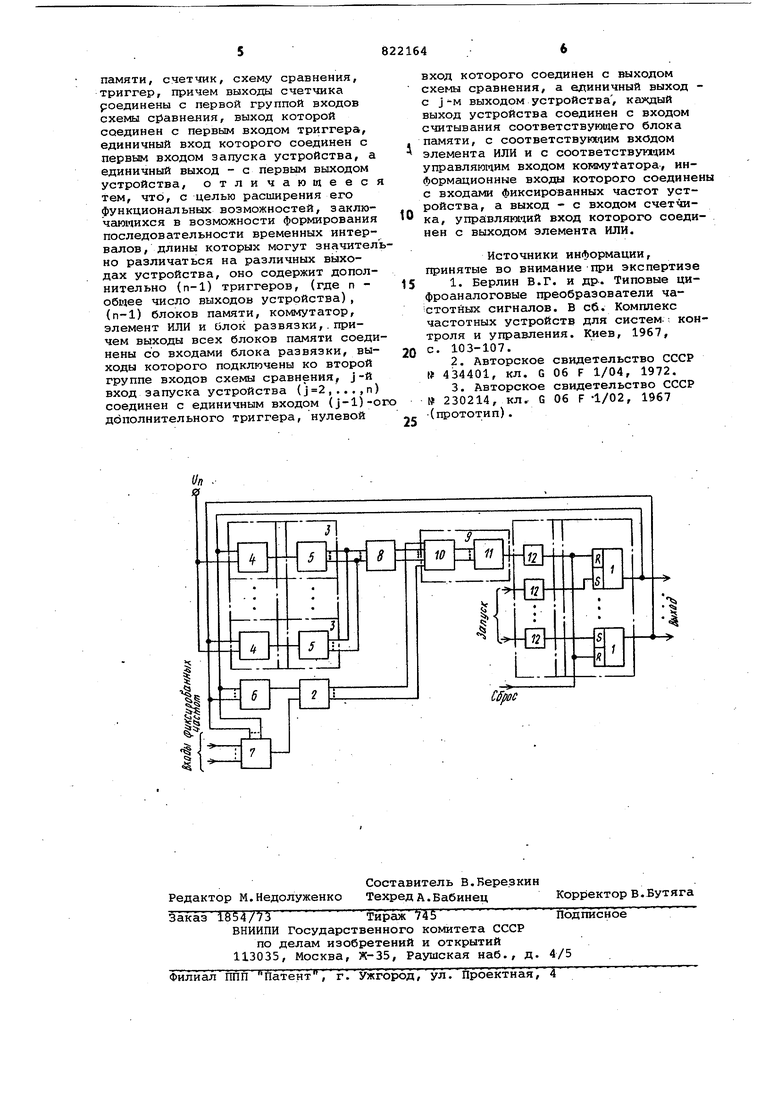

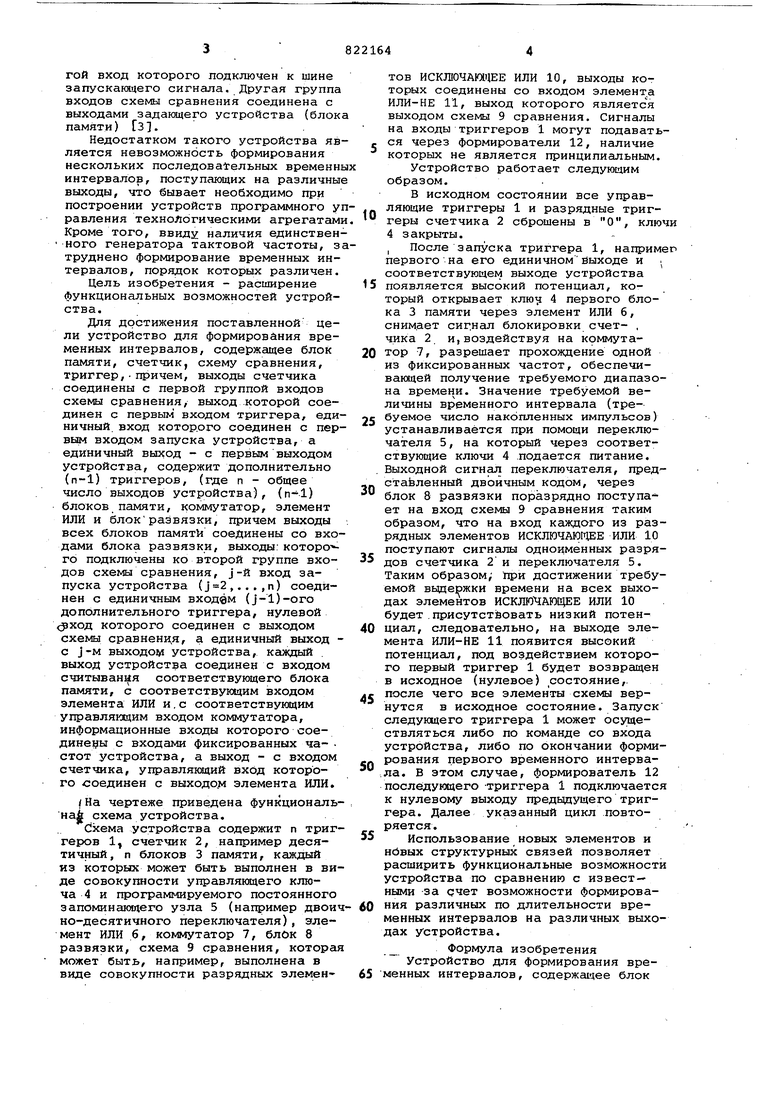

Изобретение относй1тся к автоматике и может найти применение при поостроении систем программного и логического управления, когда возникает необходимость формирования последовательности управляющих временных команд для исполнительных устройств одной технологической цепи, причем длительности команд могут отличаться друг от друга на одни или несколько порядков. Кроме того, устройство может, использоваться для подсчета и выдачи сигналов при дости жении заданного количества импульсов, что позволяет производить до- . задювку материала или изделий по заДс)нной программе, . известны устройства формирования временных интервалов,основанные на использовании цифровых схе( и содержащие счетчик, соединенный через дешифраторы с входами управляющих триг геров fl. Недостатком таких устройств является то, что для получения последовательности временных команд необх димо использовать несколько таких устройств, что значительно увеличивает аппаратурные затраты. Известно устройство для формирования временных интервалов, содержащее управляющие триггеры, счетчик, элементы ИЛИ, дешифратор и коммутатор, адресные шины которого соединены с единичными выходами управляющих триггеров и вход(ами элемента ИЛИ, выход которого соединен с нулевым установочным входом счетчика, счетный вход которого соединен с выходом коммутатора, информационные шины которого соединены с источником фиксированных частот 2. Недостатками этого устройства являются: ограниченные функциональные возможности, т,е. оно работает по.жесткой программе, для изменения которой необходима перепайка выводов дешифратора, а также низкая помехоустойчивость. Наиболее близким к предлагаемому является устройство для формирования временных интервалов, содержащее счетчик, на вход которого подается частота с генератора тактовых импульсов, выходы счетчика подключены к первой группе входов схемы сравнения, выход которой подключен к одному из входов триггера, другой вход которого подключен к шине запускающего сигнала. Другая групп входов схемы сравнения соединена с выходами задаклцего устройства (бло памяти) З1. Недостатком такого устройства я ляется невозможность формирования нескольких последовательных времен интервалов, поступающих на различны выходы, что бывает необходимо при построении устройств программного у равления технологическими агрегатам Кроме того, ввиду наличия единствен ного генератора тактовой частоты, труднено формирование временных ин тервалов, порядок которых различен Цель изобретения - расширение функциональных возможностей устрой ства. Для достижения поставленной це ли устройство для формирования вре менных интервалов, содержащее блок памяти, счетчик, схему сравнения, триггер,причем, выходы счетчика соединены с первой группой входов схемы сравнения, выход которой соединен с первым входом триггера, еди ничный, вход которого соединен с пер вым входом запуска устройства, а единичный выход - с первым выходом устройства, содержит дополнительно (п-1) триггеров, (где п - общее число выходов устройства), (п-1) блоков памяти, коммутатор, элемент ИЛИ и блокразвязки, причем выходы всех блоков памяти соединены со вхо дами блока развязки, выходы: которого подключены ко второй группе входов схемы сравнения, j-и вход запуска устройства (,...,n) соединен с единичным входам (j-l)-oro дополнительного триггера, нулевой 3зход которого соединен с выходом схемы сравнени,я, а единичный выход с J-M выходом устройства, кг1ждый выход устройства соединен с входом считывания соответствующего блока памяти, с соответствующим входом элемента ИЛИ и,с соответствующим управляющим входом коммутатора, информационные входы которого соединецы с входами фиксированных частот устройства, а выход - с входом счетчика, управляклций вхсэд которого соединен с выходом элемента ИЛИ. /На чертеже приведена функциональ на схема устройства. Схема устройства содержит п триг геров 1, счетчик 2, например десятичный, п блоков 3 памяти, каждый из которых может быть выполнен в ви де совокупности управляющего ключа 4 и программируемого постоянного запоминающего узла 5 (например двои НС-десятичного переключателя), элемент ИЛИ 6, коммутатор 7, блок 8 развязки, схема 9 сравнения, котора может быть, например, выполнена в виде совокупности разрядных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10, выходы которых соединены со входом элемента ИЛИ-НЕ 11, выход которого являетс я выходом схемы 9 сравнения. Сигналы на входы триггеров 1 могут подаваться через формирователи 12, наличие которых не является принципиальным. Устройство работает следующим образом. В исходном состоянии все управляющие триггеры 1 и разрядные триггеры счетчика 2 сброшены в О, ключи 4 3 акрыты. I После запуска триггера 1, например первого на его единичномбыходе и . соответствующем выходе устройства появляется высокий потенциал, который открывает клю 4 первого блока 3 памяти через элемент ИЛИ 6, снимает сиг.нал блокировки счет- , чика 2 и,воздействуя на коммутатор 7, разрешает прохождение одной из фиксированных частот, обеспечивак«дей получение требуемого диапазона временен. Значение требуемой величины временного интервала (требуемое число накопленных импульсов) устанавливается при помощи переключателя 5, на который через соответствующие ключи 4 .подается питание. Выходной сигнал переключателя, представленный двоичным кодом, через блок 8 развязки поразрядно поступа ет на вход схемы 9 сравнения таким образом, что на вход каждого из разрядных элементов ИСКЛЮЧАЮГтЩЕ ИЛИ 10 поступают сигналы одноименных разрядов счетчика 2 и переключателя 5. Таким образом,- йри достижении требуемой выдержки времени на всех выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 будет.присутствовать низкий потенциал, следовательно, на выходе элемента ИЛИ-НЕ 11 появится высокий потенциал, под воздействием которого первый триггер 1 будет возвращен в исходное (нулевое) состояние,, после чего все элементы схемы вернутся в исходное состояние. Запуск следующего триггера 1 может осуществляться либо по команде со входа устройства, либо по окончании формирования первого временного интервала. В этом случае, формирователь 12 последующего -триггера 1 подключается к нулевому выходу предыдущего триггера. Далее указанный цикл повторяется. Использование новых элементов и нЬвых структурных связей позволяет расширить функциональные возможности устройства по сравнению с известными -за счет возможности формирования различных по длительности временных интервалов на различных выходах устройства. Формула изобретения Устройство для формирования временных интервалов, содержардее блок

памяти, счетчик, схему сравнения, триггер, причем выходы счетчика роединены с первой группой входов схемы сравнения, выход которой соединен с первым входом триггера, единичный вход которого соединен с первым входом запуска устройства, а единичный выход - с первым выходом устройства, отличающееся тем, что, с целью расширения его функциональных возможностей, эаключсцомихся в возможности формирования последовательности временных интервалов, длины которых могут значительно различаться на различных выходах устройства, оно содержит дополнительно (п-1) триггеров, (где п общее число выходов устройства), (п-1) блоков памяти, коммутатор, элемент ИЛИ и блок развязки,.причем выходы всех блоков памяти соединены со входами блока развязки, выходы которого подключены ко второй группе входов схемы сравнения, j-и вход запуска устройства (,...,n) соединен с единичным входом (j-l)-or дополнительного триггера, нулевой

вход которого соединен с выходом схемы сравнения, а единичный выход с j м выходом устройства , каждый выход устройства соединен с входом считывания соответствующего блока памяти, с соответствующим входом элемента ИЛИ и с соответствууадим управляющим входом коммутатора, информационные входы которого соединены с входами фиксированных частот устройства, а выход - с входом счетчи0ка, управляю1чий вход которого соединен с выходом элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Берлин В.Г. и др. Типовые ци5фроаналогоБые преобразователи частотных сигналов. В сб. Комплекс частотных устройств для систем-; контроля и управления. Киев, 1967,

с. 103-107.

0

2.Авторское свидетельство СССР № 434401, кл. G 06 F 1/04, 1972.

3.Авторское свидетельство СССР 230214, кл. G 06 F -1/02, 1967 (прототип).

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования временных интервалов | 1984 |

|

SU1195430A2 |

| Устройство для преобразования полярных координат вектора в прямоугольные | 1978 |

|

SU771682A1 |

| Преобразователь полярных координат вектора в прямоугольные | 1976 |

|

SU596955A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| АДАПТИВНЫЙ ЭЛЕКТРОСТИМУЛЯТОР С ВИРТУАЛЬНЫМ ЭЛЕКТРОДОМ | 2000 |

|

RU2198695C2 |

| Устройство для управления с контролем | 1983 |

|

SU1156074A1 |

| Устройство для регистрации команд в резервированной системе управления | 1989 |

|

SU1633284A1 |

| Задающее устройство для цифрового следящего привода | 1986 |

|

SU1411709A1 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1554115A1 |

| Генератор нестационарного случайного импульсного процесса | 1987 |

|

SU1587501A1 |

Авторы

Даты

1981-04-15—Публикация

1978-02-21—Подача