1

Изобретение относится к вычислительной технике, где оно может быть использовано для соответствующего кодопреобразования, а также в арифметических устройствах, обеспечивающих обработку как двоичных, так и двоично-десятичных операндов.

Известны преобразователи двоично-десятичного кода в двоичный 1, 2. Один из них 1 содержит динамический регистр, регистр тетрады, сумматор, вентили и элемент «ИЛИ, причем выход динамического регистра соединен через вентиль и элемент «ИЛИ со входом сумматора и через вентиль - со входом третьего разряда регистра тетрады, выходы первого и третьего разрядов которого соединены через вентили со входами сумматора, SL выход последнего соединен со входом динамического регистра. Это известное устройство характеризуется сложностью и значительным временем преобразования. Прототипом изобретения является устройство 2, содержащее элемент переноса, регистр результата и в каждой тетрада преобразуемого числа дещифратор и сумматор-сдвигатель, к первым входам которых подключен генератор тактовых сигналов. Это устройство обеспечивает преобразование п-разрядного двоично-десятичного кода в двоичный в процессе выполнения 4п тактов сдвигов - суммирования. Однако оно

требует значительного времени, затрачиваемого на преобразование.

Целью изобретения является сокращение времени преобразования. В описываемом преобразователе это достигается тем, что в нем первый выход сумматора-сдвнгателя каждой тетрады подключен к первому входу дешифратора данной тетрады, второй выход сумматора-сдвигателя каждой тетрады подключен

ко второму входу соответствующего дешифратора л к третьему входу дешифратора соседней младшей тетрады, первый, второй, третий, четвертый и нятый выходы дешифратора каждой тетрады, кроме тетрады единиц, подключены к первому, второму, третьему, четвертому и пятому входам сумматора - сдвигателя младшей тетрады, первый выход дешифратора тетрады единиц подключен ко входу элемента переноса, выход которого соединен с четвертым входом соответствующего дешифратора, второй и третий выходы дешифратора тетрады единиц подключены к первому и второму входу регистра результата, выход которого соединен с выходом устройства.

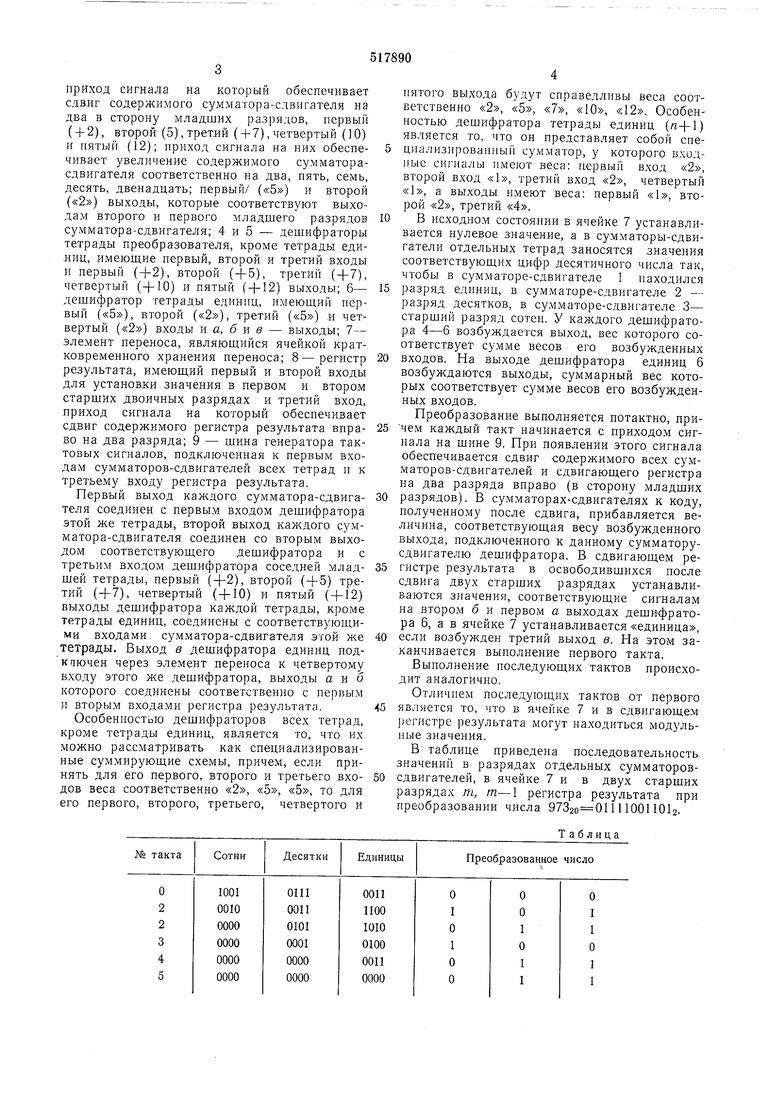

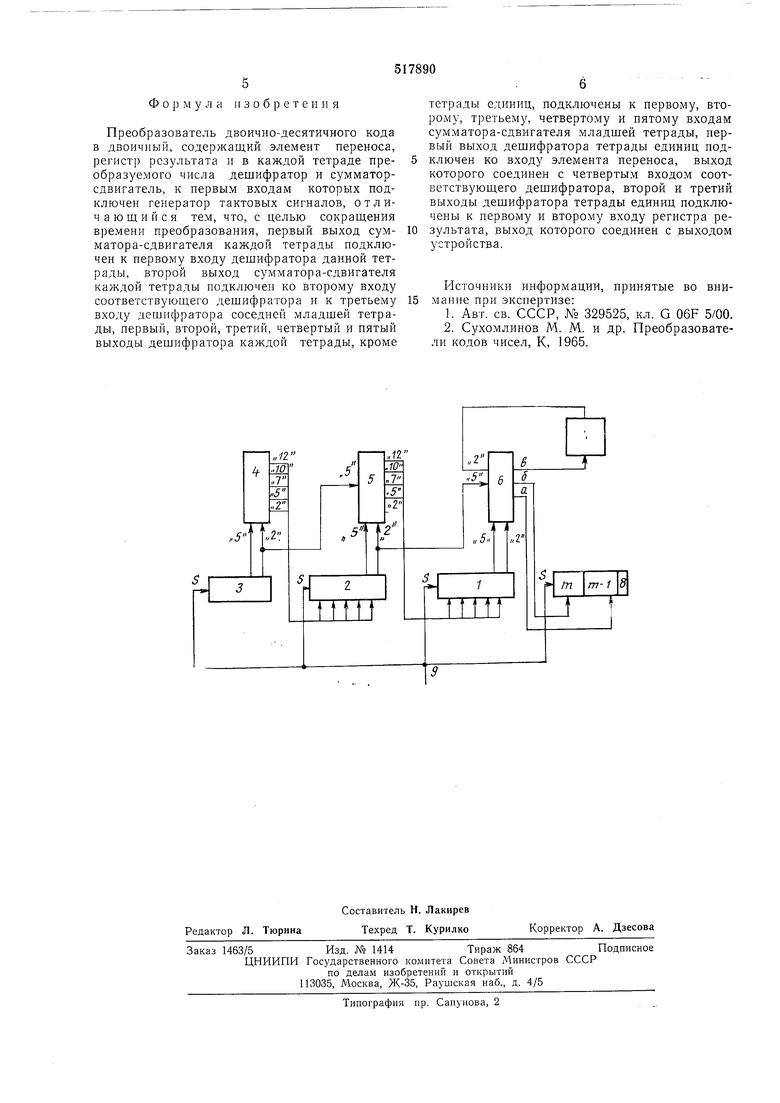

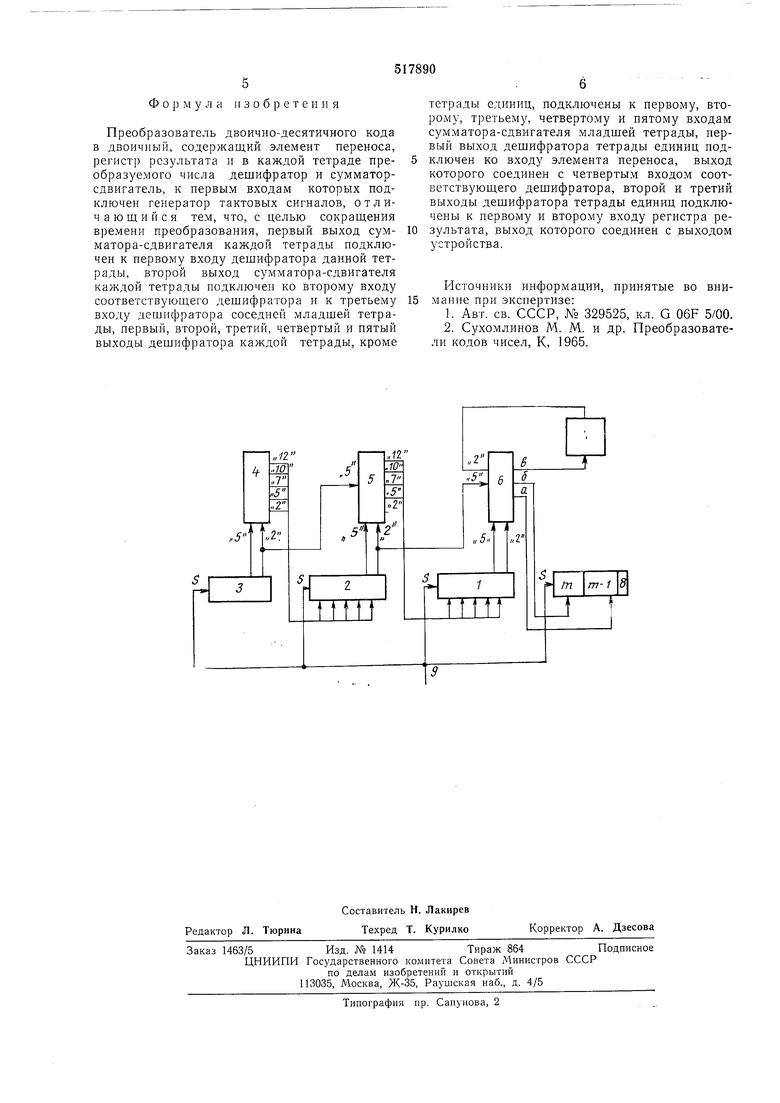

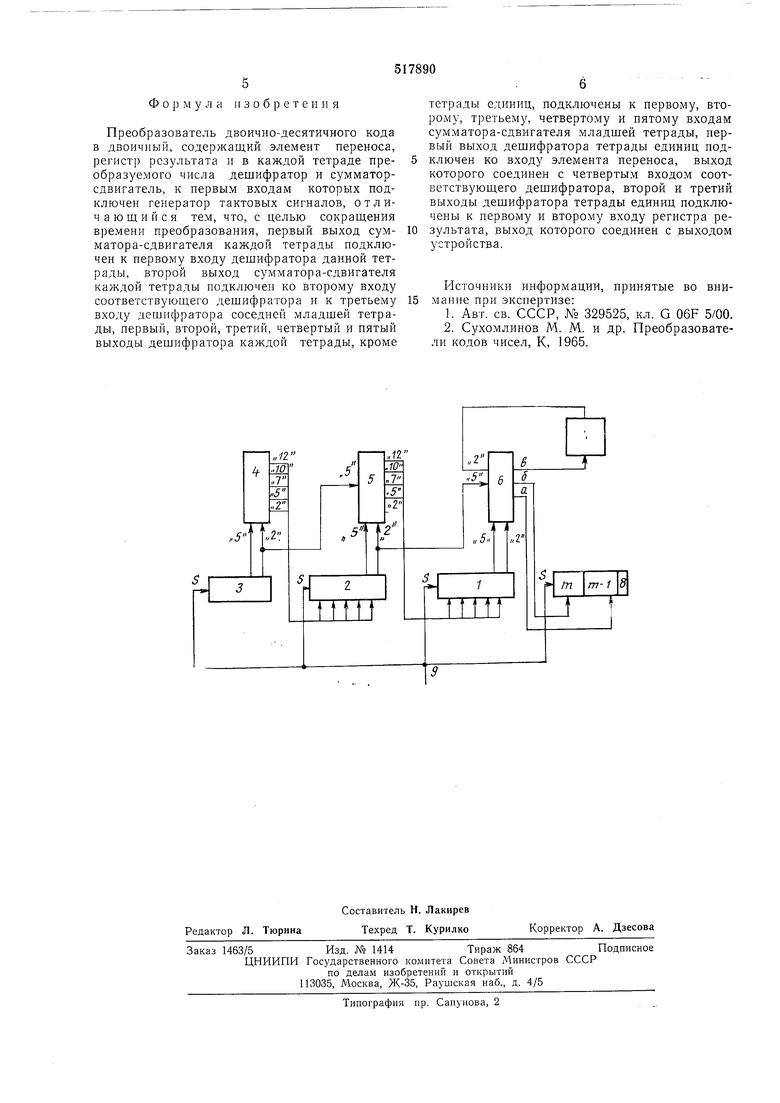

На чертеже приведена схема описываемого преобразователя для 3-разрядных (п-3) десятичных чисел. На чертеже: 1, 2 и 3 - сумматоры-сдвигатели, обеспечивающие фиксацию десятичных цифр исходного числа; каждый из них имеет первый вход (вход S), приход сигнала на который обеспечивает сдвиг сОл ержимого сумматора-сдвигателя на два в сторону младших разрядов, первый ( + 2), второй (5),третий ( + 7), четвертый (10) и пятый (12); приход сигнала на них обеспечивает увеличение содержимого сумматорасдвигателя соответственно на два, пять, семь, десять, двенадцать; первый/ («5) и второй («2) выходы, которые соответствуют выходам второго и первого младшего разрядов сумматора-сдвигателя; 4 и 5 - дешифраторы тетрады преобразователя, кроме тетрады единиц, имеющие первый, второй и третий входы и первый (+2), второй (+5), третий (+7), четвертый ( + 10) и пятый () выходы; 6- дешифратор тетрады единиц, имеющий первый («5), второй («2), третий («5) ,и четвертый («2) входы и а, б и 0 - выходы; 7- элемент переноса, являющийся ячейкой кратковременного хранения переноса; 8-регистр результата, имеющий первый и второй входы для установки значения в первом и втором старших двоичных разрядах и третий вход, приход сигнала на который обеснечивает сдвиг содержимого регистра результата вправо на два разряда; 9 - шина генератора тактовых сигналов, подключенная к первым входам сумматоров-сдвигателей всех тетрад и к третьему входу регистра результата. Первый выход каждого сумматора-сдвигателя соединен с первым входом дешифратора этой же тетрады, второй выход каждого сумматора-сдвигателя соединен со вторым выходом соответствующего дешифратора и с третьим входом дешифратора соседней младшей тетрады, первый (+2), второй (+5) третий (+7), четвертый ( + 10) и пятый ( + 12) выходы дешифратора каждой тетрады, кроме тетрады единиц, соединены с соответствующими входами сумматора-сдвигателя этой же тетрады. Выход в дешифратора единиц нодкоючен через элемент переноса к четвертому входу этого же дещифратора, выходы а и б которого соединены соответственно с первым и вторым входами регистра результата. Особенностью дешифраторов всех тетрад, кроме тетрады единиц, является то, что их можно рассматривать как специализированные суммирующие схемы, причем, если принять для его первого, второго и третьего входов веса соответственно «2, «5, «5, то для его первого, второго, третьего, четвертого и пятого выхода будут справедливы веса соответственно «2, «5, «7, «10, «12. Особенностью дешифратора тетрады единиц («+) является то, что он представляет собой специализированный сумматор, у которого входные сигналы имеют веса: первый вход «2, второй вход «1, третий вход «2, четвертый «1, а выходы имеют веса: первый «1, второй «2, третий «4. В исходном состоянии в ячейке 7 устанавливается нулевое значение, а в сумматоры-сдвигатели отдельных тетрад заносятся значения соответствующих цифр десятичного числа так, чтобы в сумматоре-сдвигателе 1 находился разряд единиц, в сумматоре-сдвигателе 2 - разряд десятков, в сумматоре-сдвигателе 3- старший разряд сотен. У каждого дешифратора 4-6 возбуждается выход, вес которого соответствует сумме весов его возбужденных входов. На выходе дешифратора единиц 6 возбуждаются выходы, суммарный вес которых соответствует сумме весов его возбужденных входов. Преобразование выполняется потактно, каждый такт начинается е приходом сигнала на шине 9. При появлении этого сигнала обеспечивается сдвиг содержимого всех сумматоров-сдвигателей и сдвигающего регистра на два разряда вправо (в сторону младших разрядов). В сумматорах-сдвигателях к коду, иолученному после сдвига, прибавляется величина, соответствующая весу возбужденного выхода, подключенного к данному сумматорусдвигателю дешифратора. В сдвигающем регистре результата в освободившихся носле сдвига двух старщих разрядах устанавливаются значения, соответствующие сигналам на втором б и первом а выходах дешифратора 6, а в ячейке 7 устанавливается «единица, если возбужден третий выход в. На этом заканчивается выполнение первого такта. Выполнение последующих тактов происходит аналогично. Отличием последующих тактов от первого является то, что в ячейке 7 и в сдвигающем )егистре результата могут находиться модульные значения. В таблице приведена последовательность значений в разрядах отдельных сумматоровсдвигателей, в ячейке 7 и в двух старших разрядах т, т-1 регистра результата при преобразовании числа 97320 011110011012. Таблица

Формула п 3 о б р е т е и и я

Преобразователь двоично-десятичного кода в двоичный, содержащий элемент переноса, регистр результата и в каждой тетраде преобразуемого числа дешифратор и сумматорсдвигатель, к первым входам которых подключен генератор тактовых сигналов, отличающийся тем, что, с целью сокращения времени преобразования, первый выход сумматора-сдвигателя каждой тетрады подключен к первому входу дещифратора данной тетрады, второй выход сумматора-сдвигателя каждой тетрады подключен ко второму входу соответствующего дешифратора п к третьему входу дешифратора соседней младшей тетра ды, первый, второй, третий, четвертый и пятый выходы дешифратора каждой тетрады, кроме

тетрады единиц, подключены к первому, второму, третьему, четвертому и пятому входам сумматора-сдвигателя младшей тетрады, первый выход дешифратора тетрады единиц подключей ко входу элемента переноса, выход которого соединен с четвертым входом соответствующего дешифратора, второй и третий выходы дещифратора тетрады единиц подключены к первому и второму входу регистра результата, выход которого соединен с выходом устройства.

Источники информации, принятые во внимание при экспертизе:

1.Авт. св. СССР, № 329525, кл. G 06F 5/00.

2.Сухомлинов М. М. и др. Преобразователи кодов чисел. К, 1965.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

Авторы

Даты

1976-06-15—Публикация

1973-12-12—Подача