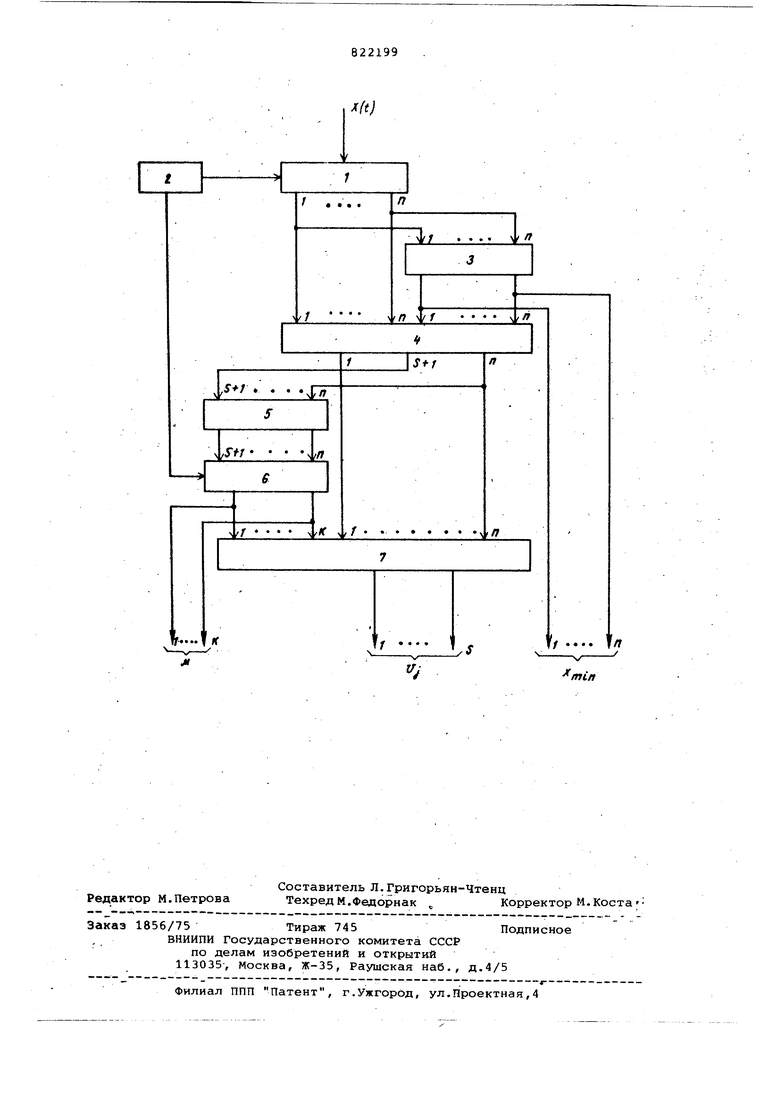

Изобретение относится к специализированным средствам вычислительной техники и предназначено для сокргидения избыточности при кодировании ста ционарных случайных rfpoueccoB. Для оптимального кодирования случайных :процессов с заранее неизвестными.областями изменения их значений исполь зуют устройства адаптивного кодирова ния. В этих устройствах число уровне квантования выбирается в соответстви с требуемой точностью независимо от диапазона входного случайного процес са. ЭтоПозволяет сократить избыточ-ность Б результате кодирования,. сохранить постоянство приведенной погрешности квантования при изменении диапазона флуктуации процессов в широки с пределах,сократить аппаратурные и временные затраты на дальнейшую статистическую обработку (определение корреляционной функции,плотности распределения и т.п.). Известно устройство адаптивного ко дирования с прогнозированием,с самонастройкой параметров по статистическим оценкам математического ожида ния l3 . Наиболее близким к предлагаемому по технической сущности является уст ройство для адаптивного кодирования стационарных случайных процессов,содержащее сумматор,первая группа входор которого объединена с соответст вyющиг ш входами блока оценки минимума и подключена к выходам аналого-цифрового преобразователя,информационный вход которого является входом устройства, управляквдий вход аналогоцифрового преобразователя соединен с первым в лxoдoм блока управления, второй выход которого подключен к управляющему входу блока изменения масштаба, выходы которого соединены с управляющими входами коммутатора и являются первой группой выходов устройства, информационные входы коммутатора подключены к соответствующим выходам сумматора,вторая группа входов которого соединена с соответствующими выходами блока оценки минимума и является второй группой выходов устройства L2J . Недостатком данного устрЪйства является аппаратурная сложность, связанная с тем,что для определения диапазона флуктуации используются блоки определения максимума, минимума, сумматор и коммутатор. Цель изобретения - упрощение конструкции устройства, основанное на том, что оценивание диапазона флуктуации процесса может быть произведено по максимуму разности текущих значений выборки и минимума, благодаря чему не требуется блок определения максимума процесса и коммутатор. Эта цель достигается тем,.что в устройство введен регистр памяти,при этом соответствующие выходы старших разрядов сумматора .подключены ко входам регистра памяти, выходы которого соединены с соответствующими входами блока изменения масштаба. На чер.теже представлена блок-схема устройства. Устройство содержит аналогот-цифровой преобразсгватель 1, блок 2 управл.Ьния, блок 3 оценки минимума, сумматор 4, регистр 5 памяти, блок 6 изменения масштаба, коммутатор 7. Процесс адаптивного кодирования состоит из цикла адаптации- (длительностью TO) и цикла ад1аптивного кодир вания или измерения (длительностью Т Стационарный случайный процесс x{t) представляется на выходе аналого-цифрового преобразователя п-разрядным двоичным кодом. В цикле адаптации на сумматоре определяются значенияУ{.. (1) где у. - выходной код сумматора 1В момент времени i ; х - выходной код АЦП в момен времени t ,i minlr выходной код блока оценк минимума в,момент време ни1, . Значения у| поступают на регистр , в которой производится оценка максимального диапазона флуктуации процесса на интервале адаптации Утах)А )УтахА ( (2) где (х„„)д , (Хп,,)д - максимальное и минимальное значение случайног флуктуации является нрмер старшего, содержащего единицу разря да регистра. По окончании цикла адаптации в блоке изменения масштаба номер старше го, содержащего единицу разряда кода оценки (Ушах)А преобразуется в код масштаба М (К разрядов) , которой запоминается в выходном регистре блока. В зависимости от значения масштаба с помощью коммутатрра к выходу уст ройства кодирования подсоединяется , одна из S-разрядных (где ) групп. образованных из п- разрядного кода чис ла на выходе сумматора. Если код числа у представлен в виде ...ад. де fii - 4 -ый разряд двоичного кода, о из него образуются следующие Sазрядные группы; Ос,. . .020 . (3) S-IA°S- °2 °6 20&4С -Из °П°П-Г °П-54 Число Образованных групп, равное (n-S+l), определяет число масштабов представления результата. Вес млад его разряда группы, определяющий цену деления выходнрго кода, связан с масштабом М соотношением , (4) . . где ,1,2,...(n-S).. Таким образом,веса одноименных разрядов в каждой соседней группе отличаются в два раза.. В.цикле адаптивного кодирования (измерения) на сумматоре определяются значения ординат смещенного случайного процесса y(t): У (ХП,,,)Д , где XJ - значение выходного кода АЦП в момент времени цикла измерения. Полученные ординаты представляют н выходе устройства адаптивного кодирования S-разрядным двоичным кодом с ценой деления Z, соответствующей определенному в цикле адаптации масштабу М. Ч.исло разрядов S выбирается в соответствии с требуемой точностью измерения. В результате адаптивного кодирования на выходе устройства образуется массив значений выборок стационарного случайного процесса v(t) , определя.емых следующим образом;Ч rninl Очевидно, что восстановить исходный случайный процесс x(t) можно в соответствии с выражением xj 2vi + (xmJ. . (7 Устройство работает следующим образомкодируемый стационарный случайныйпроцесс x(t) поступает на вход п-раз« рядного аналого-цифрового преобразователя 1. Блок управления формирует тактовые импульсы, по которым аналого-цифровой преобразователь 1 вырабатывает ординаты х{. В течение цикла адаптации в блоке 3 оценки ми.нимума определяется текущее значение (х.:.,);. На сумматоре 4 осуществляется нахождение значений разности у, старшие (n-S) разряды которой поступают на вход регистра 5 памяти. Последний представляет собой реали-. зованный на RS-триггерах регистр, осуществляющий поразрядное логическое сложени.е входных кодов с кодами чисел, записанных на триггерах. Перед началом цикла адаптации КЗтриггеры устанавливаются в нуль сигналом на R-входах. S-входы триггеров подсоединены к соответствующим выходам старших разрядов сумматора. В течение цикла адаптации при определении величины с появлением логической 1 в к ком-либо разряде на-выходе сумматора соответствующий RS-триггер устан авливается в 1 и хранит ее до конца Цикла адаптации.. В момент времени, соответствующий концу цикла адаптацри, блок 2 управления вырабатывает импульс, по которому блок изменения 6 масштаба преобразует номер старше, го, содержащего единицу разряда в значение кода масштаба М, которое записывается в выходном регистре бло ка до конца процесса кодированая.При этом на выход коммутатора 7 подключается соответствующая S-разрядная группа (3) п-разрядного двоичного кода с выхода сумматора 4. Если 0(утах), то МвО, и на выход коммутатора 7 подсоединяются от 1-го до S-ro младших разрядов с выхода сумматора 4. Если 2()д то Msl, и на выход коммутатора 7 подсоединяются от 2-го до (S+l)-ro млад ших разрядов с выхода сумматора 4 и т.д. - . -;.. На зтом цикл адаптации заканчивается . В цикле адаптивного кодирования в каждом такте на выходе сумматора 4 образуется разность 4-(хпи|,) которая на выходе коммутатора 7 пред ставляется в виде vi. в соответствии с (6). Таким образом, независимо от диапазона флуктуации кодируемого процес са x(t) результат адаптивного кодирования представляется S-разрядным двоичным кодом. На соответствукицих выходах устройства также представлены значения (хп,4п)д (п-двоичных разрядов) и koд масштаба М (К-двоичных разрядов). Как.указывалось, восстановить исходный случайный процесс -x(t) возможно в соответствии (7). Применение регистра памяти позволяет значительно упростить известное устройство и,как следствие,повысить надежность работы. Формула изобретения Устройство для адаптивного кодирования стационарных случайных процессов, содержащее сумматор, первая группа входов которого объединена с соответствукицими входами блока оценки минимума и подключена к выходам аналого-цифрового преобразователя, информационный вход которого является входом устройства, управляющий вход аналого-цифрового прербразова- теля соедичэн с первым вьрсодом блока управления, второй выход которого подключен к управляющему входу блока изменения масштаба, выходы которого соединены с управляющими входами коммутатора и йвляются первой группой выходов устройства, инфо рмационные входы коммутатора подключ ены к соответствующим выходам сумматора, втот рая группа входов которого соединена Ь соответствующими выходами оценки минимума и является второй группой выходов устройства,о т л и чающееся тем,что,с целью упрощения устройства,в него введен регистр памяти,при этом выходы старших разрядов сумматора подключены соответственно ко входам регистра памяти, выходы которого соединены с соответствующими входами блока изменения масштаба. Источники информации, принятые во внимание при экспертизе ,1. Авторское свидетельство СССР 293239, кп. G Об F 5/02, 07.03.69.. 2.Авторское свидетельство СССР по заявке № 2461496/18-24, 11.03.77.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивного кодирования стационарных случайных процессов | 1977 |

|

SU734717A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Адаптивное устройство для масштабирования | 1983 |

|

SU1156091A1 |

| Групповой приемник сигналов управления и взаимодействия с адаптивной дифференциальной импульсно-кодовой модуляцией | 1991 |

|

SU1829126A1 |

| ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С АДАПТИВНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2103840C1 |

| Адаптивный вероятностный спектрокоррелятор | 1979 |

|

SU955087A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Устройство для непрерывного экспресс-анализа потоков случайных чисел | 1983 |

|

SU1101839A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

Авторы

Даты

1981-04-15—Публикация

1979-06-25—Подача