(54) СУММАТОР-ВЫЧИТАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный десятичный сумматор | 1975 |

|

SU690479A1 |

| Устройство для вычитания двоичнодесятичных кодов времени | 1976 |

|

SU595730A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Устройство для вычитания десятичных чисел | 1975 |

|

SU607216A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| "Одноразрядный десятичный сумматор в коде "5421" | 1988 |

|

SU1658143A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Преобразователь двоично-десятичного кода в двоичный | 1983 |

|

SU1095169A1 |

Изобретение относится k ычисли тельной технике и может быть использовано в арифмети еских устройствах ЭВМ, обрабатывающих информацию как в двоичном, так и в двоично-десятичном коде.

Известен двоично-десятичный сумматор, позволяющий суммировать и вычитать числа в двоично-десятичном коде, содержащий двоичный четырехразрядный сумматор, корректирукядий сумматор и узел коррекции fl.

Недостатком сумматора являются ограниченные функциональные возможности, так как он не позволяет суммировать и вычитать двоичные числа в двоичном коде.

Известен одноразрядный десятичный сумматор-вычитатель, содержащий четырехразрядный двоичный сумматор-вычитатель, трёхразрядный корректирукшшй двоичный сумматор, четыре элемента И и элемент ИЛИ. Данный сумматор поз воляет производить сумкшрование и вычитание двоично-десятичных чисел в зависимости от сигнала на управля-. ювоих входах путем суммирования или вычитания двоичных кодов десятичных чисел и формирования корректирующего кода для выходного кода двоичногсг сумматора-вычитателя t2j.

Однако одноразрядный десятичный с сумматор-вычитатель не позволяет суммировать и вычитать числа в двоичном коде.

Цепь изобретения - расширение функциональных возможностей сумматор а-вычитателя за счет возможности

10 суммирования и вычитания как двоично-десятичных , так и двоичных чисел.

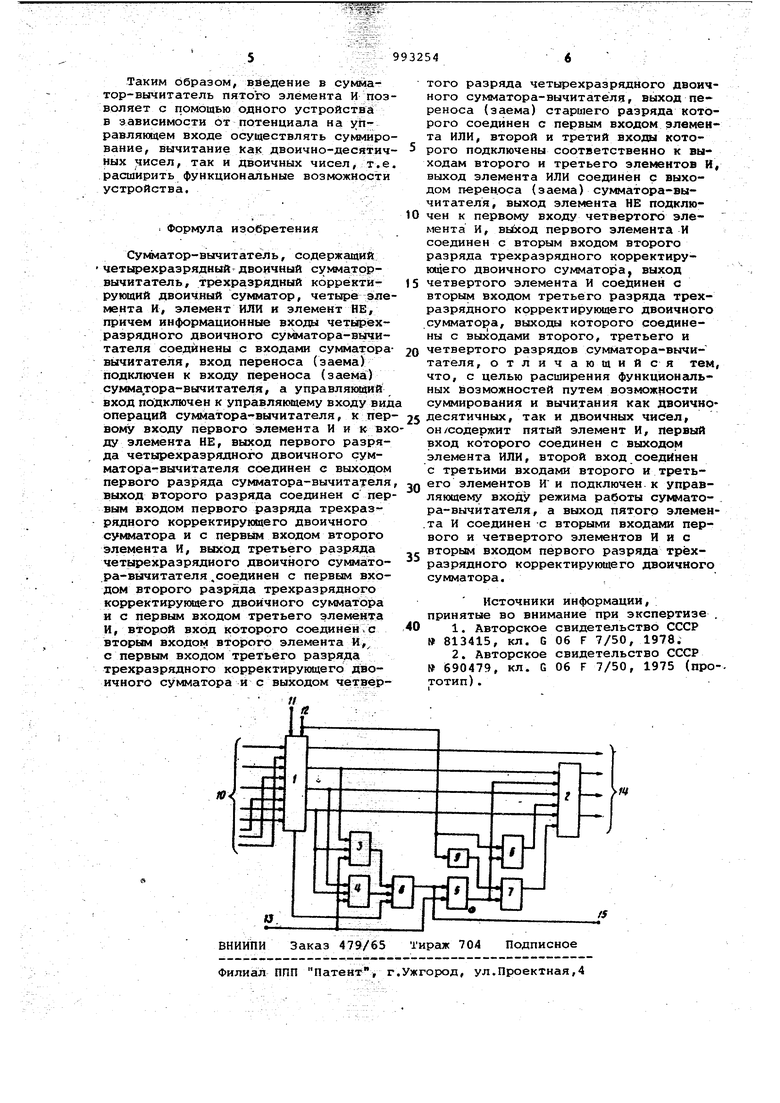

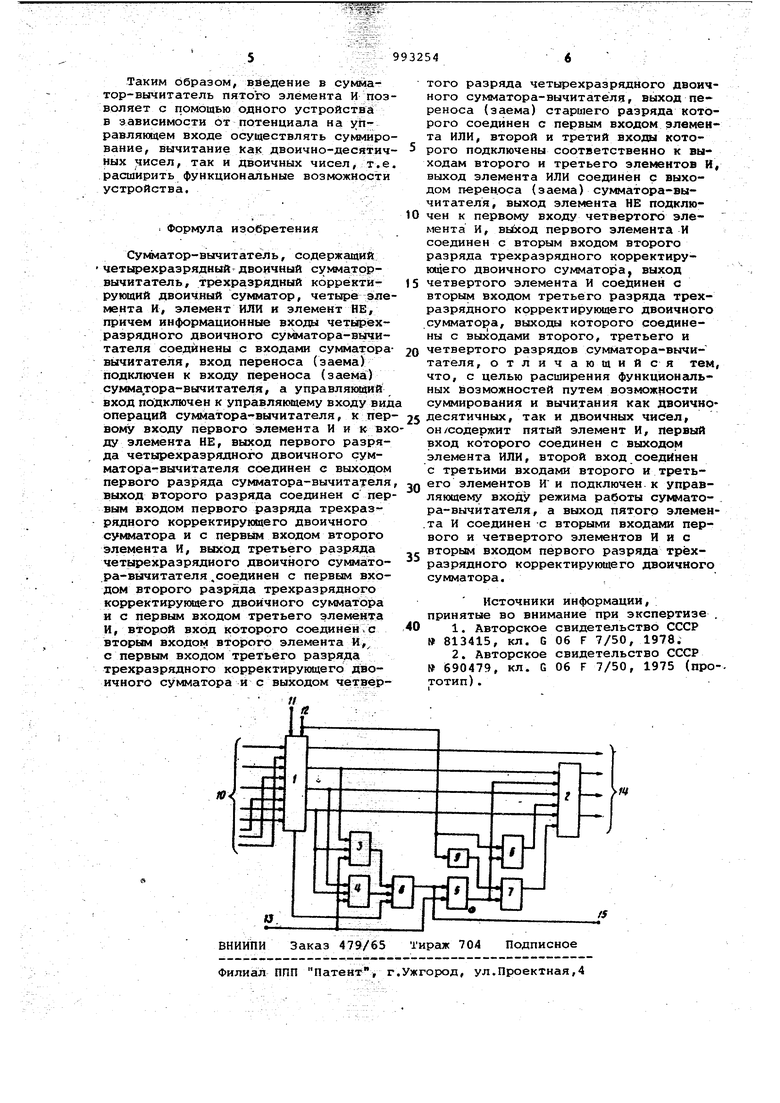

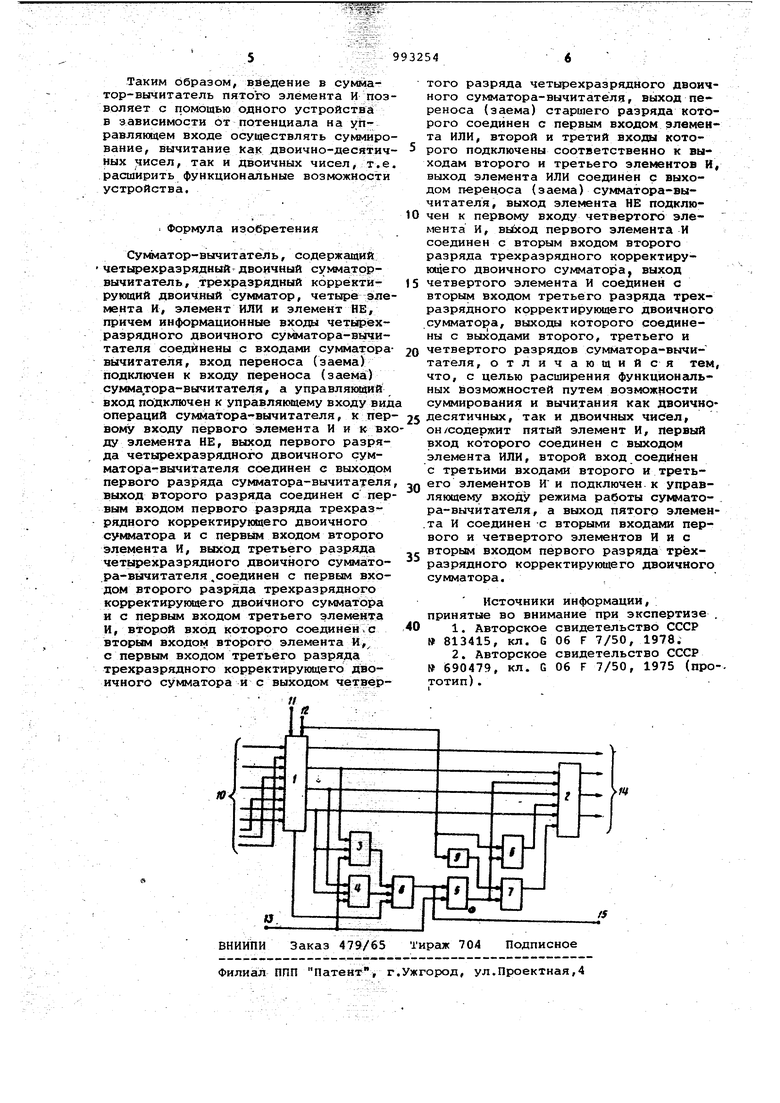

Поставленная цель достигается тем, что сумматор-вычитатель, содержащий четырехразрядный двоичный матор-вычитатель, трехразрядный корректируккций двоичный сумматор, четыре элемента И, элемент ИЛИ и элемент НЕ, причем информационные входы четырехразрядного двоичного сумматора20вычитателя соединены с входами сумматора-вычитателя, вход переноса (заема) подключен к входу переноса (заема) сумматора-вычитателя, а управляющий вход подключен к управля25 ющему входу вида операции сумматоравычитателя, к первому входу первого элемента Ник входу элемента НЕ, выход первого разряда четырехразрядного двоичного сумматора-вычитателя

30 соединен с выходом первого разряда сумматора-вычитателя, выход второго разряда соединенс первым входом первого разряда трехразрядного корректирующего двоичного сумматора и с первым входом второго элемента И, выход третьего разряда четырехразрядного двоичного сумматора-вычитателя соединен с первым входом второрого разряда трехразрядного коррект рующего двоичного сумматора и с пер вым входом третьего элемента И, вто рой вход которого соединен с вторым входом второго элемента И, с первым входом третьего разряда трехразрядного корректирующего двоичного, сумм тора и с выходом четвертого разряда четырехразрядного двоичного суммато ра-вычитателя, выход переноса (заем старшего разряда которого соединен с первым входом элемента ИЛИ, второй и третий входы которого подключены соответственно к выходам второго и третьего элементов И, выход элемента ИЛИ соединен с выходом переноса (заема) сумматора-вычитателя, выход элемента НЕ подключен к первому входу четвертого элемента И, выход первого элемента И соединен с вторым входом второго разряда трехразрядного корректирующего двоичного суммато ра, выход четвертого элемента И соединен с вторым входом третьего разр да трехразрядного корректирующего двоичного сумматора, выходы которого соединены с выходами второго, третьего и четвертого разрядов сумматоравычитатепя, введен также пятый элемент И, первый вход которого соединен с выходом элемента ИЛИ, второй вход соединен с третьими вводами вто рого и третьего элементов И и подключен к управляющему входу режима работы сумматора-вычитателя, а выход пятого элемента И соединен с вторыми входами первого и четвертого элементов и и с вторым входом первого разряда трехразрядного корректирующе го двоичноЛ сумматора. На чертеже приведена структурная схема, сумматора-вычитателя. Сумматор-вычитатель состоит из четырехразрядного двоичного суммаюра-вычитателя 1, трехраэрядного корректирукицего двоичного сумматора 2, элементов И 3-7, элемента ИЛИ 8 и элемента НЕ 9. Сумматор-вычитатель имеет минформационные входы 10 для подачи кодов операндов, вход 11 переноса (эаема), управляющий вход 12 вида операции, управляющий вход 13 режима работы, информационные выходы 14 и выход 15 переноса заема. Одноразрядный десятичный сумматор-вычйтатель работает следунхаим образом. На входы двоичного сумматора-вычитателя 1 поступают числа А и В и сигнал переноса (при сложеНИИ чисел А и В) или заема /i- -1 (при| вычитании чисел А и В). При наличии единичного потенциала на управляющем входе 12 осуществляется алгебраическое сложение чисел А+В, а при наличии нулевого потенциала - алгебраическое вычитание А-В. При подаче чисел А и В в двоичнодесятичном коде на управляющем входе 13 имеет место единичный потенциал, в этом случае на выходе двоичного сумматора-вычитателя 1 формируется сумма или разность входных чисел в двоичном коде, сигнал переноса, если сумма А+В 16-19 или сигнал заема, если разность А-В - отрицательная. Выходные сигналы с трех старяиих разрядов двоичного сумматора вычитателя 1 поступают на элементы И 3 и 4. На выходе элемента И 3 формируется сигнал переноса, если сумма А+В 10-11, а на в.ыходе элемента И 4 формируется сигнал переноса, если сумма А+В 12-15. Для получения суммы или разности чисел в двоично-десятичном коде необ ходимо к результату, полученному на выходе двоичного сумматора-вычитате- . ля 1 прибавить О (0000), если сумма или разность равны 0-9J 6 (ОНО), если сумма равна 10-19 и 10 (1010), если разность отрицательная. Для этого используется трехраэрядный корректирующий двоичный сумматор 2, на первые входы которого поступают сигналы с трех старших разрядов двоичного сумматора-вычитателя 1, на вторые входы - коды трех старших разрядов чисел О, 6 или 10. Для формирования трех старших разрядов чисел О, 6/ 10 используется выходной сигнаш переноса (заема) сумматора-вычитателя и сигнал управления СЛОЖЕНИЕ-КаЧИТАНИЕ. Число 000 получается, если сигнал переноса П равен нулю. Число 011 формируется при сложении чисел (при единичном потенциале на входе 12) при наличии сигнала переноса П, а число 101 формируется при вычитании чисел (при нулевом потенциале на входе 12) и при наличии сигнала заема 3{. При наличии нулевого потенциала на входе 13 производится подача чисел А и В в двоичном коде, при этом сигналом с входа 13 осуществляется блокировка формирования сигнала, когда сумма входных чисел равна 10-15 и формируется сигнал коррекции выходного кода двоичного сумматора-вычитателя 2, равный О (0000) путем блокировки сигнаша переноса (заема) сигналом со входа 13 с помощью элемента И 5. Результат формируется в двоичном коде.

Авторы

Даты

1983-01-30—Публикация

1981-08-17—Подача