ции устройства соединен с входом третьего элемента НЕ, третьими входами первого и четвертого элементов И и вторым входом пятого элемента И узла анализасоотношения знаков операндов, второй и третий входы второго элемента И узла ана-г ЛИЗа соотношения знаков операндов соединены с выходами первого и третьго элементов НЕ узла анализа соотношения знаков операндов соответственно, второй и третий входы третьего элемента И узла анализа соотношения знаков операндов соединены с выходами второго и третьего элементов НЕ узла анализа соотношения знаков операндов соответственно, третьи входы пятого и шестого элементов И узла анализа соотношения знаков операндов соединены с выходами второго и третьего элементов НЕ узла анализа соотношения знаков операндов соответственно , выходы третьего и четвертого элементов И узла анализа соотношения знаков операндов соединены с входами второго элемента ИЛИ узла анализа соотношения знаков операндов, выходы пятого и шестого элементов И узла анализа соотношения знаков операндов соединены с входами третьего элемента ИЛИ узла соотношения знаков операндов, выходы первого и второго элементов ИЛИ узла соотноше- НИН знаков операндов соединены с входами четвертого элемента ИЛИ узла,анализа соотношения знаков операндов, выход которого подключен к входу признака записи информации сумматора-вычитателя, выход заема старшего разряда которого соединен с входом элемента НЕ и вторым входом первого элемента И узла формирования знака результата, выход элемента НЕ узла формирования знака результата соединен с первым входом третьего элемента И узла формирования знака результата, выходы второго и третьего элементов ИЛИ уз3664

.ла анализа соотношения знаков операндов соединены с вторыми входами . второго и третьего элементов И узла формирования знака результата соответственно, выходы первого и третьего элементов И узла формирования знака результата подключены соответственно к второму и третьему входам элемента ИЛИ узла формирования знака результата, выход которого соединен с информационным входом знакового разряда сумматора-вычитателя, вход запуска устройства соединен с установочным входом сдвигового регистра узла формирования сигналов синх ронизации выход первого рязряда которюго соединен с первым входом элемента ИЛИ узла формирования сигналов синхронизации, выход которого соединен с входом разрешения записи сумматора-вычитателя, выход второго разряда сдвигового регистра узла формирования сигналов синхронизации соединен с входом разрешения регистра, выход третье- го разряда сдвигового регистра уз-; ла формирования сигналов .синхронизации соединен с входом разрешения считывания регистра и с вторым входом элемента ИЛИ узла формирования сигналов синхронизации, выход четвертого разряда сдвигового регистра узла формирования сигналов синхронизации соединен с входом разрешения записи знакового разряда cyMMiaтора-вычитателя, выход пятого разря-. да сдвигового регистра узла формирования сигналов синхронизации соединен с входом разрепения считывания сумматора-вычитателя и с входом элемента НЕ узла формирования сигналов синхронизации, выход котордго соединен с первым входом элемента И узла формирования сигналов синхронизации, второй вход и выход которого соединены соответственно р выходом генератора тактовых импульсов и входом сдвига сдвигового регистра узла формирования сигналов синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg(y/x) | 2015 |

|

RU2595486C1 |

| Двоичное устройство деления | 1974 |

|

SU497585A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для деления двоичных чисел | 1981 |

|

SU1008733A1 |

УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ, содержащее сумматор-вычитатель и блок -управления, включающий узел, анализа соотношения знаков операндов и узел, формирования знака результата, причем первая группа информационных входов сумматора-вычитателя соединена с входами перво- . го операнда устройства, выходы сум- матора-вычитателя соединены с выходами устройства, узел анализа соотношения операндов знаков содержит три элемента НЕ, первый, второй, третий и четвертый элементы И, первый элемент ИЛИ, узел формирования знака результата содержит элемент НЕ, три элемента И и элемент ИЛИ, при этом выходы первого и второго элементов НЕ узла анализа соотношения знаков операндов соединены соответственно с первым и вторым входами первого элемента И узла анализа соотношения знаков операндов, выход которого соединен с первым входом первого элемента ИЛИ узпа анализа соотношения знаков операндов, второй вход которого подключен к выходу второго элемента И -узла анализа соотношения знаков операндов, а выход соединен с первым входом первого элемента И узпа формирования знака результата, выход элемента НЕ узпа формирования знака результата подключен к первому вхбку второго элемента И узпа формирования знака результата., выход которого соединен с первым входом элемента ИЛИ узпа формирования знака результата, от л и.ч а ю щ е е с я тем, что, с целью повьш1ения быстродействия,, устройство содержит регистр, в блок управления введен узел формиро(Л вания сигналов синхронизации, содержащий генератор тактовых импульсов, сдвиговый регистр, элемент НЕ, элемент И, элемент ИЛИ, в узел анализа соотношения знаков операндов введены пятый и шестой элементы И, второй, третий и четвертый элементы ИЛИ, о со причем информационные входы регистра соединены с входами второго операн-. да устройства, выходы регистра соеОд динены с первой и второй группами информационных входов сумматора-вычитателя, выход знакового разряда которого соедцрен с входом первогоэлемента НЕ и первыми входами третьего, четвертого, пятого и шестого элементов И узла анализа соотношения знаков операндов, выход знакового разряда регистра соединен с входом второго элемента НЕ, первым входом второго элемента И и вторыми входами четвертого и шестого элементов И узпа анализа соотношения знаков операндов, вход кода опера

Изобретение относится к вычислительной технике и может быть использов но при построении оптоэлектронных арифметических устройств для

3

сложения и вычитания десятичных чисел.

I

Целью изобретения является повышение быстродействия устройства.

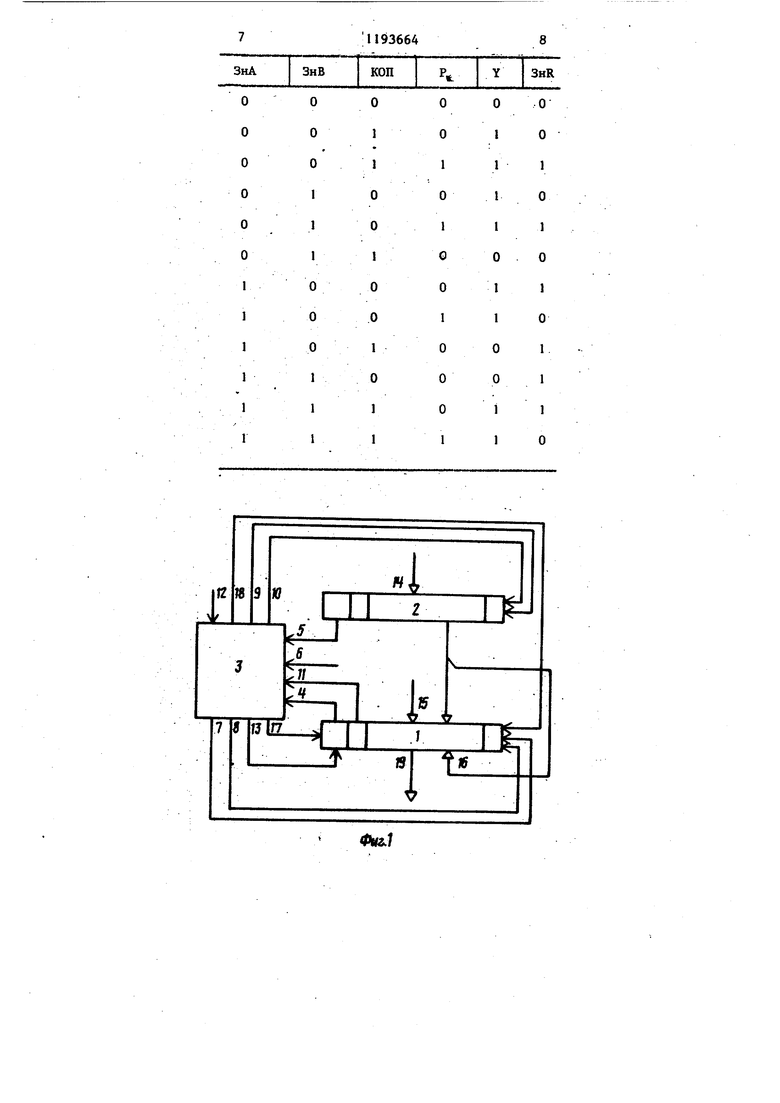

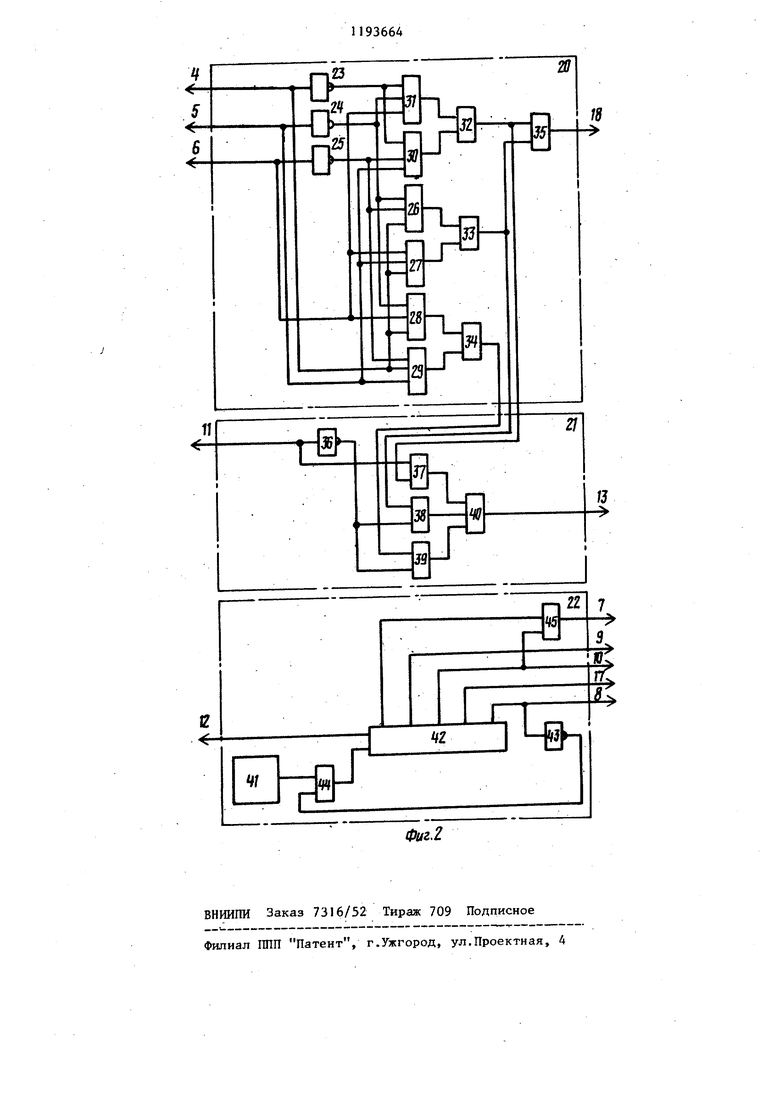

На фиг.1 представлена блок-схема устройства для сложения и вычитания на фиг.2 - структурная схема блока управления.

Устройство для сложения и вычитания содержит сумматор-вычитатель регистр 2 и блок 3 управления. Знаковые ра:зряды сумматора-вычитатеI и регистра 2 связаны соответствен но с входаьФ 4 и 5 блока 3 управления, на вход 6 которого подается код операции с входа кода операции устройства. Выходы 7 и 8 блока управления соединены соответственно с входаьш разрешения записи и разрешения считывания сумматора- вычитателя 1, а выходы 9 и 10 - с управлякицими входами разрешения записи и разрешения считывания регистра 2. Выход заема старшего разр .да сумматора-вычитателя 1 подключен к входу 11 блока 3 управления, вход 12 которого соединен с входом запуска, а выход 13 соединен с информационным входом знакового разряда сумматора-вычитатепя 1, Входы 14 регистра 2 соединены с входами второго операщ1а устройства, выходы .регистра 2 соединены с информационными входами 15 и 16 первой и второй групп сумматора-вычитате- ля1. Выход 17 блока 3 управления подключен к входу разрешения записи знакового разряда сумматора-вычитателя I, а выход 18 - к входу признака записи информации сумматораг вычитателя 1, выходы 19 которого ., соединены с выходами устройства.

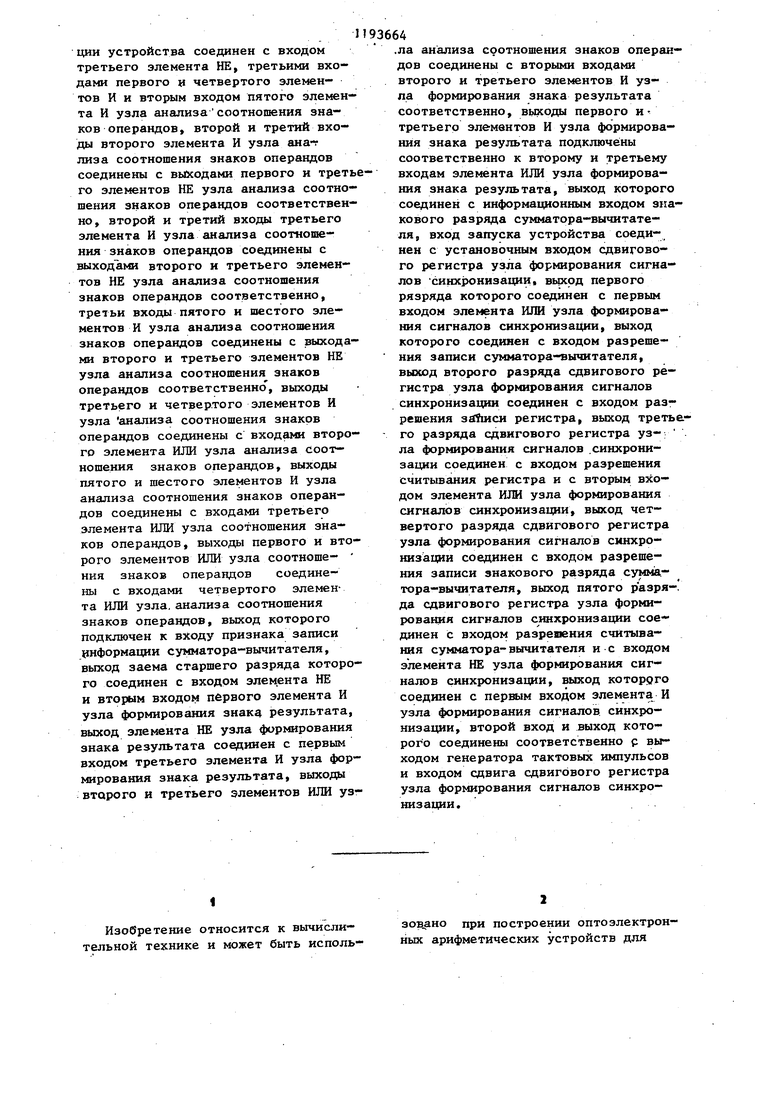

Блок 3 управления (фиг.2) содержит узел 20 анализа соотношения знаков операндов, узел 21 формирования знака результата и узел 22 формирования сигналов синхронизации.

В узле 20 входы 4,5 и 6 блока 3 управления соединены соответственно с входами злементов НЕ 23-25« Вход 4 блока 3 управления соединен с входами элементов И 26-29, ,вход 5 - с входами элементов И 27, 29 и 30, вход 6 - с- входами злементов И 27, 28 и 31. Выход элемента НЕ 23 соединен с входами элементов И 30 и 31, выход элемента НЕ .24

с входами элементов И 26, 28 и 34, выход элемента НЕ 25 - с входами элементов И 26, 29 и 30. Выходы элементов И 30 и 31 подключены к входам

5 элемента ИЛИ 32, выходы злементов И 26 и 27 - к входам элемента ИЛИ 33, выходы элементов И 28 и 29 - к входам элемента ИЛИ 34. Входы элемента ИЛИ 35 соединены с выходами элементов ИЛИ 32 и 33, а его выход является выходом 18 блока 3 управления. В узле 21 формирования знака результата вход 11 блока 3 управления соединен с входом элемента НЕ 36 и

15 входом элемента И 37, выход элемента НЕ 36 подключен к входам элементов И 38 и 39. Другие входы элементов И 37-39 соединены соответственно с выходами элементов ИЛИ 32-34,

20 а выхода - с входами элемента ИЛИ 40, выход которого является выходом 13 блока 3 управления.

Узел 22 формирования сигналов синхронизации содержит генератор 41

25 тактовых импульсов, сдвиговый ре- .гистр 42 и элементы НЕ 43, И 44-, ИЛИ 45, причем вход 12 блока 3 управления соединен с установочным входом сдвигового регистра 42, вцходы

30 генератора 41 и элемента НЕ 43 соединены с входами элемента И 44, выход которого подключен к входу сдвига сдвигового реги.стра 42, содержащего пять рязрядов. Выходы первого и третьего разрядов сдвигового

35 регистра 42 соединены с входами элемента ИЛИ 45, выход которого является выходом 7 блока 3 управления, выходы второго, третьего, четверто- го и пятого разрядов сдвигового ре40гистра 42 являются выходами- 9, 10, 17 и 8 блока 3 управления соответственно, кроме того, выход пятого раз- :ряда регистра 42 соединен с входом элемента НЕ 43.

Устройство работает следукядим образом.

В начальный момент времени cy fматор-вычитатель 1 и регистр 2 обнулены. Запись информации в сумматорвычитатель 1 выполняется при появле1€ии управляющего сигнала на выходе 7 блока 3 управления; этот сигнал формируется при наличии сигнала заSS пуска на входе 12 блока 3 управления. Затем выполняется запись второго операнда в регистр 2 по управляющему сигналу, поступающему с выхода 9

блока 3 управления. Запись информации в сумматор-вычитатель 1 и регистр 2 осуществляется по входам 15 и 14 соответственно. С выходов знаковых разрядов сумматора-вьгчитателя 1 и регистра 2 информации о знаках операндов по входам 4 и 5 подается в блок 3 управления, на вход 6 которого поступает код операции. Блок 3 управления формирует Б соответствии с этим сигнал на выходе 18, разрешающий запись информации из регистра 2 в сумматор-вычи- татель 1 по входам 16 при наличии сигналов одновременно на выходах 7 и 10 блока 3 управления, управляющих записью информа1Ц1и в сумма- тор-вычитатель 1 и считыванием информации из регистра 2. При записи в сумматор-вычитатель 1 второго елагаемого происходит параллельное суммирование операндов, если второе слагаемое поступает по входам 15, или параллельное вычитание, если оно поступает по входам 16. По управ ляющему сигналу на выходе 17 блока 3 управления в знаковый разряд сумматора-вычитателя 1 осуществляется запись знака результата, поступающего с выхода 13 блока.3 управления. Считывание результата выполняется с выходов 19 сумматора-вычитателя 1 при иаличйи управлякщего сигнала на выходе 8 блока 3 управления..

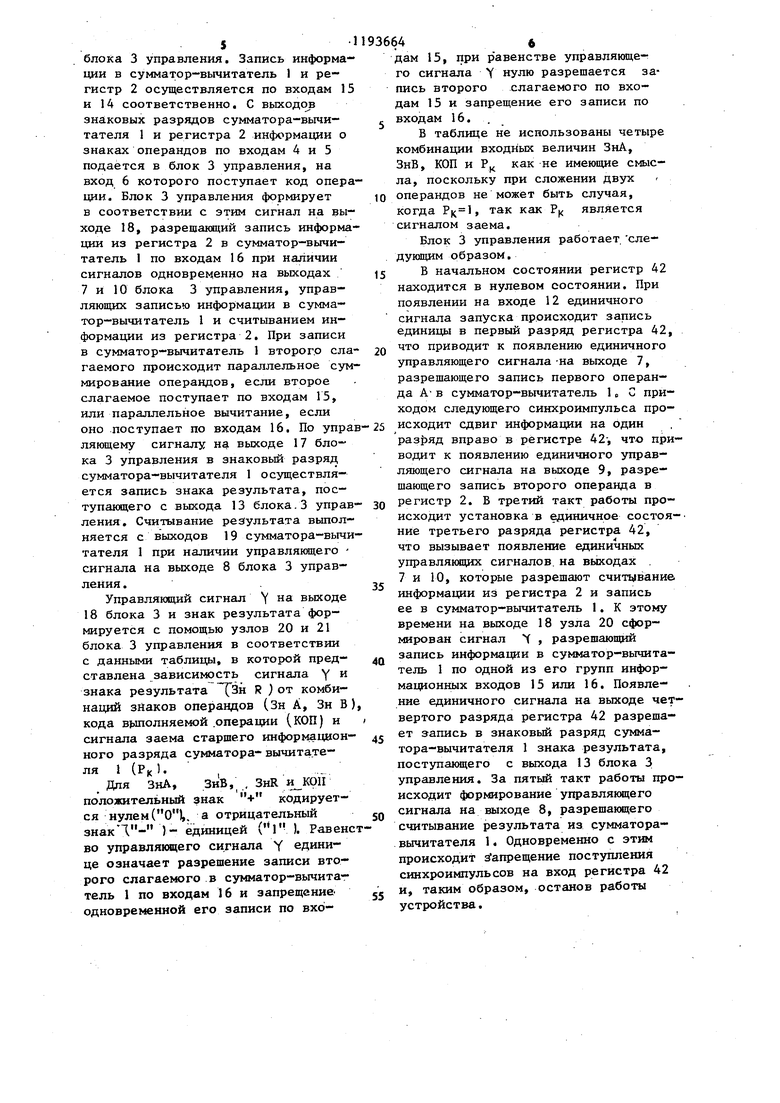

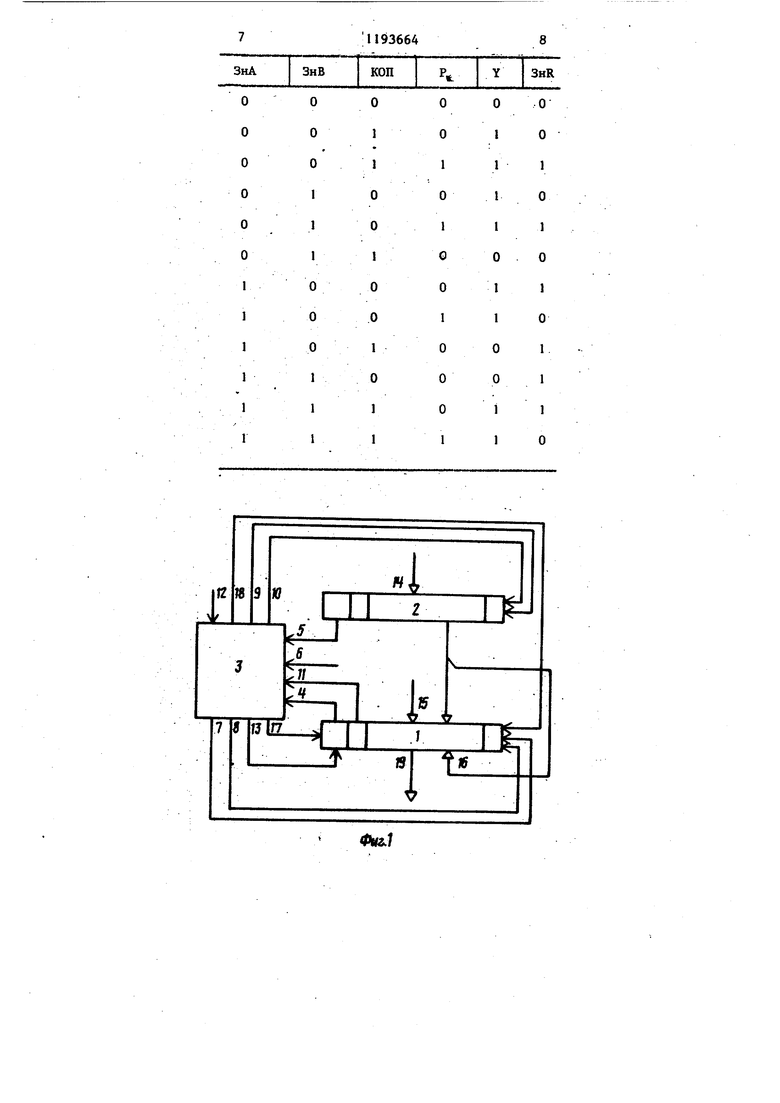

Управляющий сигнал на выходе 18 блока 3 и знак результата формируется с помощью узлов 20 и 21 блока 3 управления в соответствии с данными таблицы, в которой представлена зависимость сигнала Y и знака результата 3н R ) от комбинаций знаков операндов (Зн А, Зн В), кода в} шолняемой .операции (КОП) и сигнала заема старшего информационного разряда сумматора-вычитателя 1 (РК 1.

Для ЗнА, ЗнВ, , ЗнК положительный знак + кодируется нулем (О),, а отрицательный знак .- )- единицей (1 ). Равенство управляющего сигнала Y единице означает разрешение записи второго слагаемого в сумматор-вычита- тель 1 по входам 16 и запрещение одновременной его записи по входам 15, при равенстве управляющего сигнала У нулю разрешается запись второго слагаемого по входам 15 и запрещение его записи по входам 16..

В таблице не использованы четыре комбинации входных величин ЗнА, ЗнВ, КОП и Р как не имеющие смысла, поскольку при сложении двух операндов не может быть случая, когда , так как Р| является сигналом заема.

Блок 3 управления работает следующим образом.

В начальном состоянии регистр 42 находится в нулевом состоянии. При появлении на входе 12 единичного сигнала запуска происходит запись единицы в первый разряд регистра 42, что приводит к появлению единичного управляющего сигнала-на выходе 7, разрешающего запись первого операнда А-в сумматор-вычитатель 1„ С приходом следующего синхроимпульса происходит сдвиг информации на один разряд вправо в регистре 42-, что приводит к появлению единичного управляющего сигнала на выходе 9, разрешающего запись второго операнда в регистр 2. В третий такт работы происходит установка в единичное состоя ние третьего разряда регистра 42, что вызывает появление единичных управляющих сигналов, на выходах . 7 и 10, которые разрешают считывание информации из регистра 2 и запись ее в сумматор-вычитатель 1. К этому времени на выходе 18 узла 20 сформирован сигнал Ч , разрешающий запись информации в сумматор-вычитатель 1 по одной из его групп информационных входов 15 или 16. Появление единичного сигнала на выходе четвертого разряда регистра 42 разрешает запись в зиаковый разряд сумматора-вычитателя 1 знака результата, поступакщего с выхода 13 блока 3 управления. За пятый такт работы происходит формирование управляющего сигнала на выходе 8, разрешающего считывание результата из сумматоравычитателя 1. Одновременно с этим происходит аГащ5ещение поступления синхроимпульсов на вход регистра 42 и, таким образом, останов работы устройства.

18

-

Я

tra

Sh

Л

tL

Й

13

й

22

tt

Z

| Букреев И.Н | |||

| и др | |||

| Микроэлектроиные схемы цифровых устройств, М.: Советское радио, 1975, с.339341, рис.8.15, 8.16 | |||

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

Авторы

Даты

1985-11-23—Публикация

1984-03-29—Подача