(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕКЛЮЧЕНИЕМ СКОЛЬЗЯЩЕГО РЕЗЕРВА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления переключением скользящего резерва | 1983 |

|

SU1163327A1 |

| Устройство для управления переключением скользящего резерва | 1978 |

|

SU746526A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Многоканальное устройство для включения резервных радиостанций | 1990 |

|

SU1748299A1 |

| Система коммутации | 1986 |

|

SU1359783A1 |

| Многоканальный коммутатор | 1980 |

|

SU869033A1 |

| Устройство для задания тестов | 1981 |

|

SU1010632A1 |

| Устройство для управления реконфигурацией резервированной вычислительной систем | 1989 |

|

SU1718398A1 |

| Устройство для управления переключением резерва | 1980 |

|

SU1010734A1 |

| Отказоустойчивое устройство для умножения чисел | 1990 |

|

SU1777134A1 |

1

Изобретение относится к автоматике и может быть использовано для автематического скользящего резервирования узлов радиоэлектронной аппаратуры .

Известно устройство скользящего резервирования замещением, осуществляющее отключение отказавшего основного блока и включение в работу резервного блока, содержащее элементы контроля основных и резервных блоков, инверторы, элементы И-НЕ, коммутатор DJ

Однако в известном устройстве скользящее резервнрованиё отказавших блоков производится путем последовательного опроса элементов контроля всех блоков, независимо от их исправного или неисправного состояния, и выборки резервных блоков из числа исправных блоков, В этом случае увеличивается время выборки скол зящего резерва и снижается быстродействие устройства.

Наиболее близким техническим решением к предлагаемому изобретению является устройсцго, содержащее элементы контроля основных и резервных блоков, блоки приоритета, коммутаторы, элементы И, ИЛИ 2,

Однако в известном устройстве осуществляется приоритетное управление выборкой скользящего резерва, что повышает его быстродействие, однако в известном устройстве в качестве основных и резервных блоков используют только однотипные блоки. Это ограничивает возможности использования известного устройства в Комплексах, со0держащих различные по своему функциональному исполнению блоки. При скользящем резервировании аппаратуры сложных комплексов в состав резерва .комплекса входят различные блоки,каждалй

5 из которых соответствует одному или группе однотипных основных блоков и подключается вместо соответствующего ему отказавшего основного блока Иоэтому.резервирование комплексов

0 с потющью известных устройств возможно только путем применения нескольких таких устройств по числу типов основных блоков, каждое из которых обеспечивает резервирование

5 своей группы однотипных основных блоков. Однако это ведет к резкому осложнению комплекса в целом, его удорожанию и снижению надежности,

Цель изобретения - расширение функциональных возможностей устройства

для управления переключеЕ(ием скользящего резерва.

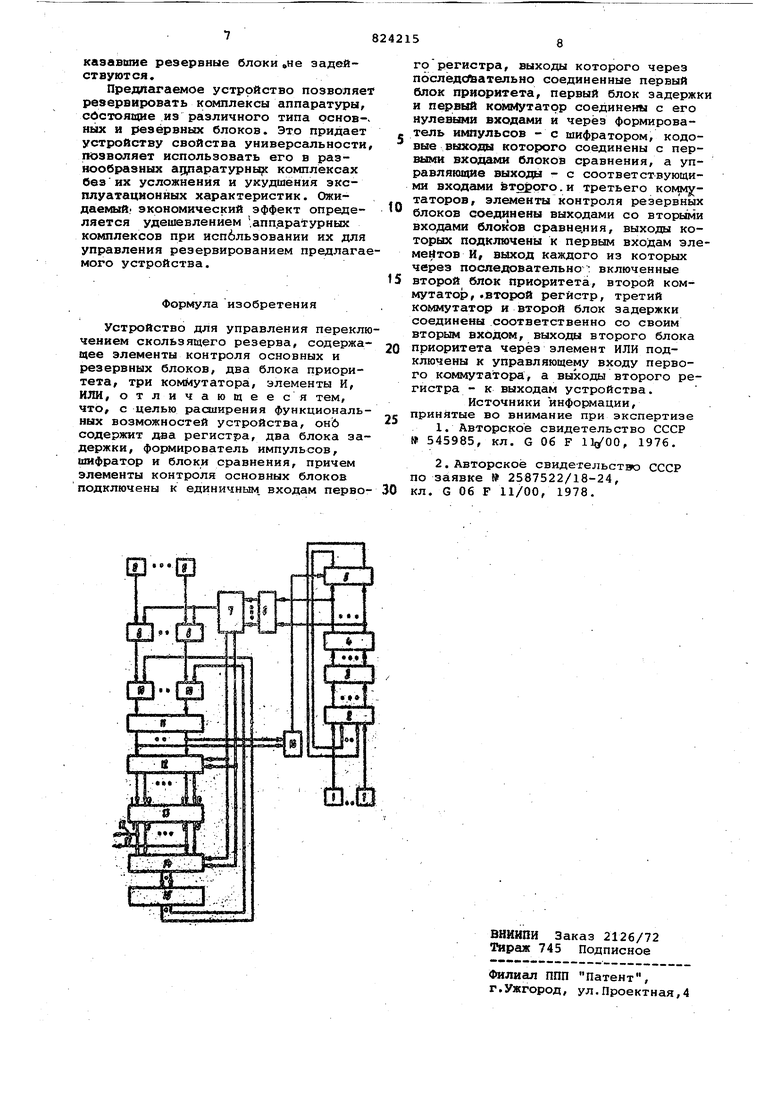

Указанная цель достигается тем, что в устройство, содержащее элеменrt контроля основных и резервных блоков, два блока приоритета, три коммутатора, элементы И, ИЛИ, введены два регистра, два блока задержки, формирователь импульсоп, шифратор и Олоки сравнения, причем элементы контроля основных блоков подкгаочёны к единичным входам первого регистра, выводы которого через последовательн включенные первый блок приоритета, первый блок задержки и первый коммут тор соединены с его нулевыми входами и через формирователь им1туль сов - с шифратором, кодовые выходы которого соединены с первыми входами блоков сравнения, а управляющие выхода) - с соответствующими входами второго и третьего коммутаторов, элементы контроля резервных блоков соединены выходами со вторыми входами блоков сравнения, выходы которых подключены к первым входам элементов И, выход каждого из которых через rjocледовательно включенные второй блок приоритета, второй коммутатор, ; второй регистр, третий коммутатор и яторОй блок задержки соединен соответственно со своим вторым входом, )ю 1ходы второго блока приоритета чере элемент ИЛИ подключены к управляю- тему входу первоге коммутатора, а выходы второго регистра - к выходам устройства.

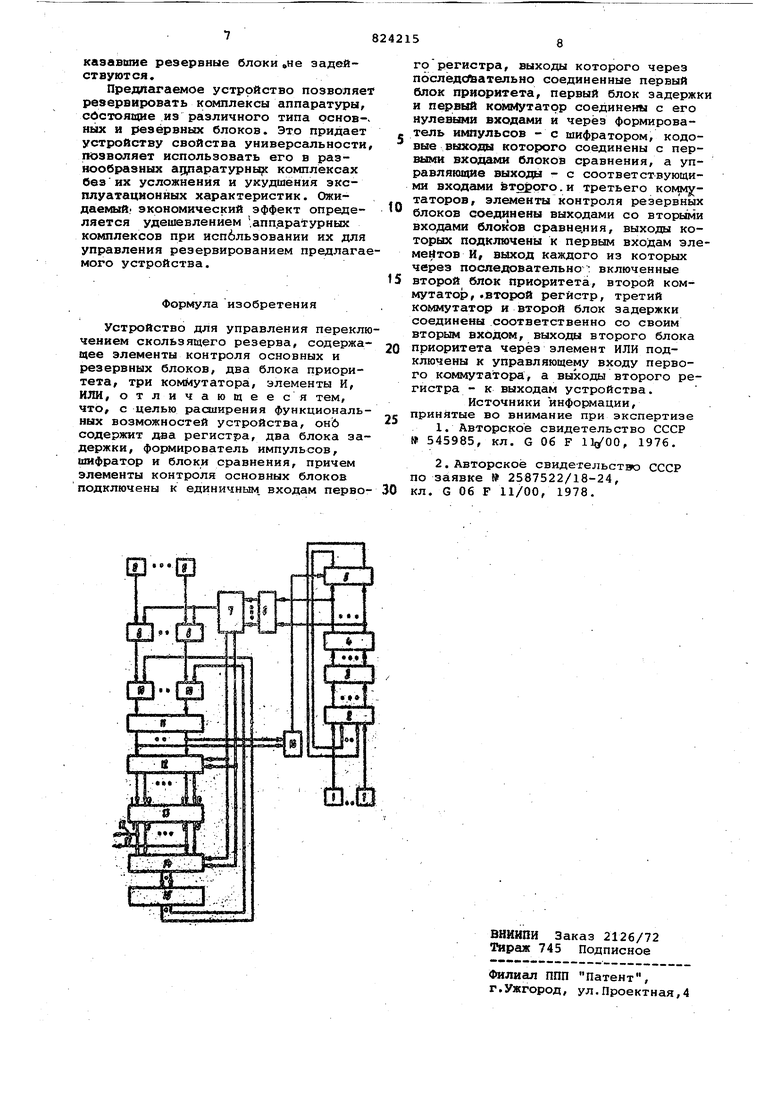

На чертеже представлена схема устройства для управления переключением скользящего резерва.

Элементы контроля основных блоков 1 соединены с единичными входами первого регистра 2, выходы которого через последовательно включенные первый блок 3 приоритета, первый блок:. 4 задержки и первый кс влутатор 5 подключены к соответствующим нулевым входам регистра 2. Кроме того, выход первого блока 4 задержки через формирователь б импульсов соединены с .входами шифратора 7. Кодовые выходы шифратора 7 подключены к первым входам всех блоков 8 сравнения, вторые входи которых соединены с элементами контроля резервных блоков 9. Шяходы блоков 8 сравнения пoдкJBoчeны к первым входам элементов И 10, выхода) KOTopdX через второй блок 11 приоритета связаны с входаьш птбр5го коммутатора 12. Одна группа выходов второго KoivBvfyTaTopa 12 подк взчана к единичным входам второго регистра 13, а другая группа его выходов - к нулевым входам этого регистра. Единичные и нулевые выходы регистра 13 подключены соответственно к первой и второй группе входов третьего коммутатора 14, выходы которого через вто рой блок 15 задержки связаны .со вторыми входами соответствующих элементов И . Выходы второго блока 11 приоритета через элемент ИЛ1 16 ключены к управляющему вход/ первого коммутатора 5. Два управляющих выхода с шифратора 7 подключены к управляющим входам второго и третьего коммутаторов 12 и 14, а единичные выходы второго регистра 13 - к выходам устройства 17.

п Блоки 3 и 11приоритета представляют собой логические статические устройства, содержащие э-лементы ИЛИ и ЗАПРЕТА и обеспечивающие на своих выходах приоритетно.е распределение входных сигналов. При этом, например, каждый входной .сигнал на предыдущем вхсГде имеет приоритет прохождения на выход по отношению к сигналам н.а всех последующих входах. Таким образом, блок приоритета формирует выходной сигнал только на одном выходе, соответствующем входу с большим приоритете. Элементы контроля основных блоков 1 формируют для каждого основного блока импульсные сигналы отказа и восстановления, которые подаются на единичные входы соответствующих групп разрядов регистра 2. Выходы регистра 2 подключены к входам блока 3 приоритета таким

.J образом, что последний обеспечивает , следующее приоритетное распределение сигналов с разрядов групп этого регистра; группа разрядов отказа имеет приоритет над группой разрядов

восстановления, а в каждой из ука .занных групп предыдущий разряд имеет приоритет по отношению ко всем последующим. Блоки 4 и 15 задержки обеспечивают синхронность работы всех элементов устройства.

0 Устройство работает следующим образом

Элементы контроля ос:;овных блоков 1 формируют сигналы отказов и последующего восстановления основных

5 блоков, которые в виде импульсов поступают «а единичные входы соответствующих разрядов регистра 2 и устанавливают их в единичные состояния. Таким образом в регистре 2 фиксил pyefся текущее состояние основных блоков. С выходов взведенных разрядов pefKcy a 2 потенциальные сиг-;налы отказов и восстановления nQcтупшот на блок 3. При этом на выкод блока 3 проходит только один сигнал,

5 поступающий на его вход с высишм nф иopитвтoм по отношению к другим его входшл например сигнал отказа основйС го блока. Укаэанный -сигнал . че1эеа блок 4 подается на вход коммутатора 5 и на формирователь 6. Ш следвиЯ формирует импульс и возбуждает соответствующий вход шифратора 7, каждый вход которого соотвегствует определенному типу основ5 igppo 6.яока и его текущему состоянию

(отказ или восстановление). При;этом на кодовых выходах шифратора 7 формируется параллельный импульсный код признака отказавшего блока и возбуждается один из управляющих выходов шифратора, соответствующий текущему состоянию основного блока/ т.е. его отказу. Сигнал с этого управляющего выхода шифратора 7 подается на соответствующие входы коммутаторов 12, 14 и устанавливает их в следу рщие состояния: коммутатор 12 подключает выходы блока единичным входам регистра 13, а коммутатор 14 подкл1рчает входы блока 15 к нулевым выходам регистра 13. При этом в исходном состоянии регистра 13 с его нулевых выходов подаются высокие ino.. тенциалы через коммутатор 14 и блок 15 на вторые входы элементов И 10. Одновременно код типа отказавшего основного блока поступа.ет на первые, ходы всех блоков 8 сравнения, на вторые входы которых поступают коды типов резервных блоков с выходов элементов 9. С помощью блоков 8 выявляются все резервные блоки требуемого типа из всей совокупности резервных блвков. При совпадении кодов на обоих входах блоков 8 происходит их срабатывание. Импульсные сигналы совпадения с выходов сработавших блоков сравнения поступают на первые входы соответствующих элементов И 10, на вторые входы которых подают высокий потенциал, и последние открываются. С выходов открытых элементов И 10 сигналы подаются на входы блока 11 приоритета, который формирует сиЬнал на одном выходе, со,ответствующем входу большого приоритета . Этот сигнал поступает через элемент ИЛИ 16 на управляющий вход коммутатора 5, и через коммутатор 12 - на единичный вход соответствующего разряда регистра 13. Указанный разряд регистра 13 устанавливается в единичное.состояние, при этом снимается высокий потенциал с его нулевого выхода и, следовательно, со второго входа -соответствующего элемента И 10. Последний блокирует соответствуювшй блок сравнения для дальнейшего его использования в процессе включения резервных блоков. Кроме того, с единичного выхода еработанного разряда регистра 13 выдается сигнал через выход 17 на исполнительный элемент соответствующего , резервного блока, который включается вместо отказавшего основного блока. Одновременно управляю1ф1й сигнал на входе коммутатора 5 разрешает прохождение сигнала с выхода блока 4 задержки на нулевой вход соответствующего разряда регистра 2, который устанавливает, этоф разряд в нулевое положение. При этом приоритет на выход в блоке 3 получает сигнал с

выхода следующего разряда группы отказов регистра 2 и происходит выбор и включение следующего резервного блока, соответствующего од-каэавшему очередному основному блоку. После сбрасывания все сработанных разрядов группы отказов регистра 2, приоритет на выход последовательно получает разряды группы восстановления этого регистра. С выходов.блоки 3 приоритета сигналы последовательно подаются на

o коммутатор 5 и через формирователь

6на входы шифратора 7, соответствующие типу восстановленного блока и его текущему состоянию (восстановления). При этом на кодовых выходах шифратора

5

7формируется код типа восстановленного основного блока и возбуждается другой управляющий выход шифратора, соответствующий восстанов; енному состоянию осыовнЬто блока. Сигнал с этого управляющего выхода шифратора 7 по0дается на входы коммутаторов 12, 14 .

и устанавливает их в следующие состояния: коммутат.ор 12 подключает выходы блока 11 к нулевым входам регистра 13, а коммутатор 14 подключает входы

5 блока 15 к единичным выходам регистра 13. При этом высокие потенциалы с единичных выходов регистра 13, соответствующих Включенным резервным блокам, подаются через коммутатор

0 14 и,блок 15 на вторыевходы соответствующих элементов И 10. С помощью блоков В выявляются все резервные блоки, однотипные с восстановленным резервным блоком, а с помощью

5 элементов И 10 - включенные резервные блоки данного типа. Сигналы с выходов сработанных блоков 8 сравнения через элементы И 10 подаются на блок 11, которьй формирует сиг0нал на соответствующем выходе. Этот сигнал через коммутатор 12 подается на нулевой вход соответствующего разряда регистру 13 и устанавливает его в нулевое положение. При этом происходит снятие .сигнала с выхода 17 и

5 отключение соответствующего резервного блока, а также снятие разрешакяцего потенциала со второго входа соответствующего элемента И 10, который за.крызвается и блокирует соответствую0щий блок 8 япя дальнейшего использования в режиме восстановления. Одиовремеаво сигнал с выхода блока 11 через элемент ИЛИ 16 и коммутатор 5 обнуляет соответствующий сброс ре5гистра 2, что обеспечивает последо вателвеый разряд всех разрядов группы воссФановяеяия этого регистра, ноеледовательйое отключение соответствуюЕфйх блоков и воз0врат устройства в исходное состояние .

В случае отказа резервных блоков с выходов соответствующих элементов 9 не выдаются кодовые сигналы на входа блоков 8, и следовательно, от5

Авторы

Даты

1981-04-23—Публикация

1979-02-19—Подача