Изобретение относится к области вычислительной техники и может быть использовано при разработке быстродействующих устройств умножения чисел повышенной надежности, удобных для изготовления с применением технологии БИС и СБИС.

Известно устройство умножения чисел, содержащее п операционных блоков (п - разрядность множимого), каждый из которых включает одноразрядный регистр множимого, узел вычисления разрядных значений произведения и два буферных регистра с соответствующими связями.

Данное устройство удобно для изготовления с применением БИС и СБИС, отличается достаточно высоким быстродействием. Недостатком его является низкая надежность.

Наиболее близким по технической сущности к изобретению является отказоустойчивое устройство умножения чисел, содержащее п основных операционных блоков (п - разрядность множимого), m резервных операционных блоков (т 1,2,3,...), первую и вторую группы по (n+m) коммутаторов, m коммутаторов множимого, гп регистров замены, п элементов ИЛИ и блок управления, причем вход множителя устройства соединен с входами множителя основных и резер- вных операционных блоков, вход слагаемого j-ro основного операционного блока (j 1п) соединен с первым выходом j-ro коммутатора первой группы, вход множимого - с входом множимого устройства и информационным входом k-ro коммутатора множимого (k 1m), выход которого

соединен с входом множимого k-ro резервного операционного блока, вход слагаемого которого соединен с выходом (n+k)-ro коммутатора первой группы, j-й информацион

ч

GO 4

ный вход которого соединен с вторым выходом J-ro коммутатора первой группы, выход результата j-ro основного операционного блока соединен с первым информационным входом J-ro коммутатора второй группы, второй информационный вход которого соединен с выходом j-ro элемента ИЛИ, k-й вход которого соединен с j-м выходом (n+k)- го коммутатора второй группы, информационный вход которого соединен с выходом результата k-ro резервного операционного блока, информационный вход 1-го коммутатора первой группы (1 1п-1) соединен

с выходом (1+1}-го коммутатора второй группы, управляющие входы J-x коммутаторов первой и второй групп объединены между собой и соединены с выходом отказа J-ro основного блока блока управления и первыми входами m регистров замены, первый выход k-ro регистра замены соединен с управляющими входами k-ro коммутатора множимого и (n+k)-x коммутаторов первой и второй групп, второй выход k-ro регистра замены соединен с вторым входом (k+1)-ro регистра замены, второй выход m-ro регистра замены соединен с выходом структуры устройства, вход запрета которого соединен с вторым входом первого регистра замены, выход первого коммутатора второй группы соединен с выходом результата устройства, вход коррекции которого соединен с информационным входом n-го коммутатора первой группы, третий и четвертый входы m регистров замены соединены соответственно с вторым выходом блока управления, первым входом блока управления и первым входом контроля устройства, второй вход контроля которого соединен с вторым входом блока управления, третий и четвертый выходы которого соединены соответственно с выходами отказа и прерывания устройства.

Известное устройство имеет более высокую надежность, поскольку продолжает функционирование после отказов операционных блоков. Недостатком известного устройства являются большие аппаратурные затраты на реализацию средств управления и коммутации.

Целью изобретения является сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в отказоустойчивом устройстве для умножения чисел, содержащем п основных операционных блоков (п - разрядность множимого), m резервных операционных блоков (т - 1, 2, 3, ...), первую и вторую группы по (n+m) коммутаторов, коммутатор множимого и блок управления, причем вход множителя устройства соединен с входами

множителя основных и резервных операционных блоков, входы множимого m резервных операционных блоков соединены с соответствующими m выходами коммутатора множимого, информационный вход которого соединен с входом множимого устройства, первый и второй входы контроля которого соединены соответственно с первым и вторым входами блока управле0 ния, выходы отказа и прерывания которого соединены соответственно с выходами отказа и прерывания устройства, выход результата которого соединен с выходом первого коммутатора второй группы, пер5 вые выходы (n+m) коммутаторов первой

группы соединены с входами слагаемых со ответствующих п основных и m резервных

операционных блоков, выходы результата

которых соединены с первыми информаци0 онными входами соответствующих (n+m) коммутаторов второй группы, информационный вход 1-го (, .... п-1) коммутатора первой группы соединен с выходом (1+1)-го коммутатора второй группы, управляющие

5 входы J-x коммутаторов первой и второй

групп (J 1п) объединены между собой

и соединены с выходом отказа j-ro основного блока блока управления, в нем входы множимого - п основных операционных бло0 ков соединены с соответствующими п входами коммутатора множимого, информационные входы коммутаторов с п- го по (п+т-1)-й первой группы соединены с выходами коммутаторов с (п+1)-го по (п+т)-й

5 второй группы соответственно, информационный вход (n+m)-ro коммутатора первой группы соединен с входом коррекции устройства, вторые входы коммутаторов первой группы соединены с вторыми

О информационными входами соответствующих коммутаторов второй группы, управляющие входы t-x коммутаторов первой и

второй групп (t - п+1 т) объединены

между собой и соединены с выходом запре5 та блока управления и первым управляющим входом коммутатора множимого, второй управляющий вход которого соединен с выходом отказа J-ro основного блока блока управления.

0 Отказоустойчивое устройство умножения чисел содержит отличительные признаки, не обнаруженные ни в одном из известных аналогичных устройств - в нем вторые выходы коммутаторов первой груп5 пы соединены с вторыми информационными входами соответствующих коммутаторов второй группы, а входы слагаемого п основных операционных блоков соединены с соответствующими выходами коммугатора множимого. Это позволяет обеспечить работоспособность устройства с использованием л основных и резервных операционных блоков; организуя обходной путь потока информации через неисправные и неиспользуемые операционные блоки, сократив, таким образом, аппаратурные затраты на реализацию средств управления реконфигурацией и коммутацию.

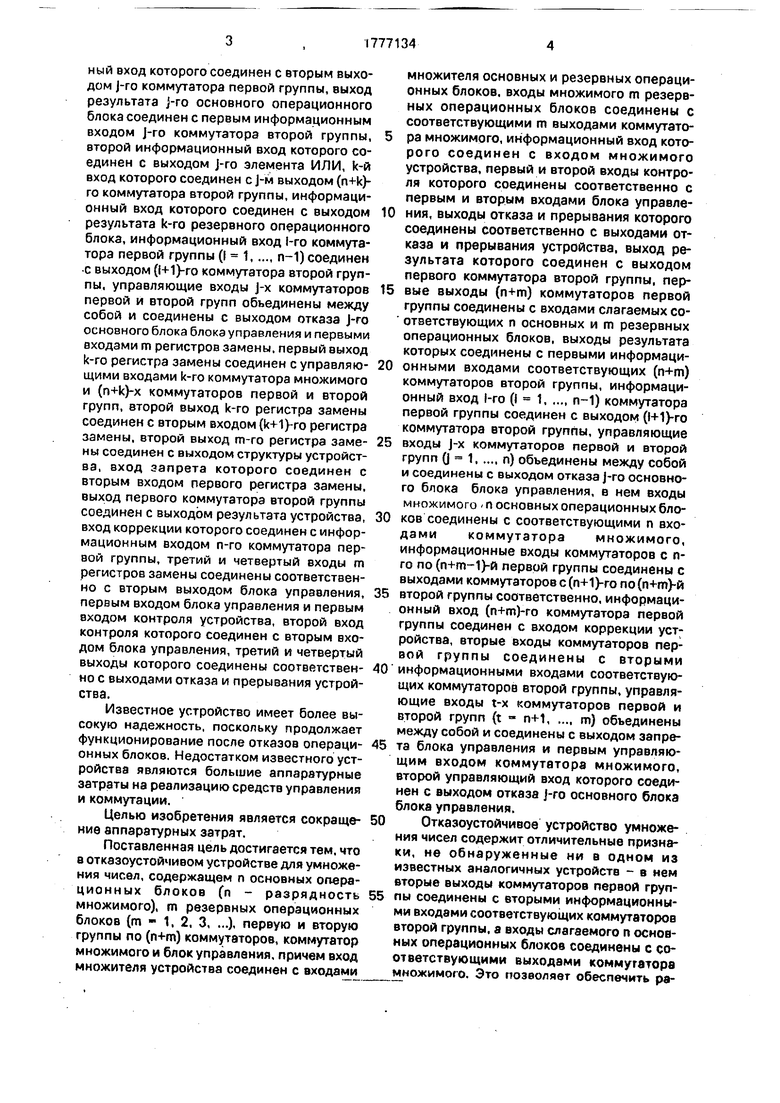

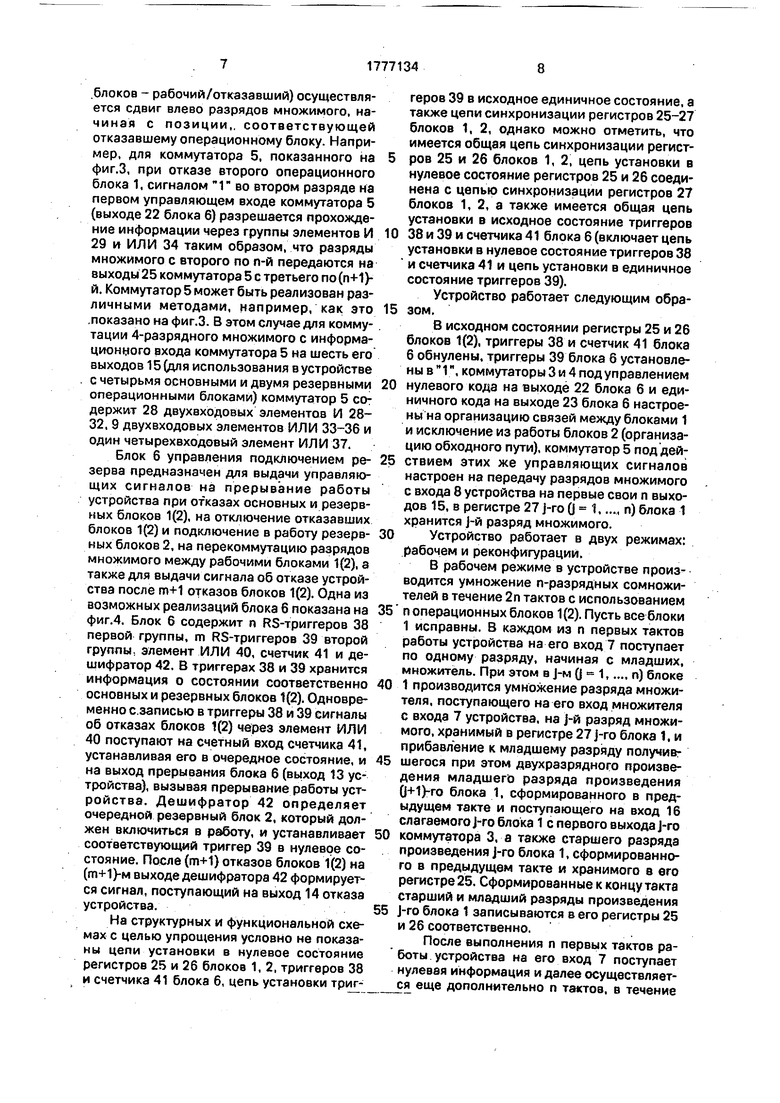

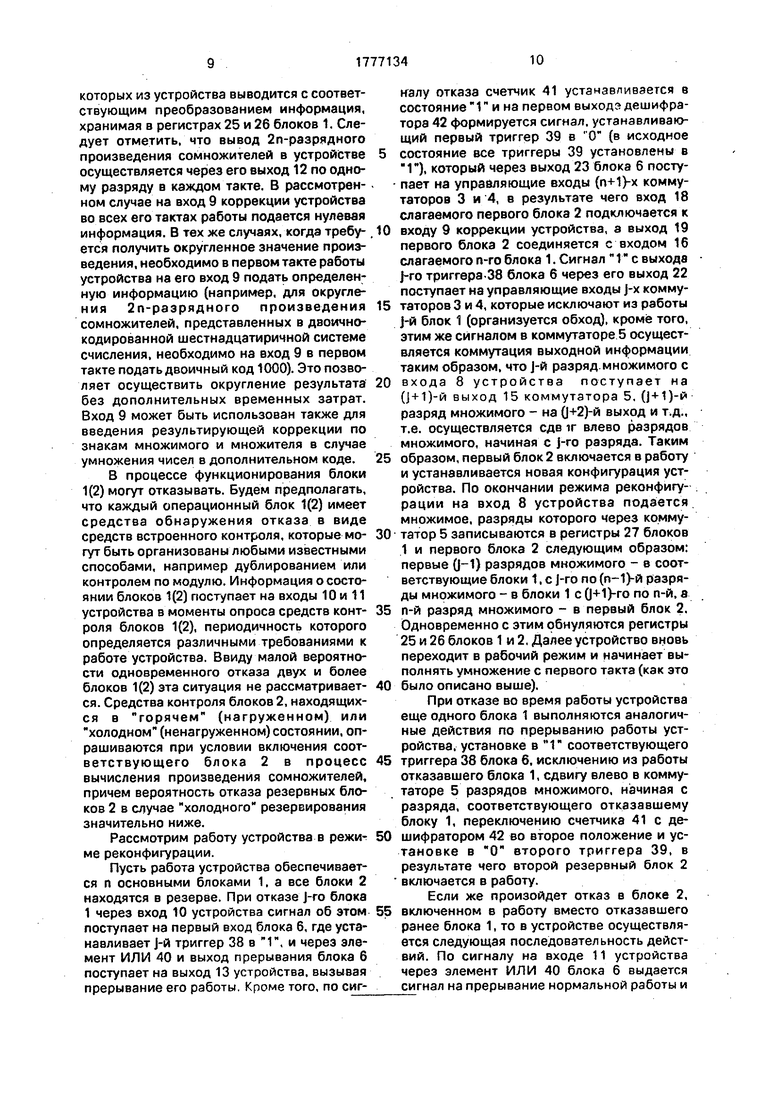

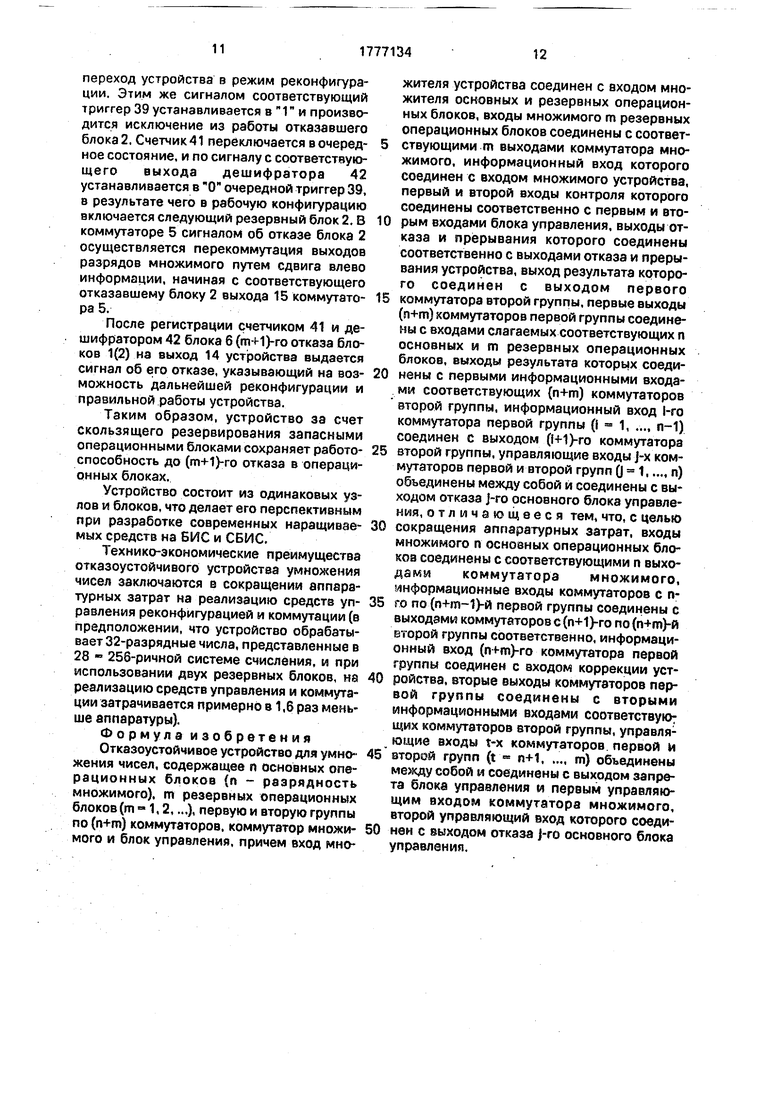

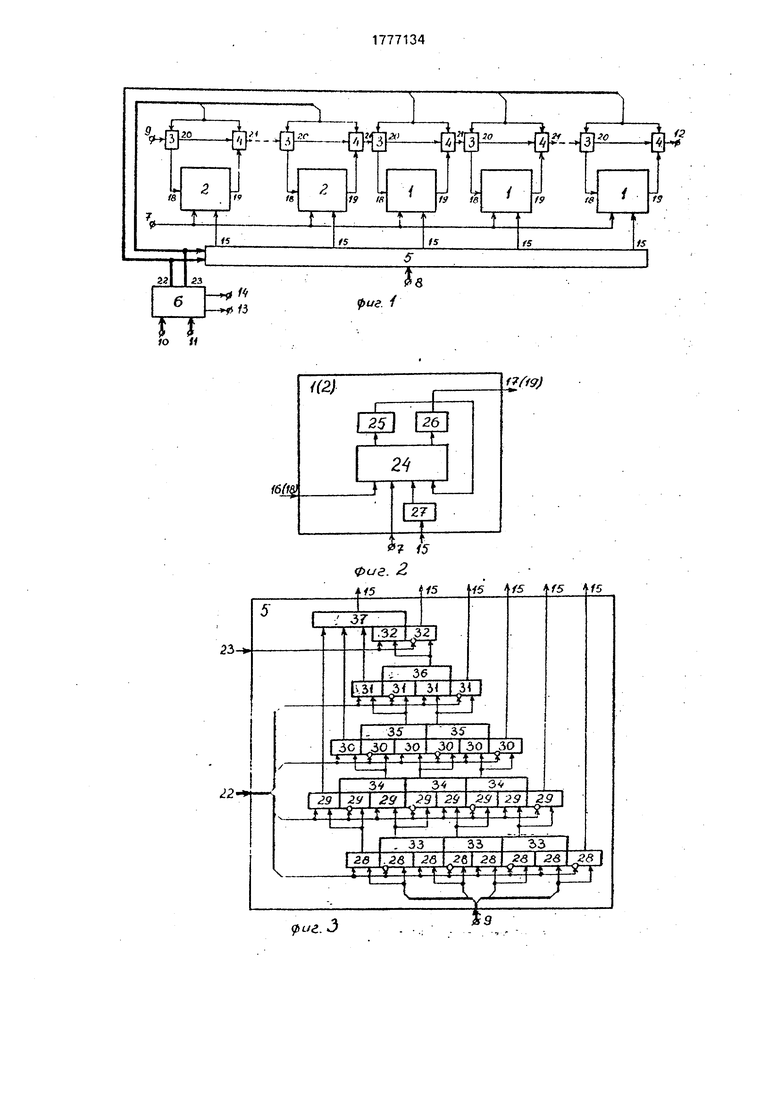

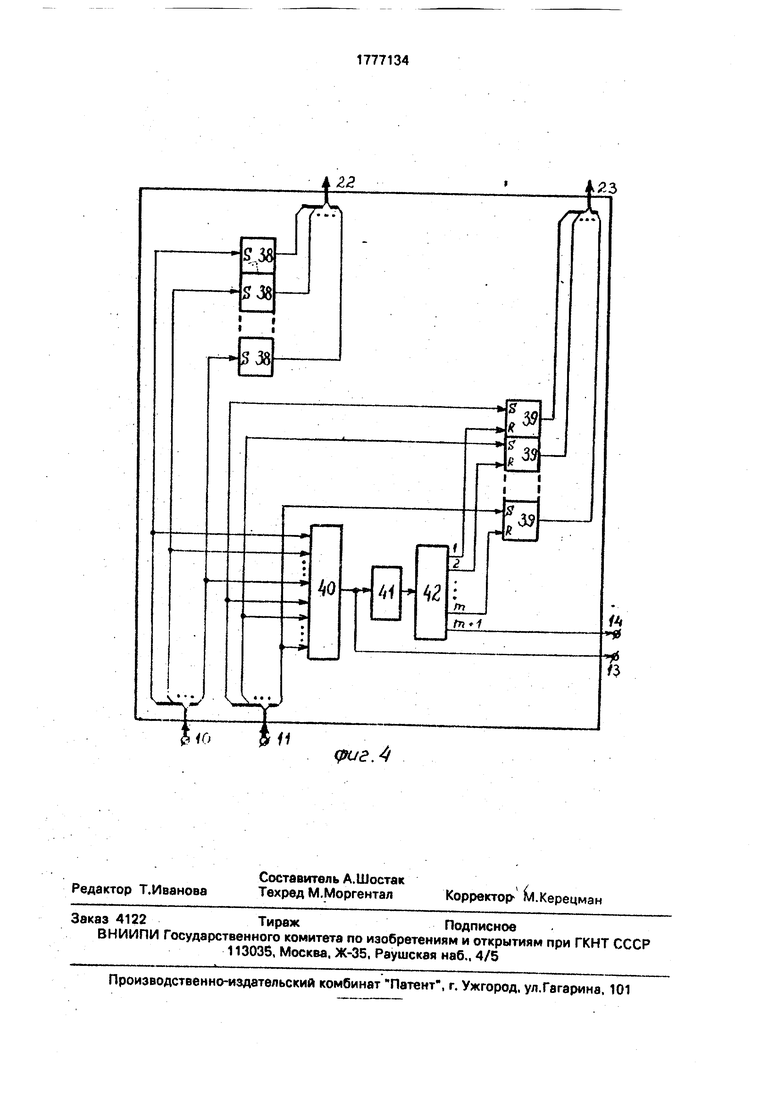

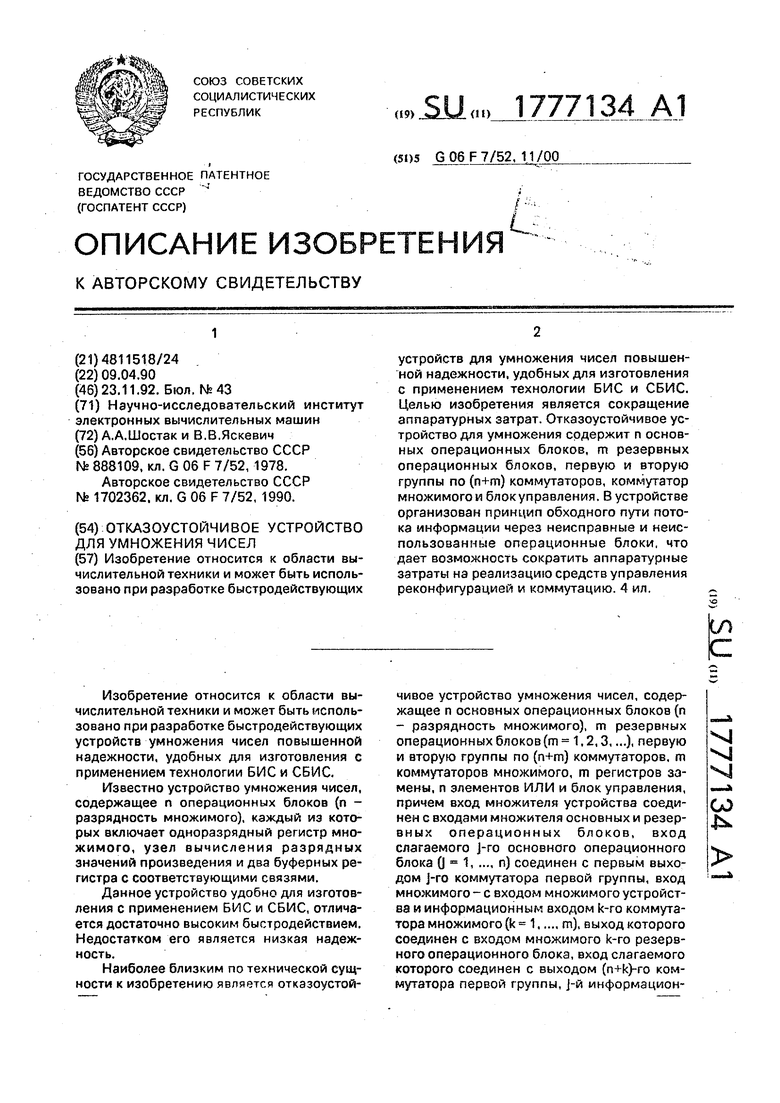

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 -структурная схема операционного блока; на фиг.З - функциональная схема коммутатора множимого для случая п 4, m 2; на фиг.4

-функциональная схема блока управления подключением резерва.

Устройство для умножения чисел (фиг.1) содержи 1 п основных операционных блоков 1 (п - число разрядов множимого) m резервных операционных блоков 2 (т 1, 2, 3...), (п+т) коммутаторов 3 первой группы, (n+m) коммутаторов 4 второй группы, коммутатор 5 множимого, блок 6 управления, входы 7 и 8 множителя и множимого устройства соответственно, вход 9 коррекции устройства, первый 10 и второй 11 входы контроля устройства, выходы 12-14 результата, прерывания и отказа устройства соответственно.

Вход множителя J-ro (j Ч п) блока 1

соединен с входом множителя k-го (к 1

т) блока 2 и входом 7 множителя устройства, вход множимого J-ro блока 1 - с j-м выходом 15 коммутатора 5, вход 16 слагаемого

-с первым выходом j-ro коммутатора 3, выход 17 результата j-ro блока 1 соединен с вторым информационным входом J-ro коммутатора 4, вход множимого k-го блока 2 соединен с (n+kj-м выходом 15 коммутатора 5, вход 18 слагаемого k-го блока 2-е первым выходом (n+k)-ro коммутатора 3, выход 19 результата k-ro блока 2 соединен с вторым информационным входом (n+k)-ro коммутатора 4, второй выход 20 1-го (1 1, .... n+m) коммутатора 3 соединен с первым информационным входом 1-го коммутатора 4, выход 21 1-го коммутатора 4 соединен с информационным входом (1-1)-го коммутатора 3, выход 21 первого коммутатора 4 соединен с выходом 12 результата устройства, вход 8 коррекции которого соединен с информационным входом (гн-т}-го коммутатора 3, управляющие входы j-x коммутаторов 3 и 4 объединены и соединены с вторым управляющим входом коммутатора 5 и выходом 22 блока б, выход 23 которого соединен с первым управляющим входом коммутатора 5 и с управляющими входами (n+k)-x коммутаторов 3 и 4, первый и второй входы блока 6 соединены с первым 10 и вторым 11 входами контроля устройства соответственно, выход прерывания блока 6 соединен с выходом 13 прерывания устройства, выход 14 отказа которого соединен с выходом отказа блока 6, вход 8 множимого устройства соединен с информационным входом коммута5 тора 5 множимого.

Рассмотрим функциональное назначение и реализацию узлов и блоков устройства.

Операционные блоки 1(2) предназначе10 ны для вычисления разрядных значений произведения и формируют на своих выходах 17(19) результата значения (ХУ + А + В) мл, где мл означает младший разряд двухразрядного результата; ХУ - соответствую5 щие разряды сомножителей, поступающих на входы множителя и множимого блоков

1(2);

А - одноразрядное слагаемое, поступающее на вход 16(18) слагаемого блоков 1(2);

0 В - внутреннее одноразрядное слагаемое, хранимое в одном из буферных регистров блоков 1(2).

Реализация блоков 1(2) показана на фиг.2. В этом случае каждый блок 1(2) содер5 жит узел 24 вычисления разрядных значений произведения, буферные регистры 25 и 26 и регистр множимого 27. В регистре 27 хранится соответствующий разряд множимого. Узел 24 формирует двухразрядные

0 значения функции F X-Y + A+B,

старшие и младшие разряды которых записываются соответственно в регистры 25 и 26. Реализация узла 24 зависит от требова5 ний к регулярности структуры и к быстродействию и может быть осуществлена известным образом. Регистры 25-27 могут быть реализованы на синхронных двухтактных D-триггерах, причем регистры 25 и 26

0 имеют входы установки в нулевое состояние.

Коммутатор 3 предназначен для выдачи информации со своего входа на первый или второй свои выходы в зависимости от управ5 ляющих сигналов. Он может быть реализован на элементах 2И.

Коммутатор 4 предназначен для передачи информации на свой выход с первого или второго своих информационных входов

0 в зависимости от управляющих сигналов. Он может быть реализован на элементах 2И-2ИЛИ.

Коммутатор 5 множимого предназначен для передачи разрядов множимого со свое5 го информационного входа (входа 8 устройства) в определенном порядке на свои выходы 15 в соответствии с управляющими сигналами. Порядок коммутации следующий; под действием управляющих сигналов (определяемых состоянием операционных

блоков - рабочий/отказавший) осуществляется сдвиг влево разрядов множимого, начиная с позиции,, соответствующей отказавшему операционному блоку. Например, для коммутатора 5, показанного на фиг.З, при отказе второго операционного блока 1, сигналом 1 во втором разряде на первом управляющем входе коммутатора 5 (выходе 22 блока 6) разрешается прохождение информации через группы элементов И 29 и ИЛИ 34 таким образом, что разряды множимого с второго по n-й передаются на выходы 25 коммутатора 5 с третьего по(п+1)- и. Коммутатор 5 может быть реализован различными методами, например, как это показано на фиг.З. В этом случае для коммутации 4-разрядного множимого с информационного входа коммутатора 5 на шесть его выходов 15 (для использования в устройстве с четырьмя основными и двумя резервными операционными блоками) коммутатор 5 содержит 28 двухвходовых элементов И 28- 32. 9 двухвходовых элементов ИЛИ 33-36 и один четырехвходовый элемент ИЛИ 37.

Блок 6 управления подключением резерва предназначен для выдачи управляющих сигналов на прерывание работы устройства при отказах основных и резервных блоков 1(2), на отключение отказавших блоков 1(2) и подключение в работу резервных блоков 2, на перекоммутацию разрядов множимого между рабочими блоками 1(2), а также для выдачи сигнала об отказе устройства после т+1 отказов блоков 1(2). Одна из возможных реализаций блока 6 показана на фиг.4. Блок 6 содержит п RS-триггеров 38 первой группы, m RS-триггеров 39 второй группы, элемент ИЛИ 40, счетчик 41 и дешифратор 42. В триггерах 38 и 39 хранится информация о состоянии соответственно основных и резервных блоков 1(2). Одновременно с записью в триггеры 38 и 39 сигналы об отказах блоков 1(2) через элемент ИЛИ 40 поступают на счетный вход счетчика 41, устанавливая его в очередное состояние, и на выход прерывания блока б (выход 13 устройства), вызывая прерывание работы устройства. Дешифратор 42 определяет очередной резервный блок 2, который должен включиться в работу, и устанавливает соответствующий триггер 39 в нулевое состояние. После (т+1) отказов блоков 1(2) на (т+1)-м выходе дешифратора 42 формируется сигнал, поступающий на выход 14 отказа устройства.

На структурных и функциональной схемах с целью упрощения условно не показаны цели установки в нулевое состояние регистров 25 и 26 блоков 1, 2, триггеров 38 и счетчика 41 блока б, цепь установки триггеров 39 в исходное единичное состояние, а также цепи синхронизации регистров 25-27 блоков 1, 2, однако можно отметить, что имеется общая цепь синхронизации регистров 25 и 26 блоков 1, 2, цепь установки в нулевое состояние регистров 25 и 26 соединена с цепью синхронизации регистров 27 блоков 1, 2, а также имеется общая цепь установки в исходное состояние триггеров

0 38 и 39 и счетчика 41 блока 6 (включает цепь установки в нулевое состояние триггеров 38 и счетчика 41 и цепь установки в единичное состояние триггеров 39).

Устройство работает следующим обра5 зом,

В исходном состоянии регистры 25 и 26 блоков 1(2), триггеры 38 и счетчик 41 блока 6 обнулены, триггеры 39 блока 6 установлены в 1, коммутаторы 3 и 4 под управлением

0 нулевого кода на выходе 22 блока 6 и единичного кода на выходе 23 блока 6 настроены на организацию связей между блоками 1 и исключение из работы блоков 2 (организацию обходного пути), коммутатор 5 под дей5 ствием этих же управляющих сигналов настроен на передачу разрядов множимого с входа 8 устройства на первые свои п выходов 15, в регистре 27 j-го (j 1п) блока 1

хранится j-й разряд множимого.

0 Устройство работает в двух режимах: рабочем и реконфигурации.

В рабочем режиме в устройстве производится умножение n-разрядных сомножителей в течение 2л тактов с использованием

5 п операционных блоков 1(2). Пусть все блоки 1 исправны. В каждом из п первых тактов работы устройства на его вход 7 поступает по одному разряду, начиная с младших, множитель. При этом в J-м (j 1,.... п) блоке

0 1 производится умножение разряда множителя, поступающего на его вход множителя с входа 7 устройства, на j-й разряд множимого, хранимый в регистре 27 j-ro блока 1, и прибавление к младшему разряду получив5 шегося при этом двухразрядного произведения младшего разряда произведения 0+1}-го блока 1, сформированного в предыдущем такте и поступающего на вход 16 слагаемого j-ro блока 1 с первого выхода J-ro

0 коммутатора 3, а также старшего разряда произведения j-ro блока 1, сформированного в предыдущем такте и хранимого в его регистре 25, Сформированные к концу такта старший и младший разряды произведения

5 j-ro блока 1 записываются в его регистры 25 и 26 соответственно.

После выполнения л первых тактов работы устройства на его вход 7 поступает нулевая информация и далее осуществляется еще дополнительно п тактов, в течение

которых из устройства выводится с соответствующим преобразованием информация, хранимая в регистрах 25 и 26 блоков 1. Следует отметить, что вывод 2п-разрядного произведения сомножителей в устройстве осуществляется через его выход 12 по одному разряду в каждом такте. В рассмотренном случае на вход 9 коррекции устройства во всех его тактах работы подается нулевая информация. В тех же случаях, когда требуется получить округленное значение произведения, необходимо в первом такте работы устройства на его вход 9 подать определенную информацию (например, для округления 2п-разрядного произведения сомножителей, представленных в двоично- кодированной шестнадцатиричной системе счисления, необходимо на вход 9 в первом такте подать двоичный код 1000). Это позволяет осуществить округление результата без дополнительных временных затрат. Вход 9 может быть использован также для введения результирующей коррекции по знакам множимого и множителя в случае умножения чисел в дополнительном коде.

В процессе функционирования блоки 1(2) могут отказывать. Будем предполагать, что каждый операционный блок 1(2) имеет средства обнаружения отказа в виде средств встроенного контроля, которые могут быть организованы любыми известными способами, например дублированием или контролем по модулю. Информация о состоянии блоков 1(2) поступает на входы 10 и 11 устройства в моменты опроса средств контроля блоков 1(2), периодичность которого определяется различными требованиями к работе устройства. Ввиду малой вероятности одновременного отказа двух и более блоков 1(2) эта ситуация не рассматривается. Средства контроля блоков 2, находящихся в горячем (нагруженном) или холодном (ненагруженном) состоянии, опрашиваются при условии включения соответствующего блока 2 в процесс вычисления произведения сомножителей, причем вероятность отказа резервных блоков 2 в случае холодного резервирования значительно ниже.

Рассмотрим работу устройства в режиме реконфигурации.

Пусть работа устройства обеспечивается п основными блоками 1, а все блоки 2 находятся в резерве. При отказе J-ro блока 1 через вход 10 устройства сигнал об этом поступает на первый вход блока 6, где устанавливает J-й триггер 38 в Г, и через элемент ИЛИ 40 и выход прерывания блока 6 поступает на выход 13 устройства, вызывая прерывание его работы. Кроме того, по сигкалу отказа счетчик 41 устанавливается в состояние 1 и на первом выходэ дешифратора 42 формируется сигнал, устанавливающий первый триггер 39 в О (в исходное

5 состояние все триггеры 39 установлены в Г), который через выход 23 блока б посту- пает на управляющие входы ( коммутаторов 3 и 4, в результате чего вход 18 слагаемого первого блока 2 подключается к 0 входу 9 коррекции устройства, а выход 19 первого блока 2 соединяется с входом 16 слагаемого n-го блока 1. Сигнал 1 с выхода j-ro триггера.38 блока 6 через его выход 22 поступает на управляющие входы J-x комму5 таторов 3 и 4, которые исключают из работы j-й блок 1 (организуется обход), кроме того, этим же сигналом в коммутаторе 5 осуществляется коммутация выходной информации таким образом, что J-й разряд множимого с

0 входа 8 устройства поступает на

0+ 1)-й выход 15 коммутатора 5, ( + 1)-й разряд множимого - на (|+2)-й выход и т.д., т.е. осуществляется сдв ir влево разрядов множимого, начиная с j-ro разряда. Таким

5 образом, первый блок 2 включается в работу и устанавливается новая конфигурация устройства. По окончании режима реконфигурации на вход 8 устройства подается множимое, разряды которого через комму0 татор 5 записываются в регистры 27 блоков

1и первого блока 2 следующим образом: первые ()1) разрядов множимого - в соответствующие блоки 1, с J-ro по (п-1)-й разряды множимого - в блоки 1 с (J-M)-ro по n-й, а

5 n-й разряд множимого - в первый блок 2. Одновременно с этим обнуляются регистры 25 и 26 блоков 1 и 2, Далее устройство вновь переходит в рабочий режим и начинает выполнять умножение с первого такта (как это

0 было описано выше).

При отказе во время работы устройства еще одного блока 1 выполняются аналогичные действия по прерыванию работы устройства, установке в Г соответствующего

5 триггера 38 блока 6, исключению из работы отказавшего блока 1, сдвигу влево в коммутаторе 5 разрядов множимого, начиная с разряда, соответствующего отказавшему блоку 1, переключению счетчика 41 с де0 шифратором 42 во второе положение и установке в О второго триггера 39, в результате чего второй резервный блок 2 включается в работу.

Если же произойдет отказ в блоке 2,

5 включенном в работу вместо отказавшего ранее блока 1, то в устройстве осуществляется следующая последовательность действий. По сигналу на входе 11 устройства через элемент ИЛИ 40 блока 6 выдается сигнал на прерывание нормальной работы и

переход устройства в режим реконфигурации. Этим же сигналом соответствующий триггер 39 устанавливается в 1 и производится исключение из работы отказавшего блока 2. Счетчик 41 переключается в очередное состояние, и по сигналу с соответствующего выхода дешифратора 42 устанавливается в 0й очередной триггер 39, в результате чего в рабочую конфигурацию включается следующий резервный блок 2. В коммутаторе 5 сигналом об отказе блока 2 осуществляется перекоммутация выходов разрядов множимого путем сдвига влево информации, начиная с соответствующего отказавшему блоку 2 выхода 15 коммутатора 5.

После регистрации счетчиком 41 и дешифратором 42 блока б (m+1)-ro отказа блоков 1(2) на выход 14 устройства выдается сигнал об его отказе, указывающий на возможность дальнейшей реконфигурации и правильной работы устройства.

Таким образом, устройство за счет скользящего резервирования запасными операционными блоками сохраняет работоспособность до (m+1)-ro отказа в операционных блоках.

Устройство состоит из одинаковых узлов и блоков, что делает его перспективным при разработке современных наращиваемых средств на БИС и СБИС.

Технико-экономические преимущества отказоустойчивого устройства умножения чисел заключаются в сокращении аппаратурных затрат на реализацию средств управления реконфигурацией и коммутации (в предположении, что устройство обрабатывает 32-разрядные числа, представленные в 28 256-ричной системе счисления, и при использовании двух резервных блоков, на реализацию средств управления и коммутации затрачивается примерно в 1,6 раз меньше аппаратуры).

Формула изобретения

Отказоустойчивое устройство для умножения чисел, содержащее п основных операционных блоков {п - разрядность множимого), m резервных операционных блоков (т «1,2,...), первую и вторую группы по (n+m) коммутаторов, коммутатор множимого и блок управления, причем вход множителя устройства соединен с входом множителя основных и резервных операционных блоков, входы множимого m резервных операционных блоков соединены с соответствующими m выходами коммутатора множимого, информационный вход которого соединен с входом множимого устройства, первый и второй входы контроля которого соединены соответственно с первым и вторым входами блока управления, выходы отказа и прерывания которого соединены соответственно с выходами отказа и прерывания устройства, выход результата которого соединен с выходом первого

коммутатора второй группы, первые выходы (n+m) коммутаторов первой группы соединены с входами слагаемых соответствующих п основных и m резервных операционных блоков, выходы результата которых соединены с первыми информационными входами соответствующих (n+m) коммутаторов второй группы, информационный вход 1-го коммутатора первой группы (1-1, .... п-1) соединен с выходом (1+1)-го коммутатора

второй группы, управляющие входы j-x коммутаторов первой и второй групп 0 1,..., п) объединены между собой и соединены с выходом отказа j-ro основного блока управления, отличающееся тем, что, с целью

сокращения аппаратурных затрат, входы множимого п основных операционных блоков соединены с соответствующими п выхода мм коммутатора множимого, информационные входы коммутаторов с пго по (п+т-1)-й первой группы соединены с выходами коммутаторов с (п+1)-го по (п+т)-й второй группы соответственно, информационный вход (n+m)-ro коммутатора первой группы соединен с входом коррекции устройства, вторые выходы коммутаторов первой группы соединены с вторыми информационными входами соответствую: щих коммутаторов второй группы, управляющие входы t-x коммутаторов первой и

второй групп (t n+1, ..., т) объединены между собой и соединены с выходом запрета блока управления и первым управляющим входом коммутатора множимого, второй управляющий вход которого соединем с выходом отказа j-ro основного блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1990 |

|

SU1789981A1 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1991 |

|

RU2021631C1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Устройство для умножения чисел | 1988 |

|

SU1536374A1 |

| Устройство для умножения | 1988 |

|

SU1529215A1 |

Изобретение относится к области вычислительной техники и может быть использовано при разработке быстродействующих устройств для умножения чисел повышенной надежности, удобных для изготовления с применением технологии БИС и СБИС. Целью изобретения является сокращение аппаратурных затрат. Отказоустойчивое устройство для умножения содержит п основных операционных блоков, m резервных операционных блоков, первую и вторую группы по (n+m) коммутаторов, коммутатор множимого и блокуправления. В устройстве организован принцип обходного пути потока информации через неисправные и неиспользованные операционные блоки, что дает возможность сократить аппаратурные затраты на реализацию средств управления реконфигурацией и коммутацию. 4 ил.

. 3

Фиг. 2,

Z2

11

Фиг.4

123

| Устройство для умножения | 1978 |

|

SU888109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1990 |

|

SU1702362A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-11-23—Публикация

1990-04-09—Подача