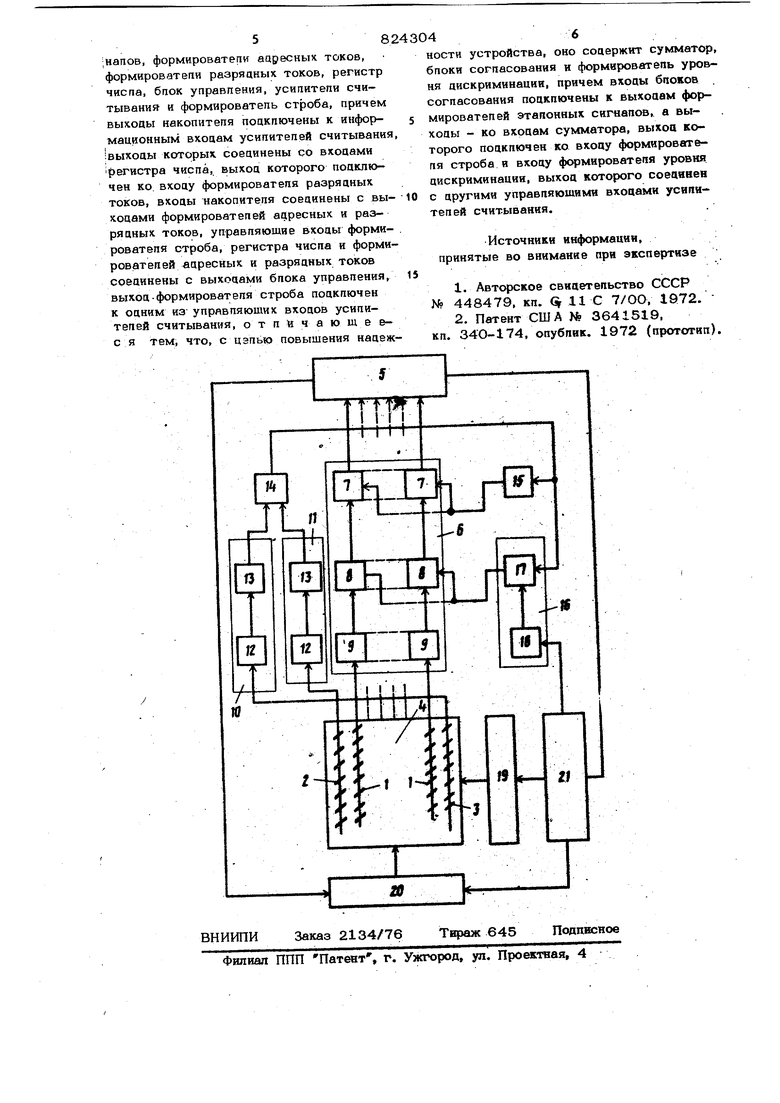

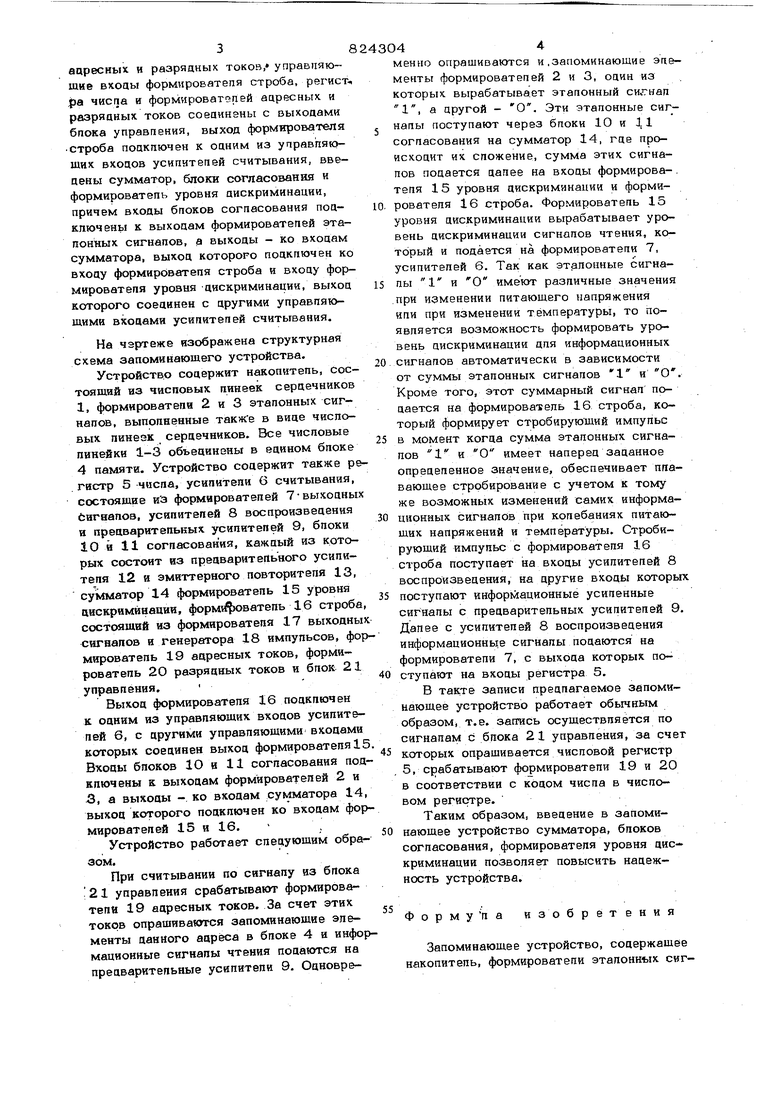

Изобретенве отнс :ится к запоминающим устройствам. Известно устройство, соаержашее накопитель, соецияенный с формирсеатепяма аоресных н раэряцных , вхоаь кстсфых по11кпю4ены к выкоаам чиспового регшггра, а выхооы чиспового регвстра соеаинеяы с выходами формировагтепей и блоком, управпення, усипитепи .считывания, соединенные с генератором строба lj Недостаток устройства в том, что в нем отсутствуют бпо&и и эпементы, пбзврпяюшие повысить ннфо{ ааиовиую надежность устройства за счет орга ннзации автоматического измерения времени стробироваиня и уровня дискриминации. Наиболее близким техническим решением к данному изобретению является запоминающее устройство, содержащее накопитель, подключенный к формирователям токов и усилителям .считывания, соединенным с регистром числа и 4 ормироватепем строба, управл.яемым от формирователей эталонных сигналов 21. Однако в этом устройстве не предусмотрено автоматическое изменение уровня дискриминации при изменении условий считывания (уровня -напряжения питания, температуры и т.п.), что снижает надежность, устройства. . Цепь изобретения - повышение надежности устройства. Поставленная цель достигается тем, что -в запоминающее устройство, содержащее накопитель, формирователи эта- лонных сигналов, формирователи адресных токов, формирователи разрядных токов, регистр числа, блок управления, усилители считывания и формирователь строба, причем выходы накопителя подключены к информационным входам усилителей считывания, выходы которых соединены со входами регистра числа, выход которого подключен ко входу формирователя разрядных токов, входы накопителя соединены с выходами формирователей ацресных и разрядных токов, управпяюшие вхоаь фopмvIpoвaтeпя строба, регист jpa чис11а и форшфоватопей адресных и разрядных токов соединены с выходами бпока управпения, выход формирователя строба подключен к одним из управляющих входов усиаитепей считывания, введены сумматор, блоки согласования и формироватепь уровня дискриминации, причем входы бпоков согласования подкпючены к выходам формирователей этапонных сигналов, а выходы - ко входам сумматора, выхоа которого подключен ко входу формирователя строба и входу фор- мироватепя уровня -дискриминации, выход которого соединен с другими управляющими входами усипитепей считывания. На чзртеже изображена структурная схема запоминающего устройства. Устройство содержит накопитель, состоящий из чисповых пинеек сердечников 1, формироватепи 2 и 3 эталонных сигналов, выпогененные такясе в виде числовых пинеэк сердечников. Все числовые пинейки 1-3 объецинйны в едином блоке 4 памяти. Устройство соаержит также ре гистр 5 числа, усилители 6 считывания, состоящие из формирователей 7-выходных бигнапов, усипитепей 8 воспроизведения и предваритепьнык усилителей 9. блоки 10 и 11 согпасования, каждый из которых состоит из предваритепьного усилителя 12 и эмиттерного повторителя 13, сумматор 14 формирователь 15 уровня цнскримйнации, форм фоватвль 16 строба состоящий из фсфмироватепя 17 выходны сигнапов и генератора 18 импупьсов, фо мирователь 19 адресных токов, формироватепь 20 разрядных токов и блок 21 управпения, Выход формирователя 16 подключен к одним из управляющих входов усилителей 6, с другими управляющими входами которых соединен выход формирователя 15 Вхоаы блоков 10 и 11 согласования под ключены к выходам формирователей 2 и 3, а выходы - ко входам сумматора 14 выход которого подключен ко входам фор мирователей 15 и 16. . Устройство работает следующим образом. При считывании по сигналу из бпока 21 управления срабатывают формирователи 19 адресных токов. За счет этик токов опрашиваются запоминающие элементы данного адреса в блоке 4 и инфор мационные сигналы чтения подаются на предварительные усилители 9. Одновременно опрашиваются и .запоминающие элементы формирователей 2 и 3, один из которых вырабатывает эталонный 1, а другой - О. Эти эталонные сигналы поступают через бпоки 10 и 11 согласования на сумматор 14, где происходит их сложение, сумма этих сигнапов подается далее на входы формирова-. теля 15 уровня дискриминации и формирователя 16 строба. Формирователь 15 уровня дискриминации вырабатывает уровень дискриминации сигналов чтения, который и подается на формирователи 7, усилителей 6. Так как эталонные сигна- пы 1 и О имеют различные значения при изменении питающего напряжения или при изменении температуры, то появляется возможность формировать уровень дискриминации для информационных сигналов автоматически в зависимости от суммы эталонных сигналов 1 и О. Кроме того, этот суммарный сигнал подается на формироватгель 16 строба, который формирует стробирующий импульс в момент когда сумма этапонных сигнапов 1 и О имеет наперед заданное определенное значение, обеспечивает плавающее стробирование с учетом к тому же возможных изменений самих информационных сигналов при колебаниях питающих напряжений и температуры. Стробирующий импульс с формирователя 16 строба поступает на входы усилителей 8 воспроизведения, на другие входы которых поступают инфорглационные усиленные сигналы с предварительных усилителей 9. Далее с усилителей 8 воспроизведения информационнь1е сигналы подаются на формирователи 7, с выхода которых поступают на входы регистра 5. В такте записи предлагаемое запоминающее устройство работает обычным образом, т.е. запись осуществляется по сигналам с бпока 21 управпения, за счет которых опрашивается числовой регистр 5, срабатывают формирователи 19 и 20 в соответствии с кодом числа в числовом регистре. Таким образом, введение в запоминающее устройство сумматора, блоков согласования, формирователя уровня дискриминации позволяет повысить надежность устройства. Формул а изобретения Запоминающее устройство, содержащее накопитель, формироватепи эталонных сиг

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с автономным контролем | 1982 |

|

SU1037349A1 |

| Усилитель считывания для оптоэлектронногозАпОМиНАющЕгО уСТРОйСТВА | 1979 |

|

SU824303A1 |

| Устройство для контроля матриц памяти | 1980 |

|

SU898507A1 |

| "Запоминающее устройство | 1979 |

|

SU809369A1 |

| Блок считывания информации для доменного запоминающего устройства | 1980 |

|

SU930381A1 |

| Запоминающее устройство | 1981 |

|

SU982093A1 |

| Устройство для индицирования двигателя внутреннего сгорания | 1982 |

|

SU1052900A1 |

| Устройство для считывания информации из накопителя | 1980 |

|

SU864334A1 |

| Запоминающее устройство | 1982 |

|

SU1049969A1 |

| Модуль доменной памяти | 1988 |

|

SU1617457A1 |

Авторы

Даты

1981-04-23—Публикация

1979-06-19—Подача