вен1Ю к выходам считывания второго и третьего усилителей, вхоаы записи которых и выход третьегхэ элемента ИЛИ соединены соответственно с вторым выходом и четвертым входом блока ввода и вывода информации, третий выход генератора сигналов подключен к входу второго формирователя сигналов, а второй вход - к выходу четвертого элемента ИЛИ, первый вход которого соединен с выходом сдвигового регистра, первый и

10

349

второй в коды которого подключены соответственно к первому входу генератора сигналов и второму выходу блока сравнения, третий выход которого и второй ВХОД четвертого элемента ИЛИ соединены соответственно с третьим входом и ойним из выходов счетчика импульсов, другие выходы которого подключены к одним из входов первого коммутатора, другие входы которого являются адресными входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Оперативное запоминающее устройство с самоконтролем | 1985 |

|

SU1300569A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Оперативное запоминающее устройство с самоконтролем | 1985 |

|

SU1317485A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

ОПЕРАТОВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ, содержащее основной адрео ный накопитель, дешифраторы, усйпитепи, бпок сравнения, блок управления,блок ввода и вывода информации, счетчик импульсов, генератор сигнадюв, формирователи сигйалов и элементы ИЛИ, причем выходр первого дешифратора подклкчень к входам первого усилителя, выходы котор(го соединены с одними из входов ос но ного адресного накопителя, другие входы и выходы которого подключены соответственно к адресным выходам и одним из адресных входов второго усилителя, другие адресные вхошл которотю соединены с выходами второго , упра&ляюшие входы дешифраторов и усилителей подключены к выходам блока управления, первые выходы первого и второго формирователей сигналов соедннены соответс вен1ю с первыми входами первого и второго элементов ИЛИ, выходы которых подключены соответственно к первым и вто,рым вхсч7Я1м блока ввода и вывода внфор мации, первый выход которого соединен с первым входом блока сравнения, второй вход которого подключен к- второму выходу первого формирователя сигналов, а третий вход - к второму выходу вгорого формирователя сигналов, третий выход которого соединен с первым входом первого формирователя сигналов, второй вход которого подключен к первому- выходу генератора сигналов, второй выход которого соединен с первым входом счетчика импульсов, второй вход которого и первый вход генератора сигналов объедиие.ны и являются установочным входом устройства, первым и вторым управляющими входами которого являются вторые входы первого i и второго элементов И, а информационным входом устройства является третий вход W блока .ввода и вывода информации, отличающееся тем, что, с целью Повышения надежности устройства, в него. введены ассоциативный накопитель, допогм нитепьный адресный накопитель, коммутаторы, третий усилитель, сдвиговый ре- гистр, третий и четвертый элементы ИЛИ, причем одни из выходов первого коммутатора соединены с входами первого дешифСА: ратора, а другие - с входами второго дешифратора и входами ассоци-. DO ативного накопителя, управляющий вход которого подключен к первому выходу ;О блока сравнения, а выходы - к входам второго коммутатора, выходы которого соединены с одними из адресных входов третьего усшитетш, другие адресные входы и адресные выходы которогр подключены к выходам и одним из входов дополнительного адресного накопителя,. другие входы которого соединены с выходами первого усилителя, входы треть;его элемента ИЛИ подключены соответст

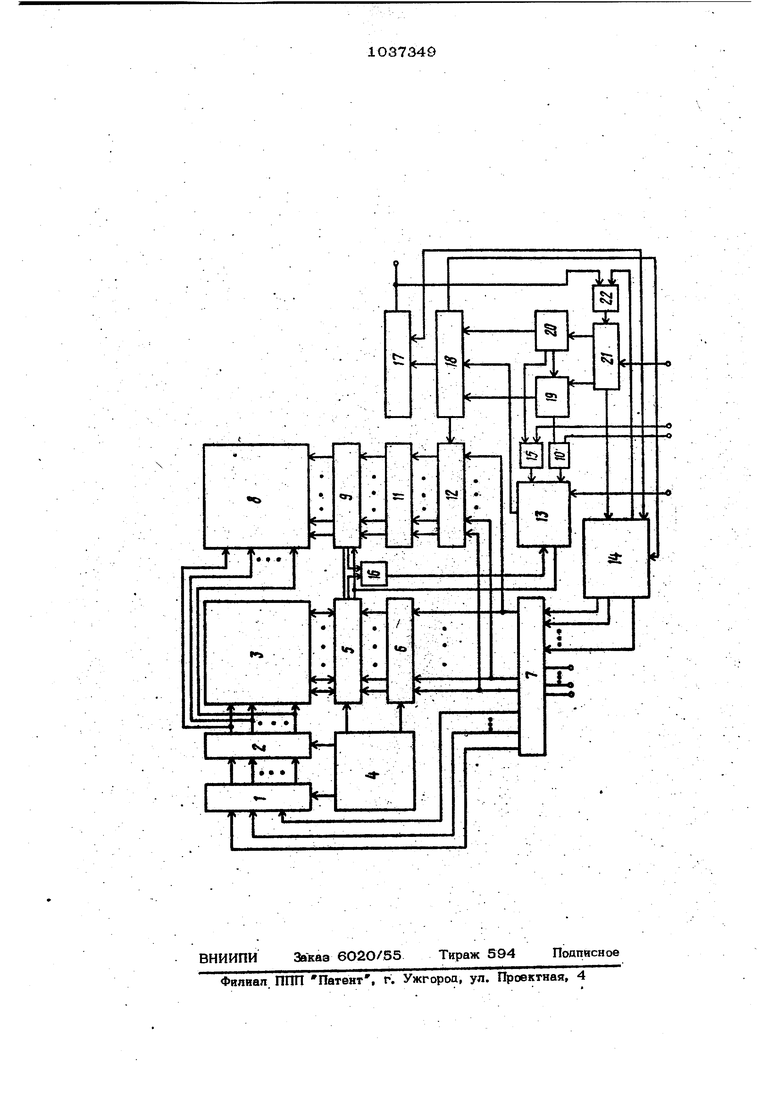

Изобретение относится к вычисплтепьгной технике, в частности к запоминающиц устройствам, и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении. Известно оперативное запоминающее устройство с автономным контролем, которое содержит накопитель, адресные и разрядные формирователи, дешифраторы, тактощ 1й генератор, генератор тестовых последовательностей и схему сравнения Недостатками этого устройства являются большие аппаратурные затраты и низкая эффективность контроля, Наиболее близким техническим; решением к изобретению является оперативное запоминающее устройство с автономным контролем, содержащее накопитель, дешиф раторы, усилители, блок управления, блок ввода и вывода, счетчик, генератор, блок сравнения, формирователи импульсов и апементы ИЛИ. Выходы первого дешифра- тора подключены к входам первого усилителя, выходы которого соединены с входами накопителя, другие входы которого соединены с выходами второго усилитепя, входы которого подключены к выходам BTOpoixi дешифратора, управпяк ший вход которого соединен с первым выходом бпока управления,другие выходы которого подключены соответственно к управляющим входам первого дешифратора, первого и второго усилителя. Первый вход блока ввода и вывода соединен с выходом первого элемента ИЛИ, второй вход соединен с выходом второго эпемвнч та ИЛИ, а выход подключен к первому входу бпока сравнения, второй вход .которого соединен с первым выходом пе{ Ього формирователя импульюов, второй выход которого соединен с вторым входом первого элемента ИЛИ, первый вход которого является первым внешним входом устройства. Третий вход блока сравнения подключен к третьему выходу второго формирователя импульсов, первый выход которого соединен с вторым входом второго элемента ИЛИ, первый вход которого является вторым внешним. входом устройства. Третий вход блока сравнения подключен к третьему выходу второго формирователя импульсов, первый выход которого подключен к второму входу второго элемента ИЛИ, первый вход которого является вторым внешним входом устройства. Второй выход второго форнмирователя импульсов подключен к первому входу первого формирователя импульсов, второй вход которого соединен с вторым выходом генератора, второй выход которого соединен с первым входом счетчика, а первый вход соединен с вторым входом счетчика и третьим внешним входом устройства 2 . Недостатком известного устройс 1за является низкая эффективность контроля, обусловленная отбраковкой микросхем после выявления первого же неисправного элемента памяти, что снижает надежность устройства. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в оперативное запоминающее устройство с автономным контролем, содержащее основной адресный накопитель, дешифраторы, усипнтепи, блок сравнения, 1блок управления, блок ввода и вывода ин310формации, счетчик импупьсов, генератор сигнадов, формирователи сигнапов и эпе . менты ИЛИ, причем выходы первого дешифратора подключены к входам первого усипитепя, выходы которого соединены с одними из.входов, основного адресного накопитепя, другие входы и выходы которого подключены соответственно к адресным выходам и одним из адресных входов второго усипитепя, другие адресные входы которого соединены с выходами второго дешифратора, управляющие входы дешифра торов и усилителей подключен к выходам блока управления, первые выходы первого и второго формирователей сигналов соеди нены соответственно с первыми входами первого и второго элементов ИЛИ, въгходы которых подключены соответственно к первым и вторым входам блока ввода и вывода информации, первый выход крторого соединен с первым входом блока сраЕ нения, второй вход которого подключен к второму выходу первого формирователя сигналов, а третий вход - к второму выходу второго формирователя сигналов третий выход которого соединен с первым входом первого формирователя сигналов, второй вход которого подключен к первому выходу генератора сигналов, второй выход которого соединен с первым входом счетчика импульсов, второй вход которого И первый вход генератора сигналов объединены и являются установочным входом устройства, первым и вторым управляющими входами которого являются вторые входы первого и второго элементов И, а информационным входом устройства является третий .вход блока ввода и вывода информации, введены ассоциативный накопитель, дополнительный адресный накопитель, коммутаторы, третий усилитель, сдвшх вый регистр, третий и четвертый элементы ИЛИ, причем одни из выходов первого коммутатора соединены с входами первого дешифратора, а другие выходы - с входами второго дешифратора и входами ассоциативного накопителя, управляющий вход которого подключен к первому выходу блока1 сравнения, а выходык входам второго коммутатора, выходы которого соединены с одними из адресных входов третьего усилителя, другие адресные входы и адресные выходы которого подключены к выходам и одним из входов дополнительногю адресного накопитепя, другие входы которого соединены с выходами первогю усилитеття, входы третьего элемента ИЛИ подключены соответственно к выходам считывания вто494рого и третьего уснпителей, входы aamicu которых и выход третьего элемента ИЛИ соединены соответственно с вторым выхо-. дом и четвертым входом блока ввода и вывода информации, третий выход генератора сигналов подключен к входу второгмэ формирователя сигналов, а второй входк выходу четвертого элемента ИЛИ, первый вход которого соединен с выходом сдвигового регистра, первый и второй входы которого подключены соответственно к первому входу генератора сигналов и к второму выходу блока сравнения, третий выход которого и второй вход четвертого элемента. ИЛИ соединены соответственно с третьим входом и одним из выходов счетчика импупьсов, другие выходы которого подключены к одним из входов первого коммутатора, другие входы которого являются адресными входами устройства. На чертеже .приведена функциональная схема предлагаемого устройства. Устройство содержит первый дешифратор 1,. первый усилитель 2, основной адресный накопитель 3, блок 4 управления, второй усилитель 5, второй дешифратор 6, первый коммутатор 7, дополнительный адресный накопитель 8, третий усилитель 9, первый элемент ИЛИ 10, второй коммутатор 11, ассоциативный накопитель 12, блок 13 ввода и вывода информации, счетчик 14 импульсов, второй 15 и третий 16 элементы ИЛИ, сдвиговый регистр 17, блок 18 сравнения, первый 19 и второй 20 формирователи, сигналов, генератор 21 сигналов и четвертый элемент . ИЛИ 22. Устройство работает следующим образом. Внешним сигналом Автоном, поступающим на установочный вход устройства, устанавливаются в начальное состояние счетчик 14, регистр 17 и запускается генератор 21..Счетчик 14 и формирователи 19 и 20, управляемые выходными сигналами генератора 21, обеспечивают работу устройства в режиме проверки работоспособности ячеек памяти накопите ля 3, причем счетчик 14 обеспечивает последоватеяьный перебор ячеек памяти при тестировании, формирователь 19 вь1рабатывает внутренние сигналы Запись /считывание а формирователь 20 вырабатывает внутренние сигналы. Элементы ИЛИ 15 и 16, а также коммутатор 7 управляют поступлением на дешифраторы 1 и б и бпок 13 сигналов пибо с внеш51них . входов устройства, пибо с выходов внутренних блоков. Выбор функционального теста, реализуемого на основе перечисленных блоков, определяется в первую очередь особенностя л1 технологического процесса, а та же емкостью накопителей, мощностными и временными параметрами устройства. Пусть в качестве функционального тео та выбран тест Последовательная запись считывание. В ходе тестирования считываемая информация поступает из блока 13 в блок 18, где ,она сравнивается с истинной информацией. Если блок 18 вырабатывает сигнал совпадения, то по прихдйу следующего сигнала с выхода генератора 21 счетчик 14 формирует адрес следующего элемента памяти накопителя 3. Если считываемая информаци нв совпадает с истинной, блок 18 выра ты.вает сигнал Ошибка, поступающий на регистр 17, счетчик 14 и накопитель 12. Этим сигналом производится запись адреса неисправного элемента памяти накопителя 3 в строку ассоциативных элементов памяти накопители 12, которо му соответствует элемент памяти накопителя В. Адрес очередного проверяемого элемента памяти поступает как на входы дешифраторов 1 и 6, так и на входы накопитепя 12, где сравнивается одновременно со всеми хранимыми адресами неисправных элементов памяти. При совпадении адресов коммутатор 11 выбирает соответствующий Резервный элемент памяти из накопителя ,8 дпя считывания или записи. Для проверки работоспособности элементов памяти накопителя -8 сигнал Ошибка блокирует счетчик 14 на время, необходимое для записи и считывания из соответствующего элемента памяти 49 накопителя 8 логических с1П налов и О. Если элемент памяти накопителя 8 оказался также неисправным, после его замены на следующий элемент памяти накопителя 8 по крайней мере две строки накопителя 12 будут хранить одинаковый адрес из которых коммутатор 11 выбирает ту,, в которую адрес записан позднее. Останов генератора 21, т.е. окончание проверки, происходит либо по сигналу с выхода счетчика 14, поступающего на второй вход элемента ИЛИ 22 и означающего завершение выполнения теста, либо по сигналу с выхода регистра 17, означающего превышение числа обнаруженных неисправных элементов памяти накопителя 3 над числом элементов памяти накопителя 8, что означает отбраковку микросхемы памяти в накопителе 3. В режиме внешних обращений, т.е. после окончания внутреннего тестирования, совпадение внешнего адреса с адресом, хранИмь1м в накопителе 12, означает автоматическую замену неисправного элемента памяти накопителя 3 на исправный элемент памяти из накопителя 8, Внутреннее тестирование может начиват ся при подключении питания к устройству (без внешнего сигнала Автоном), дпя чего установочный вход устройства должен быть пооключен к шине питания. Таким образом, отбраковка микросхемы памяти в контролируемом накопителе выполняется при обнаружении определе ного (более чем одного) числа неисправных элементов памяти в ней, за счет чего повышается надежность устройства. Технико-экономическое преимущество предпоженного устройства заключается в его более высокой надежности по сравнению с известным.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля полупроводниковой памяти | 1978 |

|

SU749887A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Оперативное запоминающее устройство с автономным контролем | 1979 |

|

SU855739A1 |

| кп | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-08-23—Публикация

1982-05-17—Подача