(54) УСИЛИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| Регулятор напряжения для генератора переменного тока | 1980 |

|

SU1005261A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКООМНЫМИ ВХОДАМИ | 2008 |

|

RU2383099C2 |

| Усилитель | 1988 |

|

SU1720146A1 |

| УСТРОЙСТВО ПОДДЕРЖАНИЯ РЕЖИМА РАБОТЫ ПО ПОСТОЯННОМУ ТОКУ УСИЛИТЕЛЯ | 2001 |

|

RU2207712C2 |

| Дифференциальный усилитель | 1987 |

|

SU1501256A1 |

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УСТРОЙСТВОМ КОРРЕКЦИИ ЭЛЕКТРОТЕРМИЧЕСКОЙ СВЯЗИ В БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2011 |

|

RU2462813C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2349024C1 |

| Безрезистивный арсенид-галлиевый дифференциальный каскад и операционный усилитель на его основе с малым напряжением смещения нуля | 2023 |

|

RU2815912C1 |

| Усилитель | 1988 |

|

SU1580527A1 |

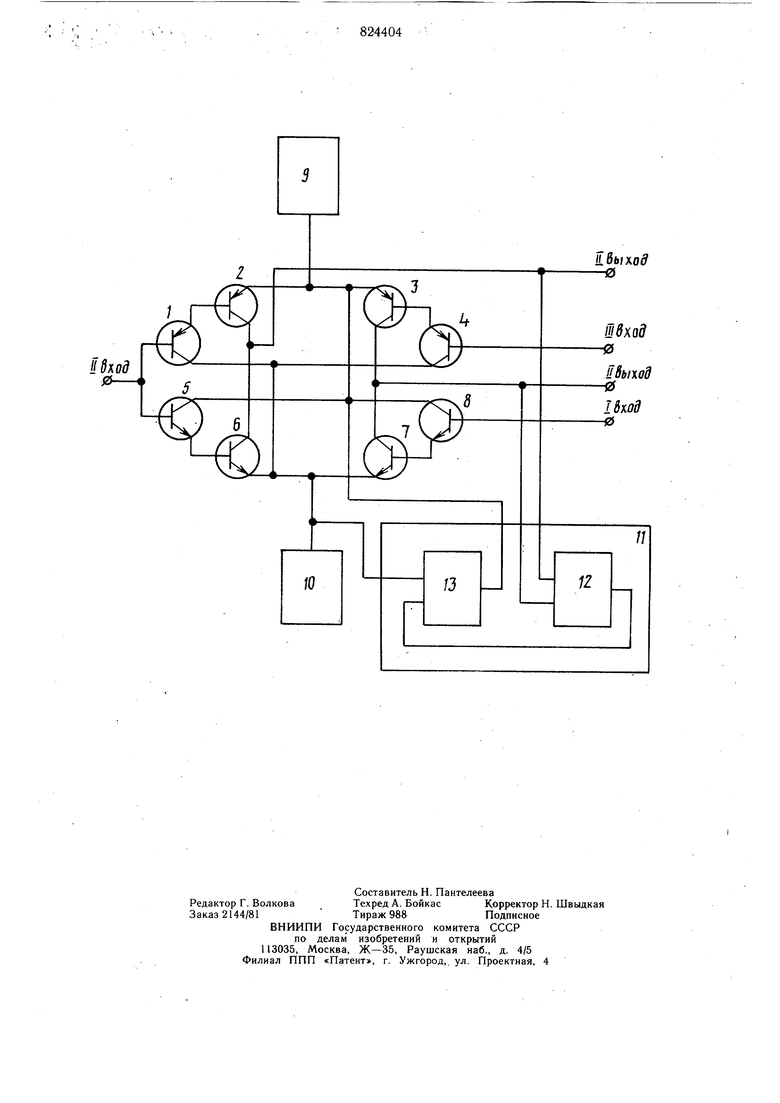

Изобретение относится к информационноизмерительной технике,в частности к усилителям постоянного тока, и может использоваться для предварительного усиления малых сигналов (порядка десятков микровольт) . Известен усилитель, содержащий первый, второй, третий и четвертый транзисторы одного типа проводимости, пятый, шестой, седьмой и восьмой транзисторы другого типа проводимости, первый и второй источники тока, причем выход первого источника тока через последовательно соединенные эмиттер-базовые переходы второго и первого транзисторов подключен к второму входу усилителя, а через последовательно соединенные эмиттер-базовые переходы третьего и четвертого транзисторов - к третьему входу усилителя, выход второго источника тока через последовательно соединенные эмиттер-базовые переходы шестого и пятого транзисторов подключен к второму входу усилителя, а через последовательно соединенные эмиттер-базовые переходы седьмого и восьмого транзисторов - к первому входу усилителя {1. Однако известный усилитель имеет недостаточную стабильность параметров при обработке входного синфазного сигнала. Цель изобретения - повышение стабильности коэффициента передачи дифференциального сигнала при воздействии синфазной помехи. Поставленная цель достигается тем,, что в усилитель, содержаш,ий первый, второй, третий и четвертый транзисторы одного типа проводимости, пятый, шестой. Седьмой и восьмой транзисторы другого типа просводимости, первый и второй источники тока, причем выход первого источника тока через последовательно соединенные эмиттер-базовые переходы второго и первого транзисторов подключен к второму входу усилителя, а через последовательно соединенные эмиттер-базовые переходы третьего и четвертого транзисторов - к третьему входу усилителя, выход второго источника тока через последовательно соединенные эмиттер-базовые переходы шестого и пятого транзисторов подключен к второму входу усилителя, а через последовательно соединенные эмиттер-базовые переходы седьмого и восьмого транзисторов - к первому входу усилителя. дополнительно введен блок совмещения уров ней синфазных сигналов, коллекторы пятого и восьмого транзисторов подключены к выходу первого источника тока, коллекторы первого и четвертого транзисторов подключень; к выходу второго источника тока, коллекторы второго и шестого транзисторов подключены к первому выходу усилителя и первому входу блока совмещения уровней синфазных сигналов, к второму входу которого подключены коллекторы третьего и седьмого транзисторов и второй выход усилителя, к его третьему входу подключен выход одного из источников тока, а к его выходу - выход другого источника тока. При этом блок совмещения уровней синфазных, сигналов выполнен на двух дифференциальных каскадах, первый и второй входы блока совмещения образованы базовыми входами первого дифференциального каскада, третий вход - первым базовым входом второго дифференциального каскада, а его выход - неинвертирующим относительно первого базового входа - коллекторным выходом второго дифференциального каскада, второй базовый вход которого соединен с эмиттерным выходом первого дифференциального каскада. На чертеже изображена структурная электрическая схема предлагаемого усилителя-. Усилитель содержит первый, второй, третий, четвертый, пятый, щестой, седьмой и восьмой транзисторы 1-8, первый и второй источники 9 и 10 тока, блок 11 совмещения уровней синфазных сигналов, выполненный на первом и втором дифференциальных каскадах 12 и 13. Усилитель работает следующим образом. Одной из причин нелинейности и дрейфа нуля выходного напряжения усилителя является зависимость параметров транзисторов от коллекторного напряжения и температуры. Зависимость тока термогенерации, являющегося основной составляющей обратного тока коллекторного перехода для кремниевых транзисторов, от напряжения на коллекторе вызывает дополнительный дрейф нуля усилителя при отработке синфазных сигналов. Кроме того, увеличение коллекторного напряжения транзисторов усилителя при отработке синфазного сигнала вызывает избыточный щум в области коллекторного перехода, а также вызывает саморазогрев транзисторов, что ведет к увеличению обратного тока коллекторного перехода и еще больщему смещению уровня выходного сигнала. Зависимость коэффициента усиления по току и входного сопротивления транзисторов от коллекторного напряжения способствует увеличению нелинейности выходного сигнала усилителя при различных уровнях входного синфазного сигнала. При недостаточном коэффициенте подавления синфазного сигнала усилителя нелинейность выходного сигнала имеет дополнительную составляющую. Использование во входном каскаде усилителя «следящего за синфазным входным сигналом коллекторного питания транзисторов и увеличение коэффициента подавления выходного синфазного сигнала относительно входного синфазного сигнала в значительной степени уменьшает влияние на точность усилителя перечисленных выще дестабилизирующих факторов. Для обеспечения стабильности коллекторного питания входных транзисторов 5 и 8 используется напряжение на эмиттерах транзисторов 2 и 3. В качестве коллекторного питания входных транзисторов 1 и 4 используется на пряжение на эмиттерах транзисторов б и 7. Указанные напряжения незначительно изменяются относительно входного синфазного сигнала. Использование части тока первого источника 9 тока для питания транзисторов 5 и 8 и части тока второго источника 10 тока для питания транзисторов 1 и 4 не влияет на стабильность рабочей точки выходных транзисторов 2, б и 3, 7, поскольку суммарные токи транзисторов 5, 8 и 1, 4 постоянны и во много раз меньше токов транзисторов 2, б и 3, 7. Входные транзисторы 1, 5 и 4, 8 служат для увеличения входного сопротивления усилителя, для задания напряжения между базами выходных транзисторов 2 и б, равного падению, напряжения на переходах баз.аэмиттер входных транзисторов 1 и 5, и для задания напряжения между базами выходных транзисторов 3 и 7, равного падению напряжения на переходах база-эмиттер входных транзисторов 4 и 8. Напряжения на переходах база-эмиттер входных транзисторов 1, 5 и 4, 8 при питании дифференциальных каскадов 12 и 13 от источников 9 и 10 тока практически не зависят от входного синфазного сигнала в широкой полосе частот. Эти напряжения ограничивают допустимую амплитуду сигнала, снимаемого с коллекторов выходных транзисторов 2, б и 3, 7. Неизменное напряжение питания транных каскадов 12 и 13 от источников 9 и 10 тока позволяет уменьшить нелинейность и дрейф нуля усилителя. Соединение между собой коллекторов транзисторов 2 и б и соединение коллекторов транзисторов 3 и 7 при условии высокоомной нагрузки позволяет получить большой коэффициент усиления усилителя. Однако использование высокоомной динамической нагрузки в коллекторной цепи выходных транзисторов 2, б, 3 и 7 ведет к увеличению дополнительной по отношению к входному сигналу синфазной составляющей в выходном сигнале, в результате этого транзисторы 2, 3 или 6, 7 Ыогут войти в режим насыщения и утратить свои усилительные свойства. Использование дополнительно введенного в усилитель блока совмещения уровней синфазных сигналов 11 позволяет скомпенсировать рассогласование синфазных уровней, действующее на входы этого блока, путем коррекции тока на токозадающем входе одного из входных дифференциальных каскадов. В качестве первого дифференциального каскада 12 блока совмещения уровней 11 может использоваться второй дифференциальный каскад усилителя. Рассогласование между входным и выходным синфазными сигналами при равенстве токов одного из входных и первого дифференциального каскада 12 равно разности напряжений на этих токозадающих входах, которая, воздействуя на входы второго дифференциального каскада 13, вызывает противофазное приращение коллекторного тока Л1ц в одном из его транзисторов. Ток первого источника: тока 9 задается больще тока второго источника 10 тока на величину, равную половине суммарного коллекторного тока транзисторов второго дифференциального каскада 13. За счет составляющей тока ДП суммарный ток, текущий через транзисторы 2 и 3, изменяется таким образом, что компенсируется рассогласование синфазных уровней, и выходной синфазный сигнал устанавливается в середине линейного диапазона усилителя. Таким образом, взаимное подключение коллекторов входных транзисторов дифференциального каскада на составных транзисторах одного типа проводимости к точке соединения эмиттеров дифференциального каскада на составных транзисторах другого типа проводимости и подключение коллекторов выходных транзисторов, инвертирующих входной парафазный сигнал, к одному выходу усилителя, и коллекторов выходных транзисторов, не инвертирующих входной парафазный сигнал, к другому выходу усилителя, выгодно отличает предлагаемый усилитель отизвестного вследствие уменьщения дрейфа нуля и нелинейности, что приводит к повышению стабильности коэффициента передачи дифференциального сигнала при воздействии синфазной помехи. Формула изобретения 1. Усилитель, содержащий первый, второй, третий и четвертый транзисторы одного типа проводимости, пятый, шестой, седьмой и восьмой транзисторы другого типа проводимости, первый и второй источники тока, причем выход первого источника тока через последовательно соединенные эмиттер-базовые переходы второго и первого транзисторов подключен к второму входу усилителя, а через последовательно соединенные эмиттер-базовые переходы третьего и четвертого транзисторов - к третьему входу усилителя, выход второго источника тока через последовательно соединенные эмиттер-базовые переходы шестого и пятого транзисторов подключен к второму входу усилителя, а через последовательна соединенные эмиттер-базовые переходы седьмого и восьмого транзисторов - к первому входу усилителя, отличающийся тем, что, с целью повышения стабильности коэффициента передачи дифференциального сигнала при воздействии синфазной помехи, в него дополнительно введен блок совмещения уровней синфазных сигналов, коллекторы пятого и восьмого транзисторов подключены к выходу первого источника тока, коллекторы первого и четвертого транзисторов подключены к выходу второго источника тока, коллекторы второго, и шестого транзисторов подключ ны к первому выходу усилителя и первому входу блока совмещения уровней синфазных сигналов, к второму входу которого подключены коллекторы третьего и седьмого транзисторов и второй выход усилителя к его третьему входу подключен выход одного из источников тока, а к его выходу - выход другого источника тока. 2. Усилитель по п. 1, отличающийся тем, что блок совмещения уровней синфазных сигналов выполнен на двух дифференциальных каскадах, первый и второй входы блока совмещения образованы базовыми входами первого дифференциального каскада, третий вход - первым базовым входом второго дифференциального каскада, а его выход - неинвертирующим относительно первого базового входа - коллекторным выходом второго дифференциального каскада, второй базовый вход которого соединен с эмиттерным выходом первого дифференциального каскада. Источники информации, принятые во внимание при экспертизе i Патент США № 3816761, кл. Н 03 К 5/20, 1974. ISxod f8fc;xo Q

Авторы

Даты

1981-04-23—Публикация

1979-03-19—Подача