I

Изобретение относится к вычисли- ; тельной технике и предназначается, в основном, для использования в еледяще-регулировочных электроприводах переменного и постоянного тока с цифровым управлением, где используются многофазные коды, а управление этими электроприводами осуществляется от вычислительной машины, работающей в двоичном коде.

Известны электроприводы постоянно го и переменного тока, использующие арифметические устройства, работающие в многофазном коде fl .

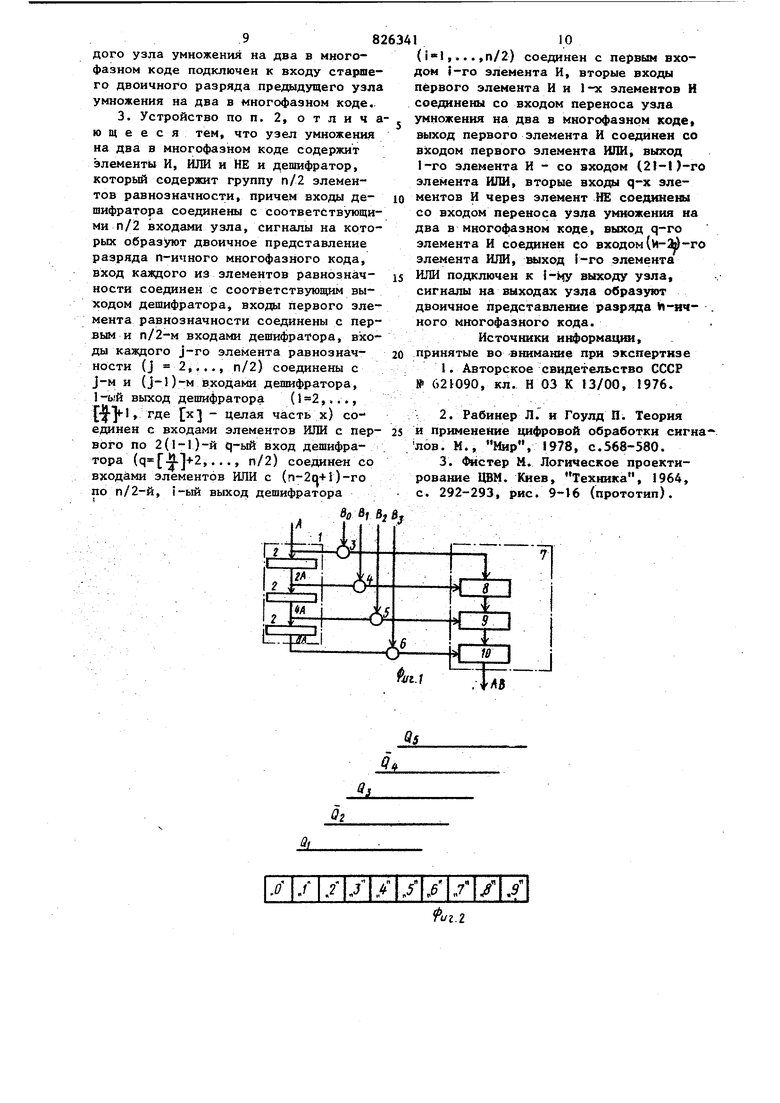

Эти коды выполняются для систем с основанием п 4,6,8,10... Принцип формирования многофазного кода поясним на примере пятифазного кода (п 10), сигналы которого приведены в таблице. В таблице также приведены названные эквивалентные пятифазному коду цифровые сигналы унитарного десятичного кода . Эти эквивалентные цифровые сигналы унитарного

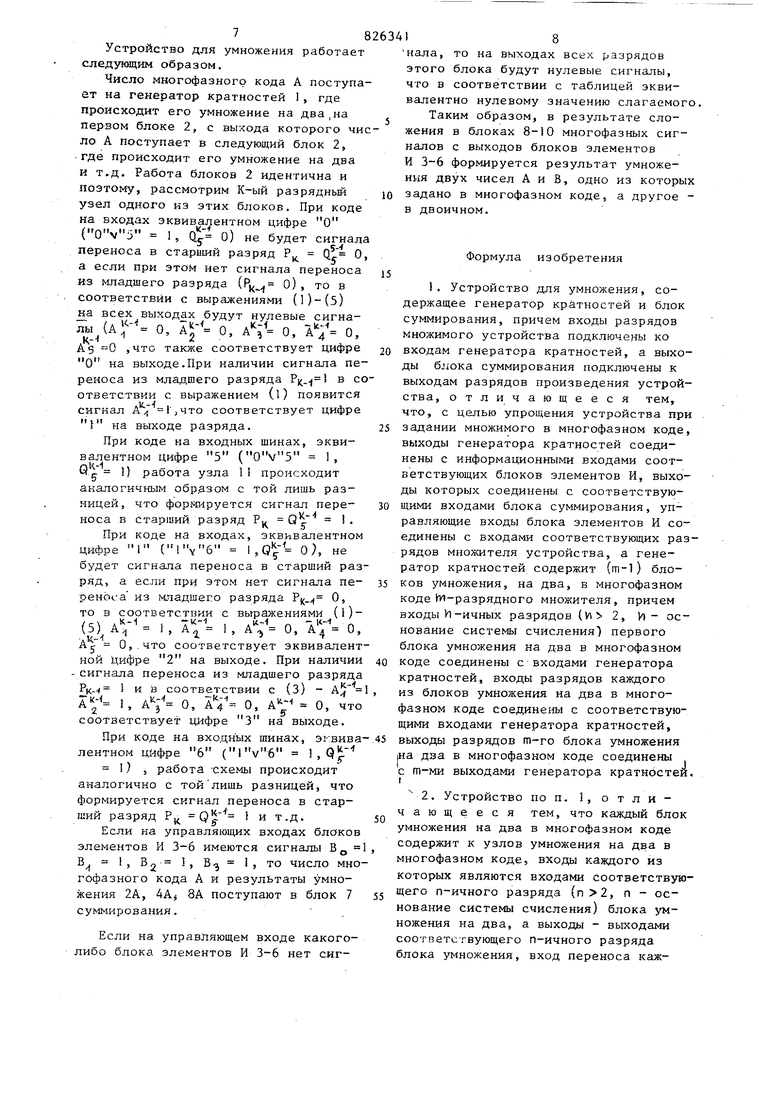

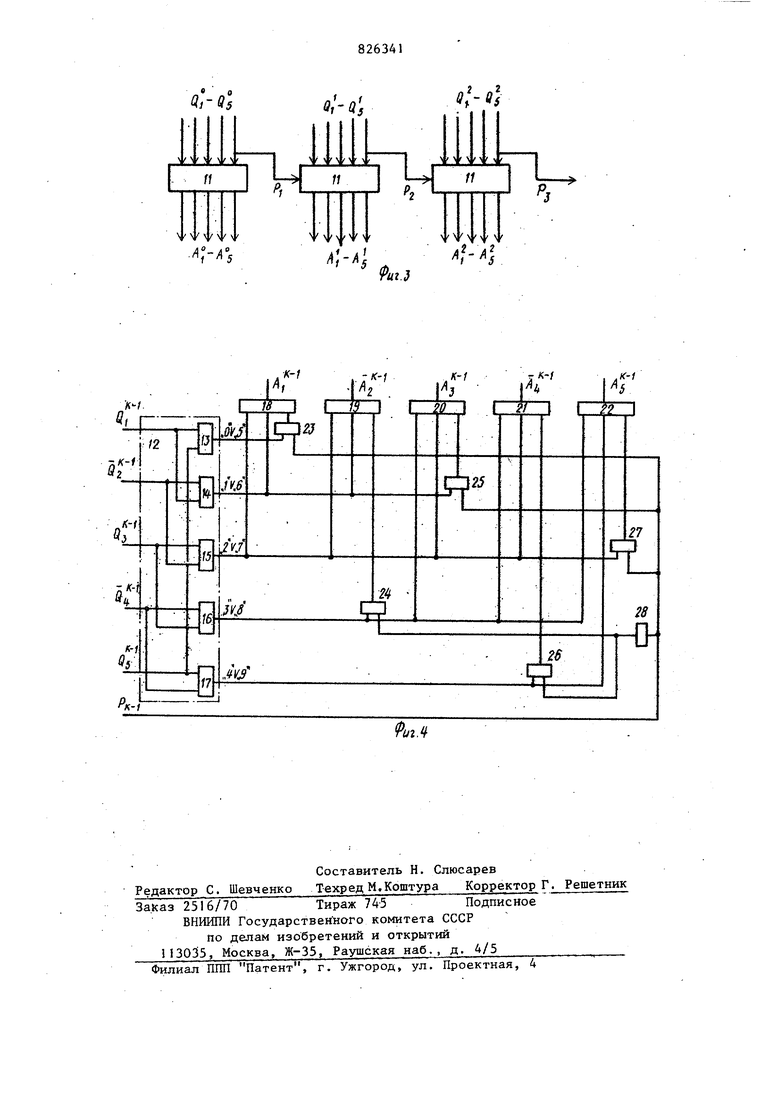

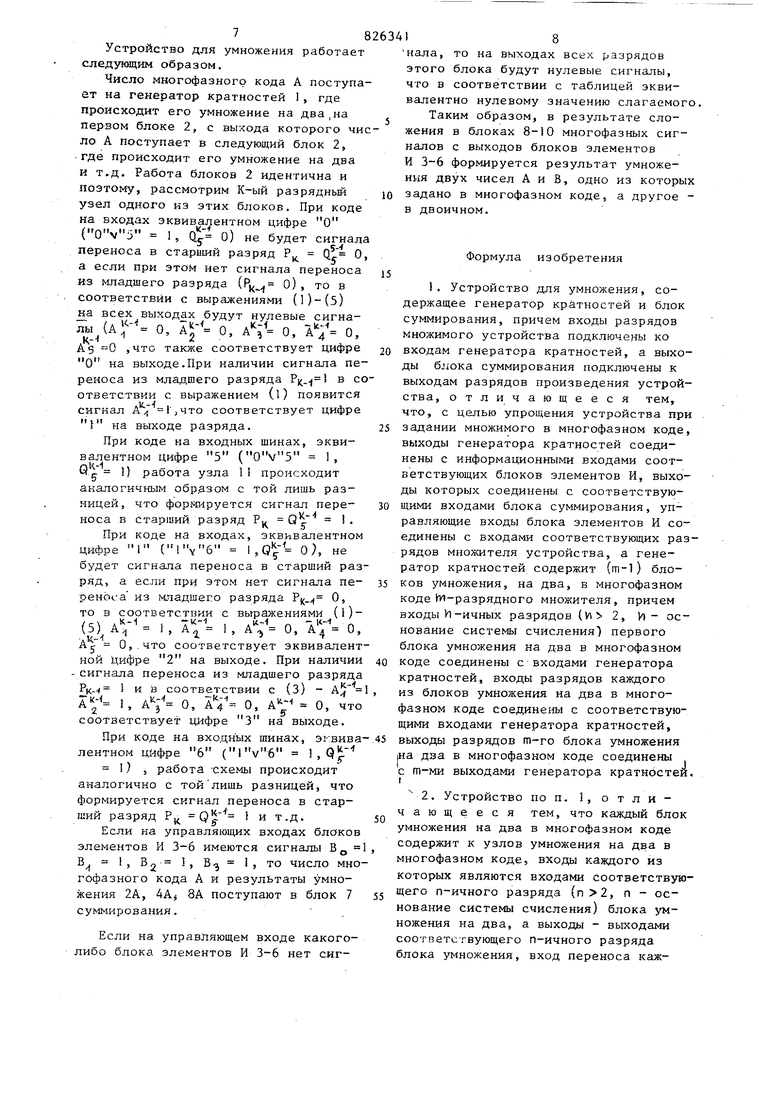

кода могут быть определены при необходимости двувходовыми элементами И (последний столбец таблицы) на входы которых поступают пряные и инверсные сигналы многофазного кода. 38 Продолжение таблицы 7 О 00 1 . 8 0-00 о 9 Известны устройства умножения, ра ботающие в двоичном коде (п 2) Использование таких устройств для случая, когда одно из заданных чисел задано в многофазном коде и необходи результат умножения также в многофаз ном коде, требует наличия на входе и выходе устройства умножения преобразователей из одного кода в другой (многофазного в двоичный и двоичного в многофазный), что приводит к увели чению оборудования и дополнительному снижен1по быстродействия. Вместе с те известно, что системы с основанием п 2 обладают более высоким быстродействием и, следовательно, переход к системе с основанием п 2 нецелесообразен. Наиболее близким к предлагаемому является устройство для умножения, содержащее генератор кратностей и бл суммирования, в котором вход множимо устройства подключен к входу генератора кратностей, выходы которого соединены СО входом блока суммирования выход которого является выходом устройства З. Однако при задании множимого в многофазном коде выполнение такого устройства усложняется за счет необходимости перевода множимого в двоич но-кодированную систему счисления. Цель изобретения - упрощение устройства при задании множимого в многофазном коде. Поставленная цель достигается тем что.в устройстве для умножения, содержащем генератор кратностей и бдок суммирования, причем входы разрядов множимого устройства подключены ко входам генератора кратностей, а выхо ды блока суммирования подключены к выходам разрядов произведения устройства, входы генератора кратностей соединены с информационными входами соответствующих блоков элементов И, 4 выходы которых соединены с соответствующими входами блока суммирования, управляющие входы блоков элементов И, соединены с входами соответствуюгцих разрядов множителя устройства, а генератор кратностей содержит (m-l) блоков умножения на два в многофазном коде т-разрядного множителя, причем входы п-ичных разрядов (, п - основание системы счисления) первого блока умножения на два в многофазном коде соединены с входами генератора кратностей, входы разрядов каждого из. блоков умножения на два в многофазном коде соединены с соответствующим входом генератора кратностей, выходы разрядов т-го блока умножения на два в многофазном коде соединены с т-ми выходами генератора кратностей. Кроме того, каждый блок умножения на два в многофазном коде содержит к узлов умножения на два в многофазном коде,входы каждого из которых являются входами соответствующего п-ичного разряда (п , п - основание си темы счисления) блока умножения на два, а выходы - выходами соответствующего п-ичного разряда блока умножения, вход переноса каждого узла умножения на два в многофазном коде подключен ко входу старшего двоичного разряда предьщущего узла змножения на два в многофазном коде. Кроме того, узел умножения на два в многофазном коде содержит элементы И, ИЛИ и НЕ и дешифратор, который содержит группу п/2 элементов равнозначности, причем входы дешифратора соединены с соответствующими п/2 входами узла, сигналы на которых образуют двоичное представление разряда п-ичного многофазного кода, выход каждого из элементов равнозначности соединен с соответствукяцим выходом дешифратора, входы первого элемента равнозначности соединены с первым и П/2-М входами дешифратора, входы каждого JTO элемента равнозначности (j 2,...., п/2) соединены с j-м и (j-j)-H входами дешифратора, 1-ый выход дешифратора { 2,.. . ,т +, где Х j - целая часть Х) соединен со входами элементов ИЛИ с первого по 2(1-)-й, q-ый вход дешифратора (q .) соединен со входами элементов ИЖ с (п -2q +)-го по R/2-й, i-ий выход дешифратора (i 1,...,- ) соединен с первым вхо582дом i-го элемента И, вторые входы пер вого элемента И и 1-х элементов И соединены со входом переноса узла умножения на два в многофазном коде, выход первого элемента И соединен со вх дом первого элемента ИЛИ, выход J-ro элемента И - со входом (21-1)-го эле мента ИЛИ, вторые входы q-x элементов И через элемент НЕ соединен со входом переноса узла умножения на два в многофазном коде, выход q-ro элемен та И соединен со входом (n-2q)-ro элемента ИЛИ, выход i-ro элемента ИЛИ подключен к i-му выходу узла, сигналы на выходах узла образуют двоичное представление разряда, а п-ичного мно гофазного кода. На фиг, 1 приврдена блок-схема уст ройства для умноження; на фиг. 2 соотношение между сигналами многофазного кода и сигналами десятичного кода на фиг. 3 структурная схема блока умножения на два в многофазном коде; на фиг.А функциональная схема узла умножения на два в многофазном коде. Число А (множимое) задано л многоФазном коде, число В (множитель) - в двоичном, например четьфех-разрядном (BO. B, B, Входы разрядов множимого А соединены со входами генератора кратностей 1, который содержит (m-l) блоков умножения на два в многофазном коде (т - разрядность множителя, в данном случае m 4), причем входы п-ичных разрядов (п - основа системы счисления, в данном случае п 10) первого блока 2 являются входами генератора кратностей 1, а входы каждого последующего блока 2 соединены с выходами предыдущего блока 2. Сформированные блоком кратностей значения А, 2А, 4А 8А поступают на входы блоков элементов И 3-6 соответственно,на управляющие входы которых подаются значения разрядов множителя В, В, Б, В-. &1ХОДЫ блоков элементов И 3-6 подклю чены ко входам блока 7 суммирования, состоящего из последовательно соединеннных суммирукяцих узлов 8-10, на выходе которого формируется значе ние произведения АВ в многофазном коде. КаждьШ блок 2 умножения на два в многофазном коде образует К узлов 1I умножения на два в многофазном коде (К - разрядность числа в п-ичной 6 системе счисления, в данном случае К 3). При этом входы первого разряда, на которые поступают сигналы соединены с входами первого узла I1 умножения на два, вход, на который поступает сигнал (i, соединен с входом переноса следующего узла I1 умножения на два. Входы второго разряда, на которые поступают сигналы , соединены с входами второго узла II, вход Qy соединен с входом переноса следукмцего узла 1 1 умножения на два и т.д. На функциональной схеме узла 1t умножения на два К-го разряда (фагЛ) входы СГ -цу соединены с входами дешифратора 12, который состоит из элементов равнозначности 13-17, формирующих соответственно выходные сигналы по следующему закону. QfVQ.Q, , TI jvQiQj, 2 - QjQ,, 3 VS (i;v i- i5Выходные сигналы А А г формируются на выходах элементов РШИ 18-22, один из выходов которых соединен с выходом элемента И 23-27. Два других входа элементов ШШ 18 и 19 соединены с выходами элементов равнозначности 14 и 15. Два других входа элементов ИЛИ 20 и 21 соединены с выходами элементов равнозначности 15 и 16. Два других входа элемента ИЛИ 22 соединены с выходам элементов равнозначности 16 и 17. Первые входы элементов И 23-27 соединены с выходами элементов равнозначности 13, 16, 14, 17, 15 соответственно. Вторые входы элементов И 23, 25 и 27 соединешл с входом переноса данного узла II, который через элемент НЕ 28 соединен с вторыми входафш элементов И 24 н 26. Сигналы на выходных шинах,К-го узла П у1 шокення на два формируются по следуихции логическим зависимостям (iV6)(2V7)v(B() l -, (1V6)()(R.r(3 8))(2) Pf. (2V7)v{«3V8«)/{.,(MV )) .. (3) А - (2V7)()i/(e(W .о..)) (1,) AV ()i(«V9)u{P,,(2V 7))(5)

Устройство для умножения работает следующим образом.

Число многофазного кода А поступает на генератор кратностей 1, где происходит его умножение на два,на первом блоке 2, с выхода которого число А поступает в следующий блок 2,

где происходит его умножение на два и т.д. Работа блоков 2 идентична и Поэтому, рассмотрим К-ый разрядньш узел одного из этих блоков. При коде

на входах эквивалентном цифре О ( 1, Qj. о) не будет сигнала переноса в старший разряд Р О, а если при этом мет сигнала переноса из младшего разряда (f О) , то в соответствии с выражениями (1)-(5) на всех выходах будут нулевые сигналь( о, А О, Л%- О, А7 О, Ад 0 ,что также соответствует цифре О на выходе.При наличии сигнала переноса из младшего разряда РК- в соответствии с выражением (l) появится сигнал )Что соответствует цифре 1 на выходе разряда.

При коде на входных шинах, эквивалентном цифре 5 ( 1, Q. U работа узла 1 происходит аналогичным образом с той лишь разницей, что формируется сигнал переноса в старший разряд Р

При коде на входах, эквивалентном цифре 1,( 0), не будет сигнала переноса в старший разряд, а если при этом нет сигнала пе из младшего разряда РК. О, то в соответствии с выражениями (1)(5) А t. А5; 1. А О, А 4 О, Аj О,.что соответствует эквивалентной цифре 2 на выходе. При наличии

-сигнала переноса из младшего разряда Рк.4 и в соответствии с (З) - А«/ , AV О, А 4 О, О, что соответствует цифре 3 на выходе.

При коде на входных шинах, Э1:вива лентном цифре 6 ( , Q

1) э работа -схемы происходит аналогично с тойлишь разницей, что формируется сигнал переноса в старший разряд Р 1 и т.д.

Если на управляющих входах блоков элементов И 3-6 имеются сигналы В, В 1, 82 I, В 1, то число многофазного кода А и результаты умножения 2А, 4Aj ЗА поступают в блок 7 суммирования.

Если на управляющем входе какоголибо блока элементов И 3-6 нет сигнала, то на выходах всех разрядов этого блока будут нулевые сигналы, что в соответствии с таблицей эквивалентно нулевому значению слагаемого

Таким образом, в результате сложения в блоках 8-10 многофазных сигналов с выходов блоков элементов И 3-6 формируется результат умножения двух чисел А и В, одно из которых задано в многофазном коде, а другое в двоичном.

Формула изобретения

1. Устройство для умножения, содержащее генератор кратностей и блок суммирования, причем входы разрядов множимого устройства подключены ко входам генератора кратностей, а выходы блока суммирования подключены к выходам разрядов произведения устройства, отличающееся тем, что, с целью упрощения устройства при задании множимого в многофазном коде выходы генератора кратностей соединены с информационнь ми входами соответствующих блоков элементов И, выходы которых соединены с соответствующими входами блока суммирования, управляющие входы блока элементов И соединены с входами соответствующих разрядов множителя устройства, а генератор кратностей содержит (т-1) блоков умножения, на два, в многофазном коде М-разрядного множителя, причем входы И-ичных разрядов (И 2, V - основание системы счисления) первого блока умножения на два в многофазном коде соединены с входами генератора кратностей, входы разрядов каждого из блоков умножения на два в многофазном коде соединены с соответствующими входами генератора кратностей, выходы разрядов т-го блока умножения |на дза в многофазном коде соединены

с т-ми выходами генератора кратностей I

2. Устройство по п. 1, отличающееся тем, что каждый блок умножения на два в многофазном коде содержит к узлов умножения на два в многофазном коде, входы каждого из которых являются входами соответствующего п-ичного разряда (п 2, п основание системы счисления) блока умножения на два, а выходы - выходами соответствующего п-ичного разряда блока умножения, вход переноса каждого узла умножения на два в многофазном коде подключен к входу старшего двоичного разряда предыдущего узла умножения на два в многофазном коде.

3. Устройство по п. 2, отлича ю щ е е с я тем, что узел умножения на два в многофазном коде содержит элементы И, ИЛИ и НЕ и дешифратор, который содержит группу п/2 злементов равнозначности, причем входы дешифратора соединены с соответствующими п/2 входами узла, сигналы на которых образуют двоичное представление разряда п-ичного многофазного кода, вход каждого из злементов равнозначности соединен с соответствующим выходом дешифратора, входы первого злемента равнозначности соединены с первым и n/2-M входами дешифратора, входы каждого j-ro элемента равнозначности (j 2j..., n/2) соединены с J-M и (j-1)-м входами дешифратора, 1-ый выход дешифратора (,..., , где х - целая часть х) соединен с входами элементов ИЛИ с первого по 2(1-1)-й q-ый вход дешифратора (,..., п/2) соединен со входами элементов ИЛИ с ()-го по п/2-й, t-ый выход дешифратора

%в|

(,... ,п/2) соединен с первым входом i-ro элемента И, вторые входы первого элемента И и элементов И соединены со входом переноса узла умножения на два в многофазном коде выход первого элемента И соединен со входом первого элемента ИЛИ, выход 1-го элемента И - со входом (21-1)-г элемента ИЛИ, вторые входы q-x элементов И через элемент НЕ соединены со входом переноса узла умножения на два в многофазном коде, выход q-ro элемента И соединен со входом(й-2Й-г элемента ИЛИ, выход Г-го элемента ИЛИ подключен к }-му выходу узла, сигналы на выходах узла образуют двоичное представление разряда И-ичного многофазного кода.

Источники информащш, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 62Ю90, кл. Н 03 К 13/00, 1976.

2.Рабинер Л. и Гоулд П. Теория

и применение цифровой обработки . М., Мир, 1978, с.568-580.

3.«hicTep М. Логическое проектирование ЦВМ. Киев, Техника, 1964, с. 292-293, рис. 9-16 (прототип).

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения последовательного действия | 1983 |

|

SU1157541A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1977 |

|

SU769539A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

J

.1

Авторы

Даты

1981-04-30—Публикация

1979-06-23—Подача