формирования йулевого номера цикла реверсивного счётчика циклов, а выход - с выходом окончания работы устройства, выходы первого и третьего элементов ИЛИ блока управления соединены соответственно со счетным входом реверсивного счетчика тактов и управляющим входом сдвига регистра множимого, выходы старших разрядов регистров множимого и множителя соединены с инфо1 1ационными входами табличного узла перемножения старших разрядов, выходы произведения и переноса которого соединены соответственно с информационными входами первого и второго разрядов буферного

регистра, выходы первого и второго разрядов буферного регистра соединены соответственно с первыми информационньми входами первого и второго разрядов сумматора, вторые информационные входы первого и второго разрядов которого соединены соответственно с выходами первого и второго разрядов регистра частичных произведений, информационные входы первого, второго и третьего разрядов которого соединены соответственно с выхрдами первого, второго и третьего разрядов сумматора, выход старшего разряда регистра множимого соединен с входом младшего разряда регистра множимого.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в позиционной избыточной ( @ , @ )-системе счисления | 1982 |

|

SU1067498A1 |

| Устройство для умножения | 1979 |

|

SU920705A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения | 1983 |

|

SU1200280A1 |

| Устройство для умножения | 1984 |

|

SU1233136A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ, соде15жащее регистр множимого,регистр множителя, регистр частичных произведений, сумматор, реверсивный счетчик циклов, реверсивный счетчик тактов и блок управления, отличаю- . щ е е с я тем, что, с целью повьшения быстродействия, в него введены буферный регистр и табличньй узел перемножения старших разрядов, а блок управления содержит три элемента ИЛИ, четыре элемента И и четыре элемента задержки, причем вход запуска устройства соединен с счетным входом реверсивного счетчика циклов, первым входом первого элемента ИЛ1 блока управления и первым входом второго элемента ИЛИ блока управления, выход которого соединен с вхо-. дами управления чтением регистра МНОЖ1МОГО и регистра мно)ителя и входом первого элемента задержки блока управления, выход которого соединен с управляющим входом чтения буферного регистра, управляющим входом чтения регистра частичных произведений и с входом второго элемента задержки блока управления,: выход которого соединен с первыми входами первого и второго элементов И блока управления, вторые входы которых соединены соответственно с выходами фо1 ирования ненулевого и нулевого номеров тактов реверсивного счетчика тактов, выход первого элемента И блока управления соединен с первым входом третьего элемента ИЛИ блока управления, первым управляющим входом сдвига, регистра частичных произведений, (Л информационным входом реверсивного счетчика тактов и входом третьего элемента задержки блока управления выход которого соединен с вторым входом второго элемента ИЛИ блока управления, третий вход которого соединен с выходом четвертого элемента задержки блока управления, вход которого соединен с вторыми СП входами первого и третьего элементов Сл ИЛИ блока управления, управляющим входом сдвига per истра множителя, NU BTopbiM управляющим входом сдвига регистра частичных произведений, информационным входом реверсивного счетчика циклов и выходом третьего элемента И блока у1 равления, первый вход .которого соединен с выходом формирования нен.улевого номера иикла реверсивного счетчика циклов, а второй вход - .с выходом второго элемента И и первьи входом четвертого элемента И блока управления.второй вход которого соединен с выходом

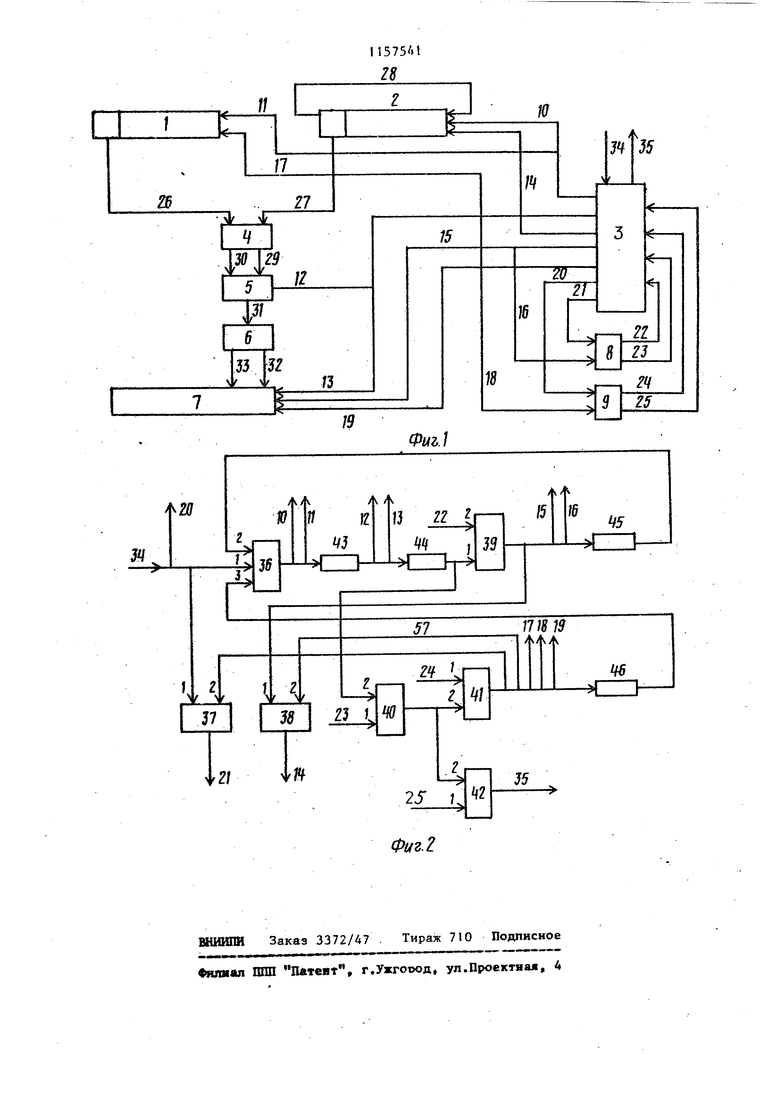

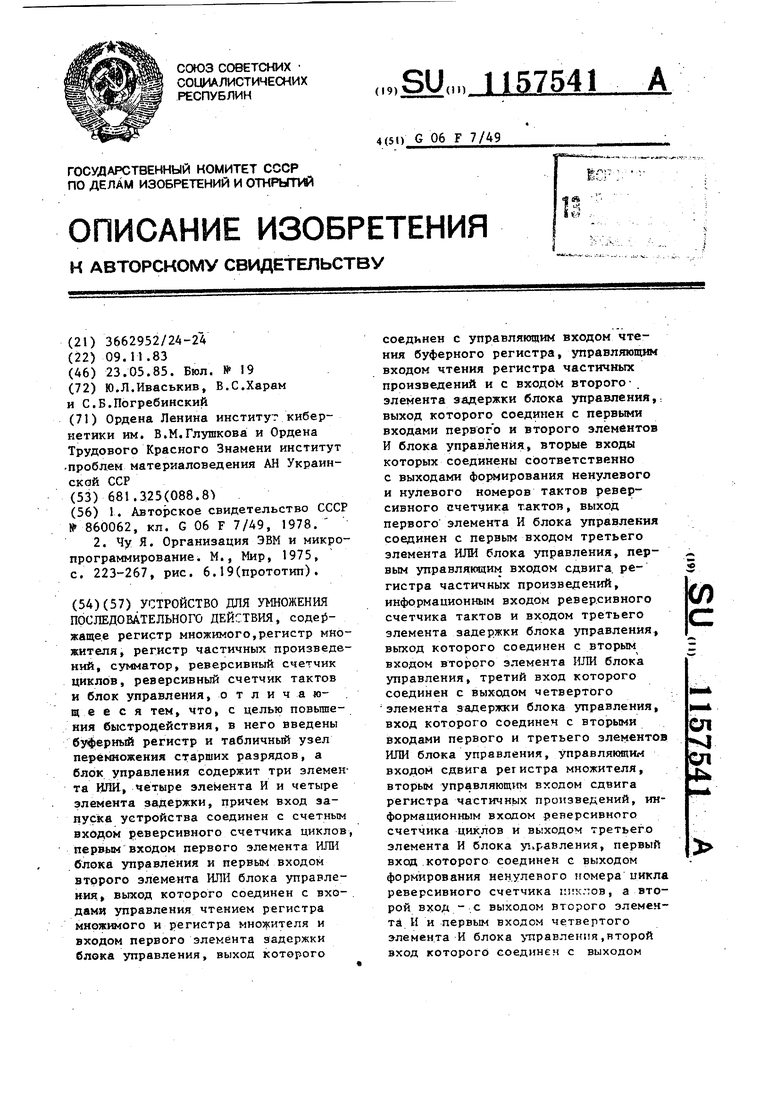

Изобретение относится к вычислительной технике и может бь1Ть использовано при построении арифметических устройств ЦВМ последовательного действия, Известнь устройства для умножения чисел последовательного действия в позиционной двоичной системе счис ления, которые содержат регистр множимого, регистр множителя, сумматор СП Наиболееблизким по тезд1ической сущности к изобретению является устройство для умножении чисел последовательного действия в поэицион ной h-ичной (г72 ) системе счисления содержащее регистры множимого и мно жителя, регистр произведения, сумма тор, блок управлвЕйия, счетчики такт и циклов Недостатком известного устройств является невысокое быстродействие, обусловленное применением последова тельного сумматора, осувцеетвляющего суммирование п-разрядных чисел. Йелью изобретения является повыш ш1ие быстродействия устройства для умножения последовательного действия. Поставленная цель достигается тем, что в.устройство для умножения последовательного действия содержащее регистр гшожимого, регистр множителя, регистр частичшх произведений, сумматор,реверсивный счетчик циклов, реверсивный счетчик тактов и блок управления, введены буферный регистр и табличный узел перемножения старших разрядов, а блок управления содержит три элемента ИЛИ, четьфе элемента И и четьфе элемента задержки, причем вход запуска устройства соединен со счетным входом реверсивного счетчика циклов, первым входом первого элемента ИЛИ блока управления и первым входом второго элемента ИЛИ блока управления, выход которого соединен с входами управления чтением регистра множимого и регистра множителя и входом первого элемента задержки блока управления, выход которого соединен с управляющим входом чтения буферного регистра, управляющим входом чтения регистра частичных произведений и с входом второго элемента задержки блока управления, выход которого соединен с первыми входами первого и второго элементов И блока управления, вторые входа которых соединены соответственно с выходами формирования ненулевого и нулевого номеров тактов реверсивного счетчика тактов, выход первого элемента И блока управления соединен с первым входом третьего элемента ИЛИ блока управления, первым управлякяцим входом сдвига регистра частичтапс произведений, шсформационным входом реверсивного счетчика тактов и входом третьего элемента задержки блока управления, выход которого соединен с вторым входом второго элемента ИЛИ блока управления, третий вход которого соединен с выходом четвертого элемента задержки блока управления, вход которого соединен с вто рыми входами первого и третьего элементов ИЛИ блока управления, управляющим входом сдвига регистра множителя, вторым управлякицим входом сдвига регистра частичных произ ведений, информационным входом, реверсивного счетчика циклов и выходом третьего элемента И блока управления, первьй вход которого соед нен с выходом формирования ненулевого номера цикла реверсивного счетчик циклов, а второй вход - с выходом вторЬго элемента И и первым входом четвертого элемента И блока управле ния, второй вход которого соединен с выходом формирования нулевого иомера цикла реверсивного счетчика циклов, а вйход - с выходом окончания работы устройства, выходы перво го и третьего элементов ИЛИ блока управления соединены соответственно со счетным входом реверсивного счетчика тактов и управляющим входом сдвига регистра множимого, выходы старших разрядов регистров множимог и множителя соединены с информационными входами табличного узла перемножения ртарших разрядов, выходы произведения и переноса которого соединены соответственно с информационными входами первого и второго разрядов буферного регистра, выходы первого и второго разрядов буферного регистра соединены соответственно с первыми информационными входами первого и второго разрядов сумматора вторые информационные входы первого и второго разрядов которого соединены соответственно с выходами первого и второго разрядов регистра частичных произведений, информационные входы первого, второго и третьего разрядов которого соединены соответственно с выходами первого, втор го и третьего разрядов сумматора, выход старшего разряда регистра множимого соединен с входом младшег разряда регистра множимого. На фиг. 1 показана структурная схема устройства для умножения посл довательного действия; на фиг. 2 функциональная схема блока управления устройства для умножения. Устройство для умножения последовательного действия содержит регистр 1 множителя, регистр 2 множимого, блок 3 управления, табличньй узел 4 перемножения старших разрядов, буферный регистр 5, трехразрядный сумматор 6, регистр 7 частичных произведений, реверсивный счетчик 8 тактов, реверсивный счетчик 9 циклов, каналы 10 и 1I, соединяющие первый выход блока 3 управления с входами управления чтением регистров множимого 2 и множителя 1, каналы 12 и 13, соединяющие второй выход блока 3 управления с входами управления чтением регистров 5 и частичных произведений 7, канал 14, соединяклций третий выход блока 3 управления с входом Управления сдвигом регистра 2 мн&жимого, каналы 15 и 16, соединяющие четвертый выход блока 3 управления соответственно с первым управляющим входом сдвига регистра 7 частичных произведений и информационным входом реверсивного счетчика 8 так- тов, каналы 17 - 19, соединяющие пятый выход блока 3 управления соответственно с входом управления сдвигом регистра 1 множителя, с информационным входом реверсивного счетчика 9 циклов, с вторым управляющим входом сдвига регистра 7 частичных произведений, канал 2:0, соединяющий шестой выход блока 3 управления со счетным входом реверсивного счетчика 9 циклов, канал 21, соединяющий. седьмой выход блока 3 управления со счетным входом реверсивного счетчика 8 тактов, каналы 22 и 23, соединяющие выходы формирования ненулевого и нулевого номеров тактов реверсивного счетчика 8 тактов с первым и вторьм входами блока 3 управления соответственно, каналы 24 и 25, соединяющие выходы формирования ненулевого и нулевого номеров циклов реверсивного счетчика 9 циклов с третьим и четвертым входами блока 3 управления соответственно, каналы 26 и 27, соединяющие выходы старших разрядов регистров множителя 1 и множимого 2 соответственно с первьи и вторым информационными входами табличного узла 4 перемножения Старших разрядов соответственно, канал 28, соединяющий выход старшего разряда регистра 2 множимого с входом младшего разряда регистра 2 множимого, каналы 29 и 30, соединяющие вьуходы произведения и переноса табличного узла 4 перемножения старших разрядов соответстзенно с информационньми входами .первого и второго разрядов буферного регистра 5, каналы 31, соединяющие информационные выходы первого и второго разрядов буферного регистра 5 соответственно с первыми информационными входами первого и второго разрядов трехраэрядного сумматора 6, каналы 32, соединяющие информационные выходы первого и второго разряда регистра 7 частичных произведений соответственно с вторыми информационнь1ми входа ми первого и второго разрядов трехразрядного сумматора .6, каналы 33, соединяющие информационные выходы первого, второго, тртьего разрядов трехразрядного сумматора с информационными входами первого, второго, третьего разрядрв регистра 7 частичных произведени соответственно, входной канал 34, соединяющий вход запуска устройства с пятым входам блока управления, выходной канал 35 окончания работы устройства. Блок управления (фиг. 21 содержит элементы ИЛИ 36 - 38, .элементы И 3942, элементы 43-46 задержки. Табличный узел перемножения старших разрядов множителя и множимого может быть построен по схеме, реализуемой на стандартных элементах, таких как дешифраторы и шифраторы. Регистры I и 2 имеют п г-ичных разрядов, регистр 5 - два г-ичных разряда, сумматор 6 - три разряда в избыточной (г,к 1 системе счисления регистр 7 - .(Зп -2 ) к-ичнЫх разрядов Счетчик 8 тактов содержит 0( (л-1)Г двоичных раарящов. Счетчик 9 циклов также содер жит 5 о(, (п--1) двоичных разрядов. Работа устройства для умножения нач 1нается с момента поступления управляющего сигнала по каналу 34 устройства, который может быть сфор мирован в. центральним устройстве уп равления арифметического устройства в котором пр1шеняется в качестве отдельного ф ункционального блока дагное устройство. Управляющий сигн приходящий по входноиу каналу 34, запускает в работу блок 3 управления Блок 3 управления формирует сигналы поступающие по каналам 21 и 20 на входы счетчика 8 тактов и счетчика .9 циклов. Под действием этих сигналов в счетчик 9 циклов и счетчик 8 тактов заносится число -1. Операция умножения двух п-разрядных г-ичных чисел состой из пциклов (от П--1 до 0). В каждом очередном цикле множимое умножается на соответствующ й i-й (i rt, , n-2,...,2,1) разряд множителя. Цикл состоит из п тактов (от п-1 до 1). В. каждом очередном такте {.-и ( , п-12,1) разряд множителя умножается на j-й (j h, -n-l,..., 2,П разряд множимого. Очередной такт выполнения операции умножения начинается с формирования блоком 3 управления сигналов, поступающих по каналам 10 и 11 на входы управления чтением регистров множимого 2 и множителя 1. Под действием этих сигналов старшие разряды регистров 1 и 2 подаются по каналам 26 и 27 на входы табличного уэла 4 перемножения старших разрядов, где и осуществляется умножение, цифр этих разрядов в . г -ичной системе счисления. Результат умножения, представляющий собой цифру произведения и цифру переноса, по каналам 29 и 30 соответственно переписьшается в первый и второй разряды буферного регистра 5. Далее под действием . управляющих сигналов, приходящих с блока 3 управления по каналам 12 и 13, осуществляется суммирование кодов буферного регистра 5 и регистра 7 частичных произведений иа сумматоре 6. Коды регистров 5 и 7 поступает на сумматор 6 соответственно по каналам 31 и 32. Результат суммирования по каналу 33 переписывается в регистр 7. Сумматор 6 осуществляет суммирование кодов в избыточной (г ,к) системе счисления. При выполнении тактов с номерами от п-1 до 1, т.е. когда значение счетчика 8 тактов не равняется нулю, по каналу 22 из счетчика тактов на первый вход блока 3 управления поступает сигнал, в ответ на который в блоке 3 управления вырабатываются сигналы, поступающие по каналам 416 соответственно на сдвиговые входы регистра 2 множимого и регистра 7 частичных произведений, а также на информационный вход счетчика 8 тактов. Под действием этих сигналов в регистре 2 множимого осуществляется 71 циклический сдвиг влево на один разряд, в регистре частичных произведений - сдвиг влево на один разряд, а значение счетчика 8 тактов уменьшает ся на единицу. На этом выпблнекие очередного такта операции умножения заканчивается. Устройство умножения переходит к вьтолнению следующего такта работы. При вьтолнении такта с номером ноль выполняется последний такт очередного j-го цикла (, п-1,.. 1,0). Дальнейшая работа устройства зависит от текущего значения счетчика 9 циклов. При выполнении циклов с номерами от п-1 до 1, т.е. когда значение счетчика 9 циклов не равняется нулю, по каналу 23 из счетчика тактов поступает сигнал, свидетельст вующий о нулевом значении счетчика 8 тактов, а по каналу 24 из счетчика циклов в блок 3 управления поступает сигнал, свидетельствующий о ненулевом значении счетчика 9 циклов. В результате сочетания этих сигналов в блоке 3 управления вырабатываются сигналы, поступающие по каналам 1Д, 17, 18,19, 21 соответственно на регистр 2 множимого, регистр 1 множителя, счетчик 9 циклов, регистр 7 частичных произведений, счетчик 8 тактов. Под действием этих сигналов происходит циклический сдвиг влево в регистре 2 множимого, сдвиг влево на один разряд регистра 1 множителя, уменьшение на единицу значения счетчика 9 циклов, сдвиг вправо на п-2 разряда регистра 7 частичных произведений, занесение числа h-l в счетчик 8 тактов. Завершается очередной цикл работы устройства умножения и осуществляетс переход к следующему за данным циклу работы устройства умножения. При вьтолнении нулевого, такта нулевого цикла работа устройства умножейия заканчивается. При этом по ,каналу 23 из счетчика тактов и по каналу 25 из счетчика циклов в блок 1 3 управления поступают сигналы, в результате сочетания которых блок .. управления по каналу 35 выдает сигнал окончания работы устройства умножения. Результат умножения, представленный в избь точной ( г, 1 ) системе счисления, находится в регистре 7 частичных произведений. Экономический эффект от использования предлагаемого устройства состоит в построении последовательного устройства умножения в г-ичной системе счисления таким образом, что вместе последовательного сумматора п-разрядных чисел используется трехразрядный параллельный сумматор в позиционной избыточной (г, ft) системе счисления. Экономический эффект может быть оценен следующим образом. Время выполнения умножения 1,, при условии, что цифры от О до г -1 в каждом разряде равновероятны, в известном устройстве равно Чм«., где 5 время суммирования последо-вательным сумматором п-разрядных чисел; время сдвига на один разряд регистра множителя и регистра произведения. Так как t nt , где i+ - время суммирования одного разряда сумматора, MKi - / n c/Время выполнения умножения .i в предлагае ом устройстве равно .с)/Чмн.1 .j s«H.r )/ ) Таким образом, при предлагаемое устройство по быстродействию почти, в 4 раза превьппает известное устройство.

П575Л1

01IZ.Z

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для умножения | 1978 |

|

SU860062A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Чу Я | |||

| Организация ЭВМ и микропрограммирование | |||

| М., Мир, 1975, с | |||

| Способ исправления пайкой сломанных алюминиевых предметов | 1921 |

|

SU223A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-23—Публикация

1983-11-09—Подача