(54) ЗАПОМВДАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для отладки программ | 1980 |

|

SU960828A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для управления памятью | 1979 |

|

SU834704A1 |

| Устройство для ввода-вывода отла-жиВАЕМыХ пРОгРАММ | 1979 |

|

SU840913A1 |

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

1

Изобретение относится к запомпнающим устройствам.

Известное устройство содержит долговременную память, счетчик адресов, числовой регистр и вентили. Четные входы регистра связаны с вентилями, сигнальные входы кото-рых подключены через разрядный коммутатор к выходам долговременной памяти, управляющие входы подсоединены к выходам триггеров счетчика адресов, а раздельные входы регистра соединены с блоком установки. С Помощью такого устройства можно контролировать программы, защитые в долговременную память, и выявлять ошибки l 1.

Недостатками этого устройства является невозможность исправлять в нем оперативно ошибки. Для исправления выявленных ошибок необходимо производить технологические операци перегрог инки. Это требует значительных- затрат времени, и, кроме того,

в уже отлаженные программы могут быть внесены новые монтажные ошибки. Это приводит к значительному снижени эффективности устройств, куда входит долговременная память, и увеличению сроков их ввода в действие.

Наиболее близким техническим решением к предлагаемому является устройство, содержащее адресный накопитель, регистр слова, счетчик, регистр адреса, соединенный с регистрами начального и конечного адреса, панель ручной выборки с дешифратором, долговременную память, соединенную через входные - выходные элементы с вычислителем или другим устройством автоматики и вычислительной техники, схему контроля по четности, связанную с регистром слова и через элемент И с сумматором. Регистр слова под1а1ючается к разрядным цепям контролируемого или отлаживаемого запоминающего устройства, соединенного по адресным цепям с регистром адреса. Такое устройство использует метод объейно-неполного резернирования. В адресшз1Й накопитель записываются информационные разряды программы и бит контроля по четности. На панели с ручной выборкой набираются коды адресов информационных ячеек основной долговременной памяти, которые имеют отказавший разряд. В дополнительной долговременной памяти записывается номер отказавшего разряда в информационной ячейке, В случае обнаружения ошибки блоком контроля происходит восста- новление неисправных информационных разрядов программы 2j.

Недостатками этого устройства является возможность коррекции ошибок вызванных только отказом в одном разряде ячейки. Исправления ошибок в результате отказов в двух и более разрядах ячейки накопителя не происходит. Кроме того, использование дополнительной долговременной памяти ограничивает использование устройств для решения задач ускоренной отладки программ и снижает быстродействие системы в целом. Быстродействие уменьшается также и в результате использования блока контроля и дешифраторов адреса корректируемого разряда.

Цель изобретения - расширение области применения запоминающих устройств за счет оперативной смены информации путем ускорения отладки программ,, хранящихся в долговременной памяти.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее блок долговременной памяти, регистр числа, регистр конечного адреса, счетчик, один из входов которого соединен с выходом регистра начального адреса, а другой - с первым выходом блока управления, первый вход которого соединен с первой информационной шиной, а второй выходс первым входом блока долговременной памяти введены блок полупостоянной памяти, дешифратор, адресный блок выборки, блок задержки, блок срав- нения, элементы И, элемент ИЛИ и дополнительные регистры числа, выход одного из которых соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу чет264234

вертого элемента И, первый и второй входы которого подключены соответственно ко второму выходу блока долговременной памяти и третьему выходу блока управления, четвертый и пятый выходы которого подключены соответственно к первому входу блока полупостоянной памяти и первому входу третьего элемента И, второй вход

10 которого подключен к третьему выходу блока долговременной памяти, а выход третьего элемента И через блок задержки подключен к второму входу блока полупостоянной памяти, третий

15 вход которого соединен с выходом другого дополнительного регистра числа,первый и второй входы которого соединены соответственно с шестым выходом блока управления и первым

20 выходом дешифратора, второй, третий и четвертый выходы которого подключены к первым входам соответственно второго, пятого и первого элементов И, вторые входы первого и второго

25 элементов И подключены к одному из выходов адресного блока выборки, второй вход пятого элемента И соединен с выходом основного регистра числа, один вход которого соединен с

30 -выходом элемента ИЛИ, другой - с : входом-выходом блока полупостоянной памяти, выходы первого и второго элементов И подключены к четвертому входу соответственно блоков долговременной памяти и полупостоянной памяти, выход пятого элемента И подключен к второй информационной шине, второй вход блока управления соединен с выходом блока сравнения, один

40 вход которого подключен к выходу

регистра конечного адреса, а другойк выходу счетчика и первому входу адресного блока выборки, второй и третий входы которого подключены

45 соответственно к третьей информационной шине и восьмому выходу блока управления, другой выход адресного блока выборки соединен с первым входом дешифратора, второй вход которого подключен к седьмому выходу блока управления.

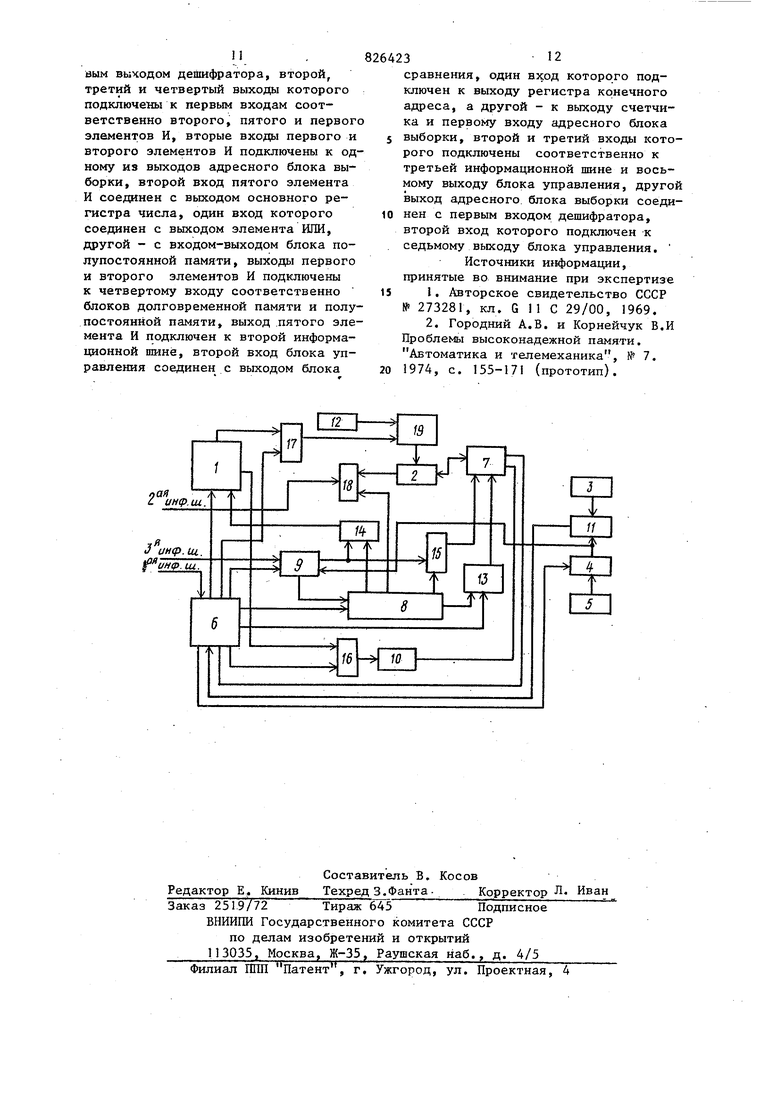

На чертеже представлена структурная схема запоминающего устройства. 55 Запоминающее устройство содержит блок 1 долговременной памяти, регистр 2 числа, регистр 3 конечного адреса, счетчик 4, один из входов которого соединен с выходом регистра 5 начального адреса, а другой - с первым выходом блока 6 управления, первый вход которого соединен с первой информационной шиной, блок 7 полупостоянной памяти, дешифратор 8, адресный блок 9 выборки, блок 10 задержки, блок 11 сравнения, дополнительный регистр 12 числа, дополнительный регистр 13 числа, первый элемент И 14, второй элемент И 15, третий элемент И 16, четвертый, элемент И 17, пятый элемент И 18 и элемент ИЛИ 19.

Запоминающее устройство, позволякщее расширить область применения за счет оперативной смены информации и ускорить отладку программ, работает в трех режимах: режиме перезаписи информации из долговременной памяти в полупостоянную память, режиме ввода новой информации в полупостоянную память и коррекции ранее записанной и рабочем режиме отладки программ, хранящихся в долговременной памяти, при первоначальной регулировке систем или переналадке систем на новые задачи.

Режим перезаписи информации из долговременной памяти в полупостоянную обычно предшествует рабочему режиму отладки.программ. В этом режиме производится запись массивов информации, которые необходимо отладить , из долговременной памяти в полупостоянную. После этого, уже в рабочем режиме, данные массивы информации долговременной памяти отключаются и вместо них включаются соответствующие массивы полупостоянной памяти. Информация в полупостоянной памяти может оперативно корректироваться в режиме коррекции, что значительно ускоряет общую отладку системы, так как исключается дорогостоящие и требующие длительного времени технологические и проверочные операции изменения информации в долговременной памяти. В режиме перезаписи информации работа начинается с установки в исходное состояние всех элементов блока 6 уп-равления, регистра 2 числа, счетчика 4, дополнительного регистра 13 числа. .Блок 6 управления вырабатывает сигналы Уст. О и Запуск, которые поступают в долговременную память 1 . Одновременно по разрешающему сигналу с блока 6 управления

через адресный блок 9 выборки и первый элемент И 14 со счетчика 4 в долговременную память 1 поступает адрес первого числа массивов. Первоначальный адрес определяется регистром начального адреса 5, связанным со счетчиком 4 текущего адреса. Вся информация долговременной памяти 1 делится на ряд массиВОВ, номера которых определяются дешифратором 8, Номер заменяемого массива поступает с дешифратора 8 через первый элемент И 14 также в долговременную память 1, из ко торой через время выборки после сигнала Запуск считывается первое число, которое через четвертый элемент И 17 по сигналу разрешения с блока 6 управления, элемент ИЛИ

19 и основной регистр 2 числа поступает на вход-выход полупостоянной памяти 7. В момент выдачи числа из долговременной памяти 1 вырабатывается сигнал сопровождения,

который через третий элемент И 16

и блок 10 задержки проходит в полупостоянную память 7 и служит сигналом Запуск для нее. Со счетчика 4 адресов через адресный

блок 9 выборки и второй элемент И 15 поступает адрес первого числа массива в полупостоянную память 7, а с дешифратора В и дополнительного регистра 13 числа - адрес номера массийа в полупостоянной памяти 7. По этому адресу происходит запись первого числа массива в полупостоянную память 7, После этого счетчик 4 меняет свое состояние,

через время цикла блок 6 управления выдает новый сигнал Запуск в долговременную память 1 и весь цикл записи повторяется. Перезапись чисел из массива долговременной памяти 1

в полупостоянную память 7 происходит до тех пор, пока адрес в счетчике 4 не сравняется с адресом в регистре конечного адреса 3, и блок 11 сравнения адресов не прекратит подачу

сигналов Запуск из блока управления 6 в долговременную память 1. Таким образом, необходимый массив или массивы, хранящиеся в долговременной памяти 1, окажутся в полупостоянной памяти 7,могут оперативно корректировач ься вручную или автоматически и затем использоваться в рабочем режиме при отладке .

В режиме ввода новой информации и коррекции ранее записанной все регистры и счетчик 4 также устанавливаются в исходное состояние по сигналу с блока 6 управления. На полупостоянную память 7 с блока 6 управления подается сигнал Запуск, а со счетчика 4 через адресный блок 9 выборки и второй элемент И 15 - ад рее записываемого или корректируемого числа в массив. Величина массива определяется регистрами начального адреса 5 и конечного адреса 3: номер массива устанавливается с помопцзю дешифратора 8 и дополнительного регистра 13 числа. Записываемое или корректируемое число поступает из внешних устройств или с пульта ручной коррекции чисел на дополнительный регистр I..2, и через элемент ИЛИ 19, регистр 2 числа проходит на вход-выход полупостоянной памяти 7 и записывается в нее. Запись новых или корректируемых чисел происходит до тех пор, пока блок 11 сравнения не выдает сигнал, прекращающий подачу сигналов Запуск из блока 6 управления. В этом режиме можно ввести новые (большие) массивы информации с перфоленты, вообще не используя долговременную память 1 и не. зашивая в нее никакой информации. Также по ходу отладки можно оперативно корректировать любое число программы, не применяя технологические процессы перепрошивки долговременной памяти 1 .

В основном рабочем режиме отладки программ из третьей информационной шины на адресный блок 9 выборки поступает адрес обрабатываемого числа вместе с номером массива в долговременной памяти 1 и из первой информационной шины сигналы управления на блок 6 управления, которые первоначально устанавливают все элементы, блоки и регистры в исходное положение. С адресного блока выборки адрес номера массива подаётся на дешифратор 8 замены массив, где он расшифровывается и определяется, находится ли данный массив в долговременной памяти 1 или он заменен соответствующим массивом в полупостоянной памяти 7. Если массив находится в долговременной памяти 1,. то адрес с адресного блока 9 выборки через первый элемент И 14 по сигналу разрешения с дешифратора 8 проходит на долговременную память 1J из которой выбирается обрабатываемое число, поступающее на обра.ботку во вторую информационную шину. Если массив находится в полупостоя,нной памяти 7, то адрес через второй элемент И 15 по сигналу разрешения

с дешифратора 8 замены массива поступает в полупостоянную память 7, на которую с блока 6 управления также подается сигнал Запуск. Номер массива в полупостоянной памяти 7 определяется дополнительным регистром числа 13 номера массива, управляемым от дешифратора 8 замены массива. Выбранное из полупостоянной памяти 7 число проходит на вход-выход регистра

2 числа и далее через пятый элемент И 18 по сигналу разрешения с дешифратора 8 на вторую информационную шину.

Таким образом, можно, работать и с массивами информации записанными в долговременную память 1, и с массивами .информации, записанными в полупостоянную память. 7. Блок 6 управления включает в себя генератор стандартных сигналов прямоугольной

формы, элементы И-ИЛИ-НЕ, элементы задержки, счетчик на J.-K триггерах, инверторы, триггеры задания режимов считывания и записи, триггеры резкимов перезаписи информации, вв.ода

новой информации и рабочего режима отладки программ.

В режиме перезаписи информации блок 6 управления выдает в долговременную память 1 сигналы установки в нуль и запуска и разрешает передачу в нее адреса из счётчика 4 адреса через адресный блок 9 выборки и первый элемент И 14. Выбранные числа из долговременной памяти 1 по

сигналу разрешения с блока 6 управления через четвертый элемент И 17 передаются на регистр 2 числа и далее в полупостоянную память 7, которая при этом запускается задержанными

сигналами сопровождения с долговременной памяти 1 через третий элемент И 16 и блок 10 задержки. В режиме ввода новой информации у.п:равления организует запись новых чисел

,в-полупостоянную память 7 в массивы, определяемые номерами массива с дешифратора 8, дополнительного регистра J3 числа и регистрами начального. и конечного адреса 5 и 3.

В рабочем режиме отладки программ блок 6 управления синхронизируется сигналами с первой информационной шины, осуществляя выборку чисел из долговременной памяти 1 или полу постоянной памяти 7 в зависимости о того, заменяется ли данный массив долговременной памяти 1 или нет,

В запоминающем устройстве с ускоренной отладкой программ могут быть быстро введены и отлажены большие массивы информации как при пер.воначальной отладке систем, так и . при переналадке систем на новые зада чи. При первоначальной регулировке систем новые массивы чисел могут быть непосредственно введены в полупостоянную память, использованы в качестве массивов долговременной памяти с быстрой корректировкой с помощью ручного пульта, затем -эти массивы зашиваются в штатные блоки долговременной памяти. При общей отладке всей системы ипи переналадке системы на новые задачи часть массивов (в любом порядке) долговременной памяти переписываются в полупостоянную память, и происходи регулировка системы с определекнол корректировкой записанной инфоркг.ции.

Информация переносится в долговременную память полностью или по блокам в удобное для программистов время (например, при перемонтаже других устройств, при профих актических работах и т.д.). Это не только повьшает производительность труда но и повьшает надежность системы в целом.

Использование предпагаемого запоминающего устройства с ускоренной отладкой программ с введенными в него блоком сравнения, дешифратором, первым дополнительным регистром.числа, полупостоянной памятью, блоком задержки, адресным блоком выборки, вторым дополнительным регистром числа, пятью элементами И и одним элементом ИЛИ, позволяющими производить замену массивов информации, записанПп1к в долговременную память, на массивы полз/постоянной памяти, вводить новые массивы информации из внешних устройств. 1 затем использовать их при отладке и переналадке процессора

или других вычислительных устройств, оперативно корректировать отлаживае, мые массивы информации и заносить уже отлаженную информацию в удобное для обслуживающего персонала время, выгодно отличает его от существукмцих устройств, так как значительно повышает эффективность работы процессора или вычислительного устройства, повьш1ает производительность труда программистов, снижает трудоемкость и затраты на отладку систем и увеличивает надежность систем.

Формула изобретения

Запоминающее устройство, содержащее блок долговременной памяти, регистр числа, регистр конечного адреса счетчик, один из входов которого соединен с выходом регистра начального адреса,а другой - с первым выходом блока управления, первый вход которого соединен с первой информационной шиной, а второй выход с первым входом блока долговременной памяти, отЛИчающеес я тем, что, с целью расширения области применения за счет оперативной смены информации, в устройство введены блок полупостоянной памяти, дешифратор, адресный блок выборки, блок задержки, блок сравнения,. элементы И, элемент ИЛИ и дополнительные регистры числа, выход одного из которых соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, первый и второй входы которого подключены соответственно ко второму ВЫХОДУ блока долговременной памяти и третьему выходу блока управления, четвертый и пятый выходы которого подключены соответственно к первому входу.блока полупостоянной памяти и первому входу третьего элемента И, второй вход которого подключен к третьему выходу блока долговременной памяти, а выход третьего элемента И через блок задержки подключен к второму входу блока полупостоянной памяти,, третий вход которого соединен с выходом другого дополнительного регистра числа, первый и второй входы которого соединены соответственно с шестым выходом блока управления и первым выходом дешифратора, второй, третий и четвертый выходы которого подключены к первым входам соответственно второго, пятого и первог элементов И, вторые входы первого и второго элементов И подключены к од ному из выходов адресного блока выборки, второй вход пятого элемента И соединен с выходом основного регистра числа, один вход которого соединен с выходом элемента ИЛИ, другой - с входом-выходом блока полупостоянной памяти, выходы первого и второго элементов И подключены к четвертому входу соответственно блоков долговременной памяти и полу постоянной памяти, выход .пятого эле мента И подключен к второй информационной шине, второй вход блока управления соединен с выходом блока 3 сравнения, один вход которого подключен к выходу регистра конечного адреса, а другой - к выходу счетчика и первому входу адресного блока выборки, второй и третий входы которого подключены соответственно к третьей информационной шине и восьмому выходу блока управления, другой выход адресного, блока выборки соединен с первым входом дешифратора, второй вход которого подключен к седьмому выходу блока управления. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 273281, кл. G 11 С 29/00, 1969. 2. Городний А.В. и Корнейчук В.И Проблемы высоконадежной памяти. Автоматика и телемеханика, № 7. 1974, с. 155-171 (прототип).

Авторы

Даты

1981-04-30—Публикация

1979-09-17—Подача