1

Изобретение относится к запоминающим устройствам.

Известны запоминающие устройства с коррекцией программы и контролем блоков памяти Ц и 12.

Одно из известных устройств содержит счетчик номеров ячеек, блок дешифраторов, блок информирования синхроимпульсов, синхрогенератор, читающее устройство, оперативную память, соединенную со схемой сравнения tl.

Надостаткёьми этого устройства являются сложность построения устройства и уменьшение быстродействия в результате затрат времени на контроль .

Наиболее близким техническим решением к предлагаемому изобретению является устройство, содержащее адресный накопитель, связанный с регистром адреса, числовой регистр, регистр слова, информация в котором может изменяться с помощью регистра кода, исходного состояния, регистр кода неисправных адресов, соединенный с адресными цепями накопителя и постоянной памятью, а также блок управления с сумматором, блоком контроля, связанным с число1ВЫМ регистром и внешними устройствами. Такое устройство использует метод объемно-неполного резервирования. В адресный накопитель записываются информационные разряды программы и бит контроля по четности. На регистре кода неисправных адресов набираются коды адресов информационных ячеек основной постоянной

0 памяти, которые имеют отказавший разряд. В дополнительной постоянной памяти записывается номер отказавшегося разряда в информационной ячейке. В случае обнаружения ошибки блоком контроля происходит восстановление, неисправных информационных разрядов программы 2.

Недостатками этого устройства являются необходимость перепрошивки

0 дополнительной постоянной пешяти, ограниченность числа корректируемых слов и снижение быстродействия.

Цель изобретения - повьниение быстродействия путем со1(ращения

5 времени отладки программ, хранящихся в постоянной памяти процессра или вычислительной системы.

Поставленная цель достигается тем, что в запоминающее устройство

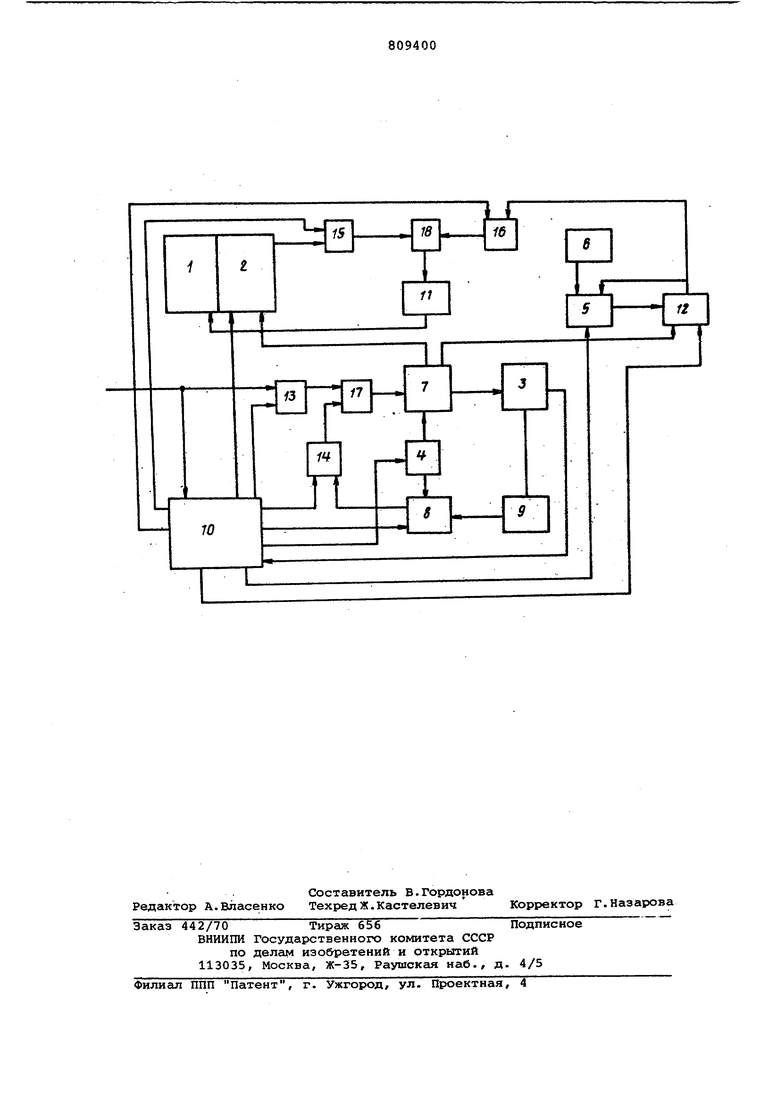

0 -с коррекцией программы, содержащее блок управления, блок постоянной памяти, регистр кода неисправных адресов, адресный и числовой регистр соединенные с регистром исходного состояния, введены блок селекции адресов, один выход которого подключен к первому входу блока постоян ной памяти, другой выход - ко входу регистра кода неисправных адресов, а первый вход к первому выходу адрес ного регистра, дополнительный адресный регистр, один вход которого соединен со вторым выходом адресного регистра, шифратор вход которого соединен с первым выходом регистра кода неисправных адресов, а выход со вторым входом дополнительного адресного регистра, дополнительный блок управления, первый вход которого соединен с кодовой шиной, второй вход - со вторым выходом регистра кода неисправных адресов, первый выход -- с третьим входом дополнительного адресного регистра, второй выход - со входом адресного регистра, а третий выход- со вторым входом числового регистра, блок селекции числа, соединенный с блоком управле ния, блок полупостоянной памяти, первый вход которого связан с число вым регистром, второй вход - с третьим выходом блока селекции адреса, а третий вход - с четвертым выходом дополнительного блока управ ления,, четыре элемента И и два элемента ИЛИ. Первый вход первого элемента И подключен к кодовой шине, второй вход - к пятому выходу допол нительного блока управления, а выход - к первому входу первого элеме та ИЛИ, выход которого соединен со вторым входом блока селекции адреса, а второй вход - с выходом второ го элемента И, первый вход которого связан с шестым выходом дополнитель ного блока управления, а второй вхо с выходом дополнительного адресного регистра. Первый вход третьего элемента И подключен к седьмому выходу дополнительного блока управления, второй вход - к выходу блока постоя ной памяти, а выход - к первому входу второго элемента ИЛИ, выход которого соединен с входом блока селекции числа, а второй вход - с выходом четвертого элемента И, первый вход которого связан с восьмым выходом дополнительного блока управ ления, второй вход - со вторым вход числового регистра и выходом блока полупостоянной памяти. Девятый выхо дополнительного-блока управления подключен ко второму входу блока постоянной памяти. На чертеже показана схема запоми нающего устройства с коррекцией про граммы. Запоминающее устройство с корре цией программы содержит блок 1 упр ения блок 2 постоянной памяти, егистр 3 кода неисправных адресов, дресный регистр 4, числовой регистр , соединенный с регистром б кода сходного состояния. С целью повышения быстродействия путем ускорения отладки, программ в него введены блок 7 селекции адреса, дополнительный адресный регистр 8, шифратор 9, дополнительный блок 10 управления, блок 11 селекции числа, блок 12 полупостоянной памяти, первый элемент И - 13, второй элемент И - 14, третий элемент И - 15, четвертый элемент И - 16, первый элемент ИЛИ - 17, второй элемент ИЛИ 18. Запоминающее устройство с коррекцией программы работает в двух режимах: рабочем режиме автоматической коррекции программы при первоначальной отладке системы или переналадке системы на новые задачи и режиме ручной коррекции записанных в блок полупостоянной памяти чисел программы (сюда относится также режим первоначального ввода корректируемых чисел в блок полупостоянной памятью). Работа устройства в режиме автоматической коррекции программ начинается с поступления из кодовой шины сигналов уст.о и запуск на первый вход дополнительного блока 10 управления. Дополнительный блок 10 управления вырабатывает сигналы установки в исходное состояние дополнительного адресного регистра 8, адресного регистра 4, числового регистра 5 и блока 12 полупостоянной памяти. Затем дополнительный блок 10 управления подает соответствующие сигналы опроса на блок 2 постоянной памяти и на блок 12 полупостоянной памяти. Далее на блок 7 селекции адреса из кодовой шины через первый элемент И - 13 на сигналу разрешения с дополнительного блока 10 управления и через первый элемент ИЛИ - 17 поступает код адреса выбираемого числа. Из блока 7 селекции адреса код адреса поступает по двум каналам: на блок 2 постоянной памяти, где по этому адресу выбирается число, и на регистр 3 кода неисправных адресов. На регистре 3 кода неисправных адресов набраны адреса чисел и массивор которые корректируются и подлежат выборке из блока 12 полупостоянной памяти. В случае совпадения поступающего рабочего адреса с одним из набранных адресов чисел и массивов из регистра 3 кода неисправных адресов на дополнительный блок 10 управления поступает импульс, по которому вырабатывается сигнал подачи в блок 1 управления числа из блока 2 постоянкой памяти или корректируемого числа из блока 12 полупостоянно памяти. Так как блок 12 полупостоянной мяти содержит только К чисел, кото могут подключаться вместо любых из п чисел, хранящихся в блоке 2 постоянной памяти (причем, может быт что К«п), то весь массив блока 12 полупостоянной памяти разбивается на гл массивов по количеству адресо регистра 3 кода неисправных адресо Массивы из блока полупостоянной па мяти могут выбираться как полность так и по отдельным числам, поэтому для получения исполнительного адреса массива или числа в блоке 12 полупостоянной Пс1мяти, который не совпадает с поступившим рабочим адресом из блока 1 управления или сов падает не полностью, включается дополнительный адресный регистр 8. Эт регистр управляется шифратором 9, преобразующим сигналы с регистра 3 кода неисправных адресов в сигналы установки триггеров дополнител ного адресного регистра 8 ( при совпадении поступившего рабочего адреса с одним из адресов регистра 3 кода неисправных адресов).. При этом дополнительный адресный регистр 8 содержит только старшие разряды мае сива или чисел в блоке 12 полупостоянной памяти, а младшие разряды определяются рабочим адресом или разрядами адресного регистра 4, с которого сигналы также поступают на блок 7 селекции адреса и дополнительный адресный регистр 8. Код исполнительного адреса с дополнительного адресного регистра 8 посту пает через второй элемент И-14 по с налу разрешения с дополнительного блока 10 управления и через первый элемент ИЛИ 17 на блок 7 селекции адреса и далее на блок 12 полупостоянной памяти. По этому адресу и по сигналам с дополнительного бло 10 управления из блока 12 полупостоянной памяти выбирается число, которое подается на четвертый элемент И 16. Таким образом, в устрой стве производится выборка двух чисел: из блока 2 постоянной памяти поступающее на третий элемент И 15 и из блока 12 полупостоянной памяти поступающее на четвертый элемент И 16. Пропуск того или иного числа чере .эти элементы и далее через второй . элемент ИЛИ 18 и блок 11 селекции числа на блок 1 управления произво дится по сигналам управления с дополнительного блока 10 управления. В случае совпадения рабочего адреса с одним из адресов чисел массивов набранных на регистре кода неисправ ных адресов, на блок 1 управления пропускается число из блока 12 полу постоянной памяти, в противном случае - из блока 2 постоянной памяти. В режиме ручной коррекции записанных в блок полупостоянной памяти чисел или первоначального ввода корректируемых чисел, адрес числа определяется адресным регистром 4 и подается через блок 7 селек11ии адреса на блок 12 полупостоянной памяти. Код корректируемого числа набирается на регистре 6 кода исходного состояния и вводится в блок 12 полупостоянной памяти через числовой регистр 5. По сигналам управления с дополнительного блока 10 управления производится запись числа в блок 12 полупостоянной памяти. Записанное число может быть проконтролировано в режиме считывания на числовом регистре 5. Дополнительный блок 10 управления состоит из ряда стандартных логических элементов, элементов задержки, триггеров, регистров и тумблеров установки режима,Он включает в себя элементы И, ИЛИ, инверторы НЕ, генератор стандартных сигналов прямоугольной формы, счетчик на триггерах, триггеры рабочего режима и режима ручной коррекции, триггеры -записи-считывания и элементы согласования. В рабочем режиме дополнительный блок 10 управления преобразует поступающие из блока 1 управления сигналы запуска и установки нуля в сигналы разрешения пропуска рабочего адреса через первый элемент И .13 в блок 2 постоянной памяти и через второй элемент И 14 из дополнительного адресного регистра 8 в блок 12 полупостоянной памяти. Сигнал с регистра кода неисправных адресов 3 преобразуется в дополнительном блоке 10 управления в сигналы разрешения пропуска числа в блок 1 управления из блока 2 постоянной памяти через третий элемент И 15 или из блока 12 полупостоянной памяти через четвертый элемент И 16 (с помощью специальных триггеров). В режиме ручной коррекции дополнительный блок 10 управления устанавливает режим записи в блок 12 полупостоянной памяти с помощью триггера записи-считывания, управляет выдачей адреса из адресного регистра 4 в блок 12 полупостоянной памяти через блок 7 селекции адреса, осуществляет подачу сигналов запуска и установки нуля с генератора стандартных сигналов в блок 12 полупостоянной памяти и организует передачу корректируемого числа из числового регистра 6 на вход-выход блока 12 полупостоянной амяти. Таким образом, в запоминающем стройстве с коррекцией программы огут быть введены и откорректиро ваны любые m числа из общего информационного объема постоянной памяти в п чисел или любые массивов чисел (общим информационным объемом в К чисел). В рабочем режиме автоматически с минимальными затратами времени производится замена соответствукидих чисел и массивов постоянной памяти на откорректированные числа. Такая замена практически не влияет на общий цикл работы устройства, но позволяет значительно ускорить отладку программы в постоянной памяти. Уже отлаженные части программ могут быть зашиты в постоянную память при профилактических работах или при других перерывах в работе вычислительных систем что позволяет значительно увеличить время эксплуатации систем,

Использование -предлагаемого запоминающего устройства с коррекцией программы, с введенными в него блоком селекции адреса, дополнительным адресным регистром, шифратором, дополнительным блоком управления, блоком селекции числа, блоком полупстоянной памяти, четырьмя элементами И и двумя элементами ИЛИ, позволяющими производить замену чисел и массивов постоянной памяти в системе управления на откорректированные, легко вводить новые числа и массивы, хранить откорректированные числа в блоке полупостоянной памяти и производить парепрошивку постоянной памяти в любое удобное время, выгодно отличает его от существующих устройств, так как значительно повышает производительност труда в одной из самых трудоемких операций - первоначальной отладке программ и переналадке систем управления на новые задачи.

Формула изобретения

Запоминающее устройство с коррекцией программы содержащее блок управления, блок постоянной памяти, регистр кода неисправных адресов i адресный и числовой регистры, соединенные с регистром кода исходного состояния, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит блок селекции адреса, один выход которого подключен к первому входу блока постоянной памяти, друго выход - к входу регистра кода неисправных адресов, а первый вход - к

первому выходу адресного регистра, дополнительный адресный регистр, один вход которого соединен со вторым выходом адресного регистра шифратор, вход которого соединен с первым

5 выходом регистра кода неисправных адресов, а выход - со вторым входом дополнительного адресного регистра, дополнительный блок управления, первый вход которого соединен с кодовой

Q шиной, а второй вход - с вторым выходом регистра кода неисправных адресов, первый выход - с третьим входом дополнительного адресного регистра, второй выход - с,входом адресного регистра, а третий выход5 с вторым входом числового регистра, блок селекции числа, соединенный с блоком управления, блок полупостоянной памяти, первый вход которого соединен с числовым регистром, второй

0 вход - с третьим выходом блока селекции адреса а третий вход - с четвертым выходом дополнительного блока управления, четыре элемента И и два элемента ИЛИ, первый вход

5 первого элемента И подключен к кодовой шине, второй вход - к пятому выходу дополнительного блока управления, а выход - к первому входу первого элемента ИЛИ, выход ко торого соединен с вторым входом блока селекции адреса, а второй вход с выходом второго элемента И, первый вход которого соединен с шестым выходом дополнительного блока управления, а второй вход - с выходом дополнительного адресного регистра, причем, первый вход третьего элемента И подключен к седьмому выходу дополнительного блока управления, второй вход- к выходу блока постоянной памяти, а выход - к первому вхо ду второго элемента ИЛИ, выход которого соединен с входом блока селекции числа, а второй вход - с выходом четвертого элемента И, первый

5 вход которого соединен с восьгллм

выходом дополнительного блока управления, а второй вход - со вторым входом числового регистра и выходом блока полупостоянной памяти, причем

50 девятый выход дополнительного блока управления подключен к второму входу блока постоянной памяти.

-. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР . № 230521, кл. G 11 С 29/00, 1969.

2. Автоматика и телемеханика, 1974, № 7, с. 155-171 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией программы | 1981 |

|

SU963108A2 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Запоминающее устройство с коррекцией информации | 1986 |

|

SU1392596A1 |

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

| Устройство для коррекции программ | 1983 |

|

SU1141416A1 |

| Запоминающее устройство с коррекцией программы | 1984 |

|

SU1246140A1 |

| Устройство для контроля блоковпОСТОяННОй пАМяТи | 1979 |

|

SU809399A1 |

| Устройство для программного сопряжения электронных вычислительных машин | 1976 |

|

SU641434A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для коррекции информации вблОКАХ пОСТОяННОй пАМяТи | 1979 |

|

SU849308A1 |

Авторы

Даты

1981-02-28—Публикация

1979-06-27—Подача