1

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в адаптивных системах сбора и передачи цифровой информации.

Известен аналого-цифровой преобразователь следящего уравновешивания с равномерно-ступенчатым изменением компенсирующей величины, содержащий блок сравнения, преобразователь «код-аналог, генератор импульсов, ключ, реверсивный счетчик импульсов и регистр. К, одному из входов блока сравнения подключен преобразуемый сигнал, ко второму - выход преобразователя «код-аналог. Первый выход блока сравнения соединен с управляющим входом ключа, а два других выхода блока сравнения - с управляющими входами реверсивного счетчика импульсов. Выход генератора импульсов подключен к информационному входу ключа, выход которого подсоединен к счетному входу реверсивного счетчика импульсов. Информационные выходы реверсивного счетчика импульсов соединены с информационными входами преобразователя «код-аналог и с информационньши входами регистра, к управляющему входу-которого подключен вход импульсов считывания 1.

Недостатком известного преобразователя является необходимость синхронизации импульсов считывания с момента времени, когда изменение мгновенного значения сигнала превышает допустимое значение.

Известен таклсе адаптивный аналогоцифровой преобразователь, содержащий два блока сравнения, первые входы которых соединены меладу собой, элемент ИЛИ, таймер и регистр, управляющий вход которого подключен ко входу таймера и выходу элемента ИЛИ, выход второго блока сравнения подключен ко второму входу элемента ИЛИ 2.

Недостатком этого преобразователя является сложность аппаратурной реализации.

Целью изобретения является упрощение аналого-цифрового преобразователя.

Поставленная цель достигается тем, что в адаптивный преобразователь, содержащий первый и второй блоки сравнения, первые входы которых соединены между собой, элемент ИЛИ, таймер и регистр, управляющий вход которого подключен ко входу таймера и к выходу элемента ИЛИ, у которого выход первого блока сравнения соединен с первым входом элемента ИЛИ, а выход второго блока сравнения подключен ко второму входу элемента ИЛИ, введены первый и второй триггеры, первый и второй реверсивные счетчики импульсов.

первый и второй преобразователи «код- аналог, мультиплексор, генератор импульсов, ключ и линия задержки, причем информационные выходы первого реверсивного счетчика импульсов соединены с информационными входами первого преобразователя «код-аналог и с первой группой входов мультиплексора, выход первого преобразователя «код-аналог соединен со вторым входом первого блока сравнения, информационные выходы второго реверсивного счетчика импульсов соединены с информационными входами второго преобразователя «код-аналог и второй группой входов мультиплексора, выходы которого подключены к информационным входам регистра; выход второго преобразователя «код-аналог соединен со вторым входом второго блока сравнения; выход первого блока сравнения соединен со входом установки нуля первого триггера и с первым управляющим входом мультиплексора; выход второго блока сравнения подключен ко входу установки единицы первого триггера и ко второму управляющему входу мульти.плексора; выход генератора имнульсов подключен к информационному входу ключа, выход которого соединен со счетными входами первого и второго реверсивных счетчиков импульсов, управляющий вход ключа соединен с инверсным выходом второго триггера; вход установки единицы второго триггера подключен к выходу линии задержки, вход которой соединен со входом установки нуля второго триггера и с выходом элемента ИЛИ; управляющие входы прямого счета обоих реверсивных счетчиков импульсов соединены между собой и подключены к инверсному выходу первого триггера, а управляющие входы обратного счета обоих реверсивных счетчиков импульсов соединены между собой и подключены к прямому выходу первого триггера.

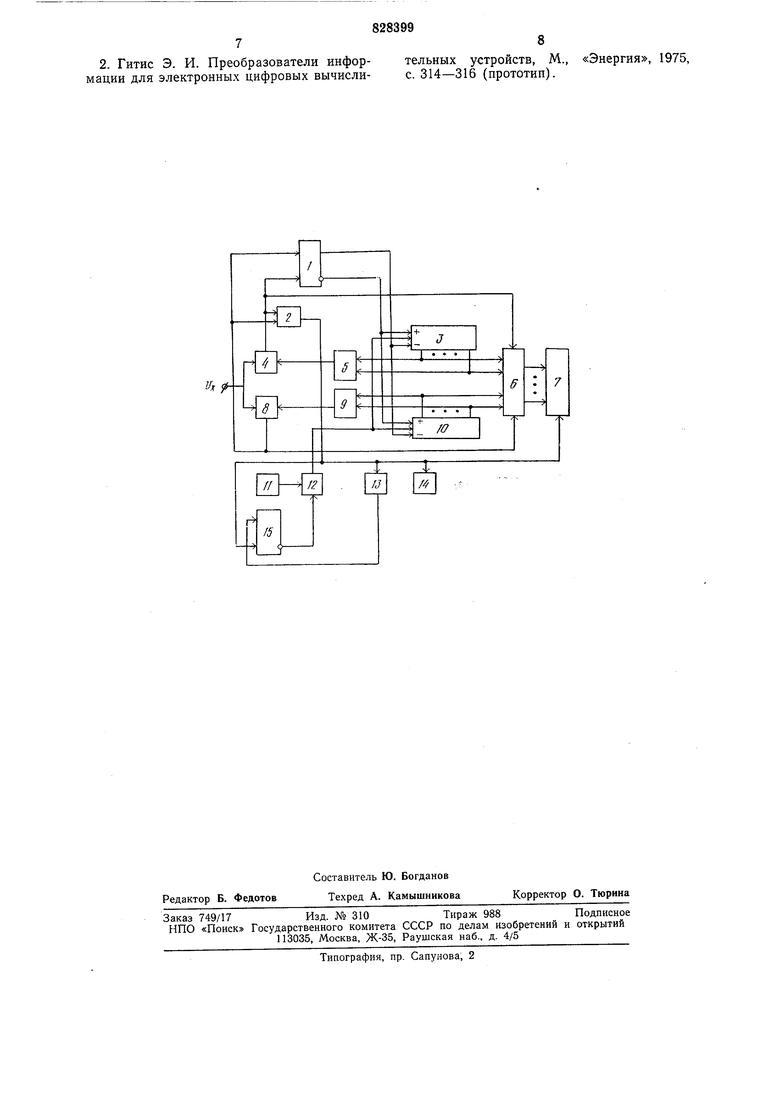

На чертеже изображена структурная электрическая схема преобразователя.

Адаптивный аналого-цифровой преобразователь содержит первый триггер 1, элемент ИЛИ 2, первый реверсивный счетчик импульсов 3, первый блок сравнения 4, первый преобразователь «код-аналог 5, мультиплексор 6, регистр 7, второй блок сравнения 8, второй преобразователь «код- аналог (ПК.А) 9, второй реверсивный счетчик импульсов 10, генератор импульсов И, ключ 12, линию задержки 13, таймер 14, второй триггер 15.

Первые входы блоков сравнения 4 и 8 соединены между собой, к ним подключен преобразуемый сигнал. Второй вход первого блока сравнения 4 подключен к выходу преобразователя «код-аналог 5, информационные входы которого соединены с информационными выходами реверсивного счетчика импульсов 3 и первой группой входов мультиплексора 6, а второй вход блока

сравнения 8 подключен к выходу преобразователя «код-аналог 9, информационные входы которого соединены с информационными выходами реверсивного счетчика импульсов 10 и со второй группой входов мультиплексора 6. Выход блока сравнения 4 соединен с первым входом элемента ИЛИ 2, с входом установки нуля триггера 1 и первым управляющим входом мультиплексора 6.

Выход блока сравнения 8 подключен ко второму входу элемента ИЛИ 2, ко входу установки единицы триггера 1 и ко второму управляющему входу мультиплексора 6.

Выход элемента ИЛИ 2 соединен с управляющим входом регистра 7, с входами линии задерлчки 13 и таймера 14 и с входом установки нуля триггера 15. Вход установки единицы триггера 15 подключен к выхоДУ линии задержки 13. Инверсный выход триггера 15 соединен с управляющим входом ключа 12, информационный вход которого соединен с выходом генератора импульсов 11, а информационный выход ключа 12 соединен со счетными входами реверсивных счетчиков импульсов 3 и 10. Управляющие входы прямого счета счетчиков 3 и 10 соединены между собой и подключены к инверсному выходу триггера 1, а управляющие входы обратного счета соединены между собой и подключены к прямому выходу триггера 1. Информационные входы регистра 7 соединены с выходами мультиплексора 6.

Адаптивный аналого-цифровой преобразователь работает следующим образом. В исходном состоянии триггеры 1 и 15 и реверсивный счетчик импульсов 10 установлены в нуль, а в реверсивном счетчике импульсов 3 установлено значение, соответствующее значению выходного сигнала преобразователя «код-аналог равного 2е, где е - допустимое значение изменения преобразуемого сигнала. При включении устройства на управляющий вход ключа 12 подается напрялсение логической единицы, ключ 12 открывается, и импульсы с генератора 11 начинают поступать через ключ 12 на счетные входы счетчиков 3 и 10. Одновременно

на управляющие входы прямого счета счетчиков подается напряженне логической единицы с инверсного выхода триггера 1. Содержимое счетчиков увеличивается до тех пор, пока не изменится знак неравенства

между значениями U и OKAI пли УпкА2, где Их значение преобразуемого сигнала; t nKAi, t/nKA2 - значения выходного сигнала первого и второго преобразователей «код-аналог 5 и 9 соответственно.

Пусть, например, в исходном состоянии Их 28. Тогда в некоторый момент времени /1 произойдет изменение знака неравенства между значениями Их(1) и Ипкм, т. е.

Ux(t) станет меньше пкм, а знак неравенства С/ж() -2е сохранится. В момент времени i на выходе блока сравнения 4 формируется прямоугольный импульс положительной полярности, который подтверждает состояние триггера 1, и, поступая на первый управляющий вход мультиплексора 6, подключает информационные выходы счетчика импульсов 3 через мультиплексор 6 к информационным входам регистра 7. Этет импульс, проходя через элемент ИЛИ 2, подтверждает состояние триггера 15, записывает в регистре 7 код, зафиксированный счетчиком 3, и поступает на входы линии задержки 13 и таймера 14. Таймер измеряет интервал времени от момента включения устройства до момента поступления импульса. Импульс с выхода линии задержки 13, задержанный на интервал времени т, устанавливает триггер 15 в момент времени 1 + т в состояние единицы, ключ 12 закрывается, прекращая поступление импульсов с генератора 11 на счетные входы счетчиков 3 и 10. Время задержки т выбирается из условия, чтобы при известной частоте следования /о импульсов с генератора 11 состояние счетчиков изменялось за время т на значение, соответствующее изменению выходного сигнала обоих преобразователей «код-аналог 5 и 9 на величину е. Таким образом в момент времени fi + т на выходе преобразователя «код-аналог 5 установится значение Ux(ti) + е, а на выходе преобразователя «код-аналог 9 - значение Ux(ti) -е. Начиная с этого момента устройство «следит за изменением преобразуемого сигнала, т. е. всегда выполняются неравенства /пкА2 x(i) UHKAI при условии, что модуль максимальной крутизны преобразуемого сигнала не превышает значения -. Пусть, например, в момент времени ti Ux(ii) пкА2. В этот момент на выходе блока сравнения 8 формируется прямоугольный импульс положительной полярности, триггер 1 устанавливается в состояние единицы, в регистре 7 фиксируется состояние счетчика 10, таймер определяет интервал времени ti - i-i. Триггер 15 устанавливается в нулевое ссотояние, ключ 12 открывается, импульсы с генератора И начинают поступать на счетные входы счетчиков 3 и 10, уменьщая их состояние. В момент времени ti + -с импульс с выхода линии задержки устанавливает триггер 15 в единичное состояние, ключ 12 закрывается В этот момент на выходе преобразователя «код-аналог 5 устанавливается значение пкА1 Ux(ti) + г, на выходе преобразователя «код-аналог 9 - значение f/nKA2 Ux(ti) -г. Формула изобретения Адаптивный аналого-цифровой преобразователь, содержащий первый и второй блоки сравнения, первые входы которых соединены между собой, элемент ИЛИ, таймер и регистр, управляющий вход которого подключен ко входу таймера и выходу элемента ИЛИ, выход первого блока сравнения соединен с первым входом элемента ИЛИ, выход второго блока сравнения подключен ко второму входу элемента ИЛИ, отличающийся тем, что, с целью его упрощения, в него введены первый и второй триггеры, первый и второй реверсивные счетчики импульсов, первый и второй преобразователи «код-аналог, мультиплексор, генератор импульсов, ключ и линия задержки, причем информационные выходы первого реверсивного счетчика импульсов соединены с информационными входами первого преобразователя «код-аналог и с первой группой входов мультиплексора, выход первого преобразователя «код-аналог соединен со вторым входом первого блока сравнения, информационные выходы второго реверсивного счетчика импульсов соединены с информационными входами второго преобразователя «код-аналог и со второй группой входов мультиплексора, выходы которого подключены к информационным входам регистра, выход второго преобразователя «код-аналог соединен со вторым входом второго блока сравнения, выход первого блока сравнения соединен со входом установки нуля первого триггера и первым управляющим входом мультиплексора, выход второго блока сравнения подключен ко входу установки единицы первого триггера и второму управляющему входу мультиплексора, выход генератора импульсов подключен к информационному входу ключа, выход которого соединен со счетными входами первого и второго реверсивных счетчиков импульсов, управляющий вход ключа соединен с инверсным выходом второго триггера, вход установки единицы второго триггера подключен к выходу линии задержки, вход которой соединен со входом установки нуля второго триггера и с выходом элемента ИЛИ, управляющие входы прямого счета обоих реверсивных счетчиков импульсов соединены между собой и подключены к инверсному выходу первого триггера, а управляющие входы обратного счета обоих реверсивных счетчиков импульсов соединены собой и подключены к прямому выходу первого триггера. Источники информации, принятые во внимание при экспертизе 1. Орнатский И. И. Автоматические измерительные приборы, Киев, «Техника, 1965, с. 351-353.

78

2. Гитис Э. И. Преобразователи инфор- тельных устройств, М., «Энергия, 1975, мации для электронных цифровых вычисли- с. 314-316 (прототип).

828399

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU911721A1 |

| Адаптивный аналого-цифровой преобразователь | 1982 |

|

SU1095387A1 |

| Адаптивный аналого-цифровой преобразователь | 1982 |

|

SU1078609A1 |

| Устройство сжатия аналоговой информации | 1988 |

|

SU1709368A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Устройство для обнаружения ошибок при передаче информации | 1988 |

|

SU1547078A1 |

| Устройство коррекции кода | 1986 |

|

SU1490720A1 |

| Рециркуляционный преобразователь кода во временной интервал | 1987 |

|

SU1474847A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

Авторы

Даты

1981-05-07—Публикация

1979-06-05—Подача