Изобретение относится к измерителям частоты и анализаторам спектр частот и может быть использовано дл обнаружения нескольких сигналов с неизвестной частотой и амплитудой на фоне шума, измерения их частоты и амплитуды. Известно устройство, представляю щее собой анализатор спектра последовательного действия с временной компрессией и содержащее частотно модулированный гетеродин, аналогово запоминающее устройство, смеситель и анализирующий фильтр. Недостатком устройства является низкая точность вследствие применения запоминающего устройства и анализирующего фильтра, выполненных в аналоговом виде. Известно устройство обнаружения сигнала и определения его частоты, содержащее полосовой фильтр, аналого цифровой преобразователь, фильтр нижних частот, оператив гое запомина ющее устройство, первый и второй бл ки возведения в квадрат, выххэды кот рых через сумматор соединены с блоком памяти и обработки, и хронизато первый выход которого соединен с тактовым входом оперативного запоми нающего устройства, второй выход с блоком памяти и обработки. Однако невозможность одновременного обнаружения нескольких сигналов с разной амплитудой вследствие применения аналого-цифрового преобразователя в виде квантователя на два уровня и оперативного запоминающего устройства в виде регистра сдвига снижает надежность устройства. Цель изобретения - повышение надежности устройства. Для достижения этой цели в устройство, содержащее полосовой фильтр, аналого-цифровой преобразователь, фильтр нижних частот, оперативный запоминающий блок, первый и второй. блоки возведения в квадрат, выходы которых через сумматор соединены с блоком памяти и обработки, и хронизатор, первый выход которого соединен с тактовым ву.опом оперативного запоминающего блока, а второй выход с блоком памяти и обработки, введены генератор кода фазы, преобразователи кода фазы в действитель.ную и . мнимую составляющие сигнала гетеродина, первый и второй перемножители, дополнительный фильтр нижних частот, дополнител ьный оперативный запомиигиощий блок, постоянный запоминающий блок, перемножитель комплексных сигналов, первый и второй накопители, причем выход полосового фильтра соединен с аналого-цифровым преобразователем, выход которого соединен с первыми входами первого и второго перемножителя, третий выход хронизатора соединен с генератором кода фазы, выход которого через преобра-. эователь кода фазы в действительн ую составляющую сигнала гетеродина соединен со вторым входом первого перемножителя, выход которого через фильтр нижних частот соединен с оперативным запоминающим блоком, и через Преобразователь кода фазы в мнимую составляющую сигнала гетеродина соединен со вторым входом второго перемножителя, выход которого через дополнительный фильтр нижних частот соединен с дополнительным оперативным запоминающим блоком, тактовый вход которого соединен с хронизатором, выход постоянного запоминающего блока соединен с перемножителем комплексных сигналов, вторые входы которого соединены с выходами оперативного и дополнительного оперативного запоминающего блоков, а выходы через первый и второй накопители с первым и вторым блоком возведения в квсщрат.

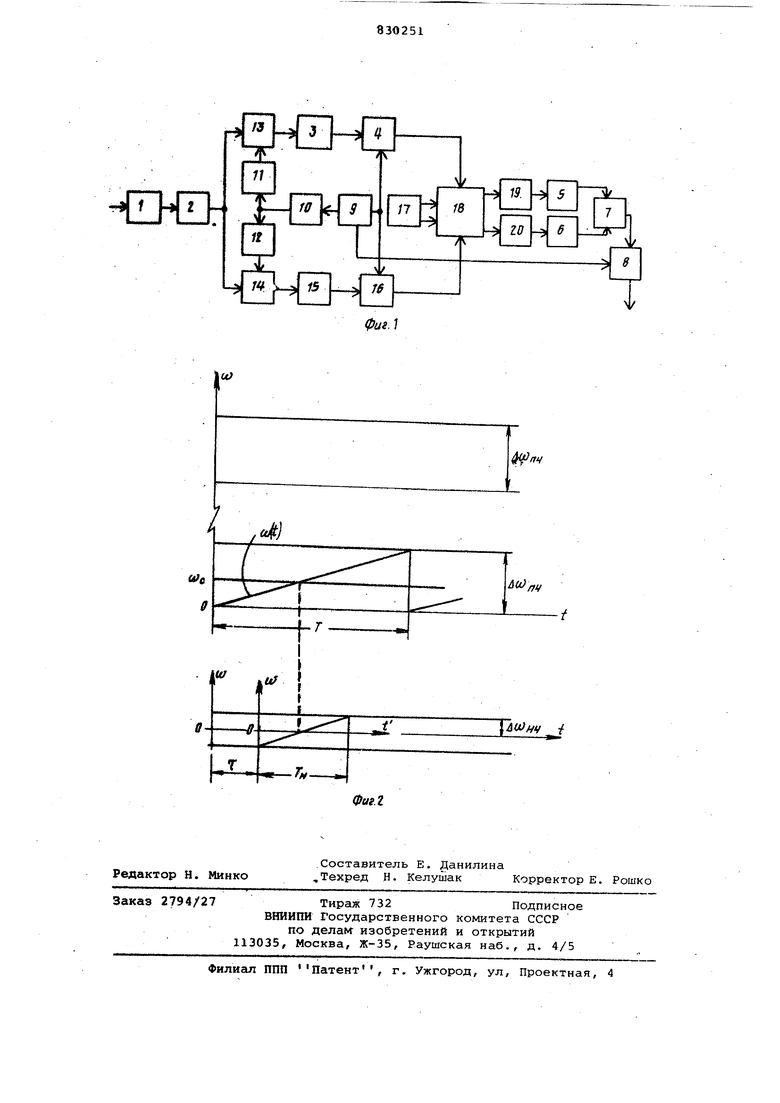

На фиг. 1 приведена -блок-схема устройства на фиг..2 - частотновременная диаграмма его работы.

Устройство содержит (фиг, 1) полосовой фильтр 1, аналого-цифровой преобразователь (АЦП) 2, фильтр 3 нижних частот, оперативный запоминающий блок 4, первый и второй блоки 5 и 6 возведения в квадрат, сумматор 7, блок 8 памяти и обработки, хронизатор 9, генератор 10 кода фазы, преобразоват ели кода фазы в действительную Ни мнимую 12 составляющие сигнала гетеродина, первый и второй перемножители 13 и 14, дополнительный оперативный запоминающий блок 16, постоянный запоминающий блок 17 перемножитель 18 комплексных сигнал первый и второй накопители 19 и 20, При этом полосовой фильтр 1 соедине с АЦП 2, который соединен с перемножителями 13 и 14. Генератор 10 кода фазы через преобразователи Ни 12 кода фазы в действительную и мнимую составляющие сигнала гетеродина ; также соединен с перемножителями, i Перемножители через цифровые фильтр 3 и 15 соедийены с оперативными запоминающими блоками 4 и 16. Оперативные запоминающие устройства соединены с перемножителем 18 комплексиых сигналов, с которым соединен и постоянный запоминающий блок 17. Перёмножитель комплексных сигналов .соединен с накопителями 19 и 20, KO торые через блоки 5 и 6 возведения

в квадрат соединены с сумматором 7. Сумматор соединен с блоком 8 памяти и обработки. Хронизатор 9 соединен с генератором 10кода фазы, оперативным запоминающим блоком 16 и блоком 8 памяти и обработки.

Устройство работает следующим образом.

Сигнал с выхода полосового филь тра 1, полоса пропускания которого. переводится в цифровую форму с помощью АЦП 2. При таком преобразовании происходит размножение спектров около частоты дискретизации и ее гармоник, в том числе и около нулевой частоты. В полосе около нулевой частоты (фиг. 2)сигнал в общем случае может быть записан как S(t) A(t)cos(Wct, где t - дискретные мометы времени с периодом ; ff- частота дискретизации сигнала в АЦП. : Генератор 10 кода фазы выдает числа, являющиеся значениями фазы как квадратр чной функции времени Ч(t) П4 tjTo соответствует линейному изменению частоты си(tj Л(.--t/T . Функция 4(t) - периодическая с периодом Т. Преобразователи 11 и 12 кода фазы образуют на выходе действительную Spn (t) cosf(t) и мнимую ) sin4,(t) составляющие комплексного сигнала гетеродина S(t)S,g (t)+ ), которые перемножаются с сигналом S (t) в перемножителях 13 и 14. Результат этой операции можно записать так

- s(:).l-A(t)e-H.(t)).

: .s((t).

Цифровые фильтры 3 и 15 нижних частот с полосой пропускания диКц каждый выделяют действительную и мнимую составляющие комплексного сигнала разностной частоты S(t). Полезный сигнал на выходах фильтров присутствует в течение времени Т, когда разностная частота находится в интервале ( иЛШ„„). Полоса 4tS)n4 Время существования сигнала Т задержано относительно начала .периода на- величину1;(Ш.-ладн4)/ т{и)(.-ли)4)/Шр , которая зависит от значения частоты .(А; входного сигнала По величине задержки определяется частота «i .

На выходе цифровых низкочастотных фильтров формируется импульс, частот внутри которого изменяется по линейному закону (ЛЧМ - импульс). Если перенести начало отсчета времени на f (фиг. 2), то полезный сигнал на выходах фильтров можно записать так

S(V).AtB- %A(t-4) ,

.где t -t-tr.

Период дискретизации сигнала на выходах фильтров выбирается из уелоВИЯ ty. Л/Аи .За время TH образуется. N. значений выходного сигнала,

.При этом условии

т.е. t

9

, s)A(w)e M4C -irtA(r,,(-T).

Действительная и мнимая составляющие сигнала S(п) записывается в два оперативныхзапоминающих блока 4 и 16, соединенных через перемножитель 18 комплексных сигналов, на другой вход которого поступает комплексный сигнал с постоянного запойинающего блока 17, с двумя накопи.телями 19 и 20, Эти блоки образуют цифровой согласованный фильтр с ЛЧМ-импульсом, появляющимся на выходах цифровых фильтров нижних часто ,Импульсная характеристика фильтра за;писана в постоянном запоминающем ус тройстве и имее вид

. h(v) . Согласованный фильтр вычисляет свертку

- 1 )- il5nr ,sV)(v--n) (,

.

которая является, по существу, спектром сигнала А (п). Блоки 5 и 6 возведения в квадрат и сумматор 7 предназначены для выделения мощности спектральных составляющих А (п),

При действии на входе устройства нескольких сигналов с разной частотой и амплитудой на его выходе будут последовательно получены значения квадратов их амплитуд. Эти числа поступают в блок 8 памяти и обработки. Здесь они сравниваются с порогом и между собой, происходит обнаружение сигналов и измерение ихамплитуд По времени появления этих чисел от начала периода Т определяется частота сигналов. Метки времени поступают в блок памяти и обработки от хронизатора 9.

Формула из обретения

Устройство обнаружения сигналов и измерения их параметров, содержащее полосовой фильтр, аналого-цифровой преобразователь, фильтр нижних частот, оперативный запоминающий блок, первый и второй блоки возведения в квадрат, выходы которых через сумматор соединены с блоком памяти и обработки, и хронизатор, первый выход которого соединен с тактовым входом оперативного запоминающего блока, второй выход с блоком памяти и обработки, о т л и ч а ю ад е е0с я тем, что, с целью повышения надежности устройства, в него введены генератор кода фазы, преобразователи кода фазы в действительную и мнимую составляющие сигнала гетеродина,

5 первый и второй перемножители, дополнительный фильтр нижних частот, дополнительный оперативный запоминающий блок,постоянный запоминающий блок, перемножитель комплексных сигнгшов,

0 первый и второй накопители,причем выход полосового фильтра соединен с аналого-цифровым преобразователем,выход которого соединен с первыми входами первого и второго перемножите-, ля, третий выход хронизатора соеди5нен с генератором кода фазы, выход которого через преобразователь кода фазы в действительную составляющую . сигнала гетеродина соединен со вторым входом первого перемножителя, выход

0 которого через фильтр нижних частЬт ;оединен с оперативным блоком, и через преобразователь кода фазы в мнимую составляющую сигнала гетеродина соединен со вторим входом второ5го перемножителя, выход которого через дополнительный фильтр нижних частот соединен с дополнительным оперативным запоминающим блоком, тактовый вход которого соединен с хрони0затором, выход постоянного запоминающего блока соединен .с перемножителем комплексных сигналов, вторые входы которого соединены с выходами оперативного и дополнительного запоминающего блоков, а выходы - через первый

5 и второй накопители с первым и вторым блоком возведения в квадрат.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения сигналов и измерения их параметров | 1987 |

|

SU1478145A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ГЛУБИНЫ РАСПОЛОЖЕНИЯ ОБЪЕКТОВ С ЛЕТАТЕЛЬНОГО АППАРАТА | 2007 |

|

RU2349937C1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Цифровой анализатор спектра | 1982 |

|

SU1078348A1 |

| Цифровой рециркуляционный анализатор спектра в реальном масштабе времени | 1973 |

|

SU517856A1 |

| Устройство для контроля аналоговых объектов | 1989 |

|

SU1718189A1 |

| СПОСОБ МНОГОПАРАМЕТРИЧЕСКОГО СЛЕЖЕНИЯ ЗА НАВИГАЦИОННЫМИ СИГНАЛАМИ И ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ С МНОГОПАРАМЕТРИЧЕСКИМ УСТРОЙСТВОМ СЛЕЖЕНИЯ ЗА СЛАБЫМИ СИГНАЛАМИ В УСЛОВИЯХ СВЕРХВЫСОКОЙ ДИНАМИКИ ОБЪЕКТА | 2012 |

|

RU2551805C2 |

| Цифровой фазовый дискриминатор | 1986 |

|

SU1394399A1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| СПОСОБ ПЕЛЕНГАЦИИ РАДИОСИГНАЛОВ И ПЕЛЕНГАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2008 |

|

RU2383897C1 |

Авторы

Даты

1981-05-15—Публикация

1979-07-13—Подача