тора подключены к шине питания,

тёр управляющего транзистора и втонены с шиной нулевого потенциала. эмит- рой вьгеод третьего резистора соеди1088068

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1982 |

|

SU1042083A1 |

| Запоминающее устройство | 1973 |

|

SU481067A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Запоминающее устройство | 1973 |

|

SU447757A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОЦП•'t-li | 1971 |

|

SU419982A1 |

| Запоминающее устройство | 1968 |

|

SU842961A1 |

| Полупроводниковое запоминающее устройство | 1973 |

|

SU654197A3 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

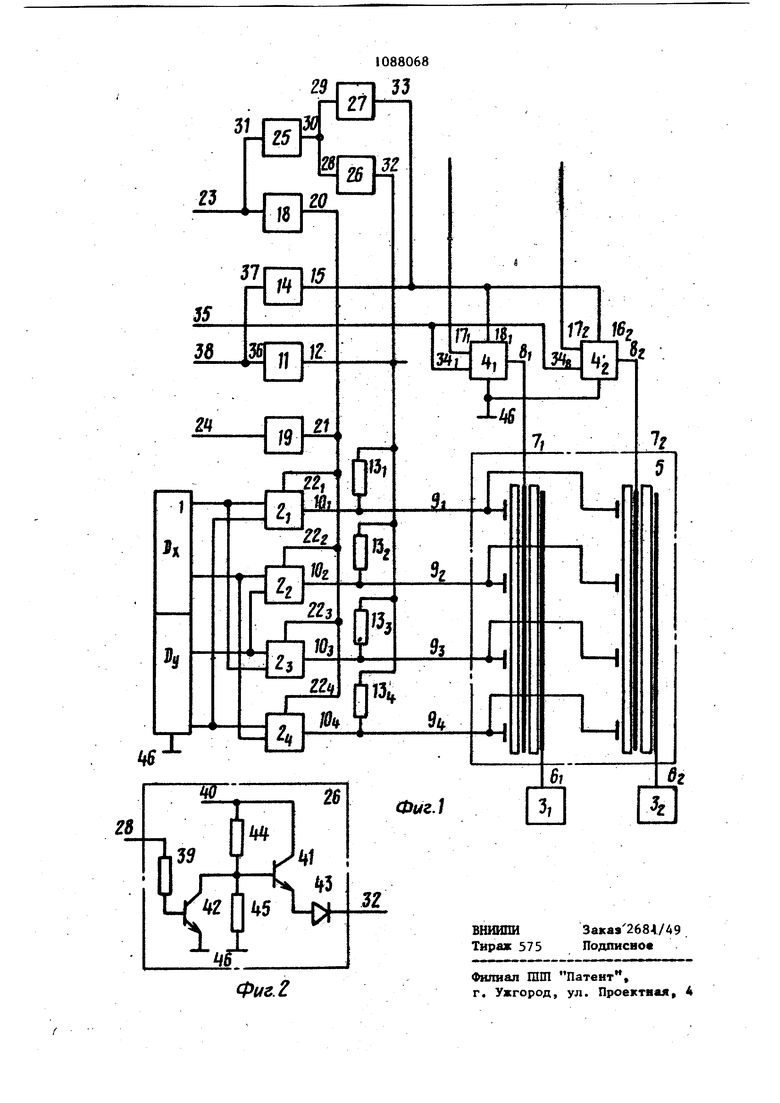

1. ПОЛУПОСТОЯННОЕ ЗАПОШНАЮИЩЕ УСТРОЙСТВО С.ЭЛЕКТРИЧЕСКОЙ ПЕРЕЗАПИСЬЮ ИНФОРМАЦИИ, содержащее дешифратор адреса, адресные ключи за-, лиси и считывания, элементы развязки числовой и разрядный формирователи стирания, разрядные ключи записи, формирователь напряжения считывания,, усилители считывания, формирователь напряжения записи и матрицу пьезокерамических элементов памяти,, раз- , рядные шины считывания которой соединены с входами усилителей считывания, разрядные шины записи с выходами разрядных ключей записи, числовые шины - с выходами адресных ключей записи и считывания, одни из входов которых подключены к выходам дешифратора адреса, а другие входы объединены и соединены с выходами формирователя напряжения считывания и формирователя напряжения записи, выход числового формирователя стирания подключен к одним из выводов элементов развязки, другие выводы которых соединены с выходами адресных ключей записи и считывания, первые входы разрядных ключей записи соединены с выходом разрядного формирователя стирания, вторые входы являются информационными входами устройства, управляющими входами которого являются объединенные входы разрядного и числового формирователей стирания, вход формирователя напряжения записи, вход формирователя напряжения считывания и объединенные третьи входы -разрядных ключей записи, о т- личающееся тем, что, с целью повьшения надежности устройства, в него введены дополнительные формирователи напряжения записи и 9 элемент задержки, вход которого подключен к одному из управляющих входов устройства, а выход соединен с входа ми дополнительных формирователей напряжения записи, выходы которых подключены соответственно к первым входам разрядных ключей записи и одним из выводов элементов развязки. 2. Устройство по п.I, о т л и 00 00 чающееся тем, что каждый дополнительный формирователь напряже- . о ния записи содержит управляквдий и Од коммутирующий транзисторы, резисто00 ры с первого по третий и диод, анод которого подключен к эмиттеру коммутирующего транзистора, а каТод является выходом формирователя, входом которого является один из выводов первого резистора, второй вывод которого соединен с базой управлякицего транзистора, коллектор которого подключен к одним из выводов второго и третьего резисторов и базе коммутирующего транзистора, коллектор которого и другой вывод второго резис

Изобретение относится к вычислительной технике, в частности к области полупостоянных-запоминаницих устройств ( ЗУ I с электрической перезаписью информации на основе сегнето электрических пьезотрансформаторных элементов памяти, совмещенных с аппаратурой перезаписи и предназначенных для работы в тяжелых эксплуатационных условиях. Известно запоминающее устройство содержащеематрицу пьезокерамических элементов памяти, числовые шины которой подключены к выходам адресных ключей записи-считьшания, разрядные шины считывания - к входам усилителей считывания, разрядные шины записи - к выходам разрядных ключей за писи, формирователи напряжений стирания, записи и считывания ГJ. Недостатком этого устройства является низкая надежность и большое число блоков адресной части. Низкая надежность обусловлена большим напря жением разрушения в невыбранных элементах памяти при записи информации. Наиболее близким к изобретению является полупостоянное ЗУ с электрической перезаписью информации, со- держащее дешифратор адреса, связанный с адресными ключами записи-считывания, усилители считывания, разрядные ключи записи, матрицу пьезокерамических элементов памяти, разрядные шины считьгоания которой соединены с входами усилителей считывания, разрядные шины записи - с вы ходами разрядных ключей записи, числовые шины - с выходами адресных ключей записи-считывания, «Числовой формирователь стирания, выход которого через резисторы подключен к чис ловым шинам, разрядный формирователь стирания, подключенный своим выходом к сигнальным входам разрядных ключей записи, формирователи напряжений записи и считывания, входы которых объединены и подключены к сигнальным входам адресных ключей t2j. Однако в известном устройстве низкая надежность также обусловлена . большим напряжением разрушения в невыбранных элементах памяти лри записи информации. Действительно, в данном устройстве коэффициент разрушет ния, т.е. отношение напряжения записи к напряжению разрушения, равен трем. В то же время параметры современных пьезокерамических материалов в диапазоне рабочих температур обуславливают смещение характеристик записи элементов памяти, при которо 4 устойчивая работа устройства возможна при коэффициенте разрушения, равном 4 и более. Целью изобретения является повышение надежности устройства. Поставленная цель достигается тем, что в полупостоянное запоминакицее усройство с электрической переза- ;. писью информации, содержащее дешифратор адреса, адресные ключи записи и считывания, элементы развязки, числовой и разрядный формирователи стирания, разрядные ключи записи, формирователь напряжения считывания, усилители считывания, формирователь напряжения записи и матрицу пьезокерамических элементов памяти, разрядные шины считывания которой соединены со входами усилителей считывания, разрядные шины записи - с выходами разрядных ключей записи, числовые шины - с выходами адресных ключей записи и считывания, одни из входов которых подключены к выходам дешифратора адреса, а другие входы объединены и соединены с выходами формирователя напряжения считывания и формирователя напряжения записи, выход числового формирователя стирания подключен к одним из выводов элементов развязки, другие выводы которых соединены с выходами адресных, ключей записи и считывания, первые входы разрядных ключей записи соединены с выходом разрядного формирователя стирания, вторые входы являются информационными входами устройства, уп равляющими входами которого являются объединенные входы разрядного и числового формирователей стирания, вход формирователя напряжения записи, вход формирователя напряжения считывания и объединенные третьи BXO ды разрядных ключей записи, введены дополнительныеформирователи напряжешш записи и элемент задержки, вход которого подключен к одному из управляющих входов устройства, а выход соединен со входами дополнительных формирователей напряжения записи, выходы которых подключены соответственно к первым входам разрядных ключей записи и одним из выво дов элементов развязки. Каждый дополнительный формирователь напряжения записи содержит управляющий и коммутирующий транзисторы, резисторы с первого по третий и диод, анод которого подключен к эмиттеру коммутирующего транзистора, а катод является выходом формирователя, входом которого является один из выводов первого резистора, второй вывод которого соединен с базой управляющего транзистора, коллектор которого подключен к одним из выводо BTOpoi;o и третьего резисторов и базе коммутирующего транзистора, колле тор которого и другой вывод второго резистора подкл19чены к шине питания эмиттер управлякнцего транзистора и второй вывод третьего ре зистор й; соединены с шиной нулево1:о потенциала. На фиг.1 представлена структурная схема полупостоянного запоминающего устройства; на фиг. 2 - прингдапиапьная схема дополнительного формирователя напряжения записи. Полупостоянное запом11нающее устройство содержит (г. I} дещифратор I адреса, связанный с адресными ключами 2 -24 записи и считывания, усилители 3,, 32 считывания, разрядные ключи -1 S записи, матрицу 5 пьезо керамических элементов памяти, разрядные щины 6, 6 считывания которой соединены с входами усилителей записи - 4, разрядные шины Ч выходами 8, 8. разрядных ключей т 4л записи, числовые шины о -О У 4 выходами 10 адресных ключей 2. записи и считывания,, числовой с формирователь 11 стирания, выход 12 которого через элементы развязки, например резисторы 13,,- 13ц. подклю349.- 9. чен к числовым шинам -7 разрядный формирователь 14 стирания, подключенный своим выходом 15 к первым входам I6fl, JGj разрядных ключей 4 4 записи, вторые входы 17, I7, которых являются информационшлми входами устройства, формирователь 18 напряжения записи и формирователь 19 напряжения считывания, выходы 20 и 21 которых объединены и подключены к входам адресных ключей 2.|-2 записи и считывания, а входы 23 и 24 являются одними из управляющих входов устройства. Кроме того, устройство содерзьит элемент 25 задержки, дополнительные формирователи 26 и 27 напряжения записи, входы 28 и 29 которых объединены и подключены к выходу 30 элемента 25 задержки f имекицего вход 31. Выход 32 формирователя 26 подключен к выводам резисторов 13j., а выход 33 формирователя 27 - ко входам 17;, 172 Р 13рядных ключей , 4 записи, третьи 34jj, 34 которых объединены и соединены с управляющим входом 35 устройства, а входы 36 и 37формирователей 11 и 14 объединены и соединены с управлякгашм входом 38 устройства. Каждь дополнительный формирователь 26 или 27 содержит (фиг.2) первый резистор 39, шину 40 питания, коммутирующий 41 и управляющий 42 Транзисторы, диод 43, второй 44 и третий 45 резисторы и шину 46 нулевого потенциала. Устройство работает стирание, запись, считывание. При стирании информации на вход 38устройства подают управляющий импульс , по которому на выходах формирователей П и 14 форгшруются импульсы полного напряжения стирания, проходящие через разрядные ключи 4 записи на разрядные шины 7 записи, а через резисторы 13 - на числовые шины 9. На вход 35 устройства подают сигнал логический О. В этом случае все разрядные ключи 4 записи коммутируют импульс полного напряжения стирания на разрядные шины 7 записи. Выбранную числовую шину, например шину 9, коммутируют через выбранный ключ 2 на шину 46 нулевого потенциала, а на остальные невыбранные числоi вые шины поступает импульс полного напряжения стирания, В результате, запоминающие элементы выбранного адреса устанавливаются в нулевое состо ние, соответствующее минус Р.,, а запоминающие элементы невыбранных адресов сохраняют прежнее состояние, так как импульсы напряжения стирания создают в них противоположно направленные электрические поля, взаимно компенсирующие друг друга. Стирание информации можно провести во всех ал ресах сразу за один такт, для чего дополнительно стробируют дешифратор 1 адреса, подключая через ключи 2л все числовые шины 9.,-9 к шине 46 нулевого потенциала. При записи информации на вход 23 устройства подают импульс управления который на выходе 20 формирователя 18 формирует импульс полного напряжения записи амплитудой U и длитель ностью tj, поступаюп 1й через выбранный ключ 2 на выбранную числовую шину 9, и пройдя элемент 25 задержки и расширившись до длительности 2tj, поступает на входы формирователей 26 и 27. На выходе 32 формирователя 26 формируется импульс напряжения амплитудой и.« 4 и длительностью 2t который через резисторы 13 поступает на все невыбранные числовые шины 9. На выходе 33 формирователя 27 формируется импульс напряжения амплитудой и длительностью 2tj,, который че рез ключи 4 (в соответствии с записы ваемой информацией ) поступает на раз рядные шины 7 записи. Кроме того, разрядные шины записи тех разрядов, в которые записывается логическая 1, коммутируют на шину 46 нулево- гр потенциала через разрядные ключи 4 записи по сигналам со входов 17. В результате в выбранном адресе происходит переключение пьезокерамики в состояние плюс Р в тех эапоминающих элементах, где записывается логическая I , а пьезокерамика тех элементов, где записывается логический О, претерпевает двойное переключение по частному циклу под действием напряжений lL/2 я первом полутакте (от О до t) и -и,«/2 во втором полутакте(от t до 2 t ) и, таким образом, остается в состоянии, близком к минус PJ, . На запоминающие элементы выбранных адресов в течение двух тактов воздействуют импульсы напряжений амплитудой , которые лишьв допустимых пределах изменяют предыдущую поляризацию пьезокерамики. При считывании информации на вход 24 устройства подают импульс управления, по которому на формирователя 19 формируется импульс возбзгждения с заданными параметрами, поступающий через выбранный адресный ключ 2 на выбранную чнсловую шину 9. Вы- : ходные сигналы, полярность которых определяется нaпpaвлeниe I поляризации пьезокерамики запоминающих элементов выбранного адреса, формируются на шинах 6 путем двойного элек- тромеханического преобразования энергии импульса возбуждения. Считывание информации происходит без разрушения, так как амплитуду импульсов возбуждения выбирают меньше допустимого уровня напряжений разрушения запоминающих элементов. Технико-экономическое преимущество предлагаемого устройства по сравнению с известным заключается в повышении его надежности за счет расширения области устойчивой работы. В случае применения пьезокерами-г ки ЦТС-19 область устойчивой работы предложенного устройства по сравнению с известным устройством увеличивается примерно в 4 раза, что обеспечивает надежную работу без термостабилизации и термокомпенсахщи в диапазоне температур -40 - .

29 I-1 55

1088068

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 0 |

|

SU331421A1 |

| Насос | 1917 |

|

SU13A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОЦП•'t-li | 1971 |

|

SU419982A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-04-23—Публикация

1983-02-22—Подача