(54) УСТРОЙСТВО ДЛЯ СТИРАНИЯ ИНФОРМАЦИЯ

В БЛОКАХ ПАМЯТИ НА МНОП-ТРАНЗИСТОРАХ

Изобретение относится к вычислительной технике, в частности к запоминающим устройствс1м (ЗУ) на МНОПтранзисторах.

Известно ЗУ на МНОП-транзисторах, в котором стирание информации ocsoaecтвляется с помощью адрескъзх формирователей. Устройство стирания включает в себя формирователи импульсов стирания, подключенные к адресным входам накопителя, дешифратор адреса и нагрузочные злементы на резисторах.

В исходном состоянии (при отсутствии обращения к накопителю)на еговхор,ах. удерживаются уровни напряжения,близкие к нулевым, за счет резисторов, подключенных к нулевой шине (отклонение уровней на входах .накопителя на МНОП-транзисторах может бытьвызвано лишь токами утечки и не превьлиает 1в) .

В режиме стирания информации по произвольному адресу, с дешифратора адреса запускается соответствующий формирователь стирания, который и обеспечивает стирание информации в выбранном адресе накопителя fj .

Недостатками устройства являются низкая надежность одновременного (общего) стирания информации из-за большогд количества формирователей стирания, большая потребляемая мощность в режиме общего стирания информации, так как при этом работают все формирователи одновременно.

Наиболее близким к предлагаемому является устройство, содержащее адресные формирователи, входы которых подключены к выходам дешифратора, а выходы - к входам накопителя и на10грузочным элементам, выполненным на резисторах 2 .

Цель изобретения - повышение надежности устройства и уменьшение потребляемой мощности в реж:1ме общего сти5 рания информации.

Поставленная цель достигается тем, что в устройство, содержащее адресные формирователи, входы которых подключены к выходам дешифратора,

20 а выходы - к входам накопителя и нагрузочным элементам, выполненным на резисторах, введены дополнительный адресный формирователь и ключ,выход1 которых объединеныи являются входом

25 запуска устройства,а выход дополнительного адресного формирователя подключен к другим выводам резисторов и через ключ - к шине нулевого потенциала.

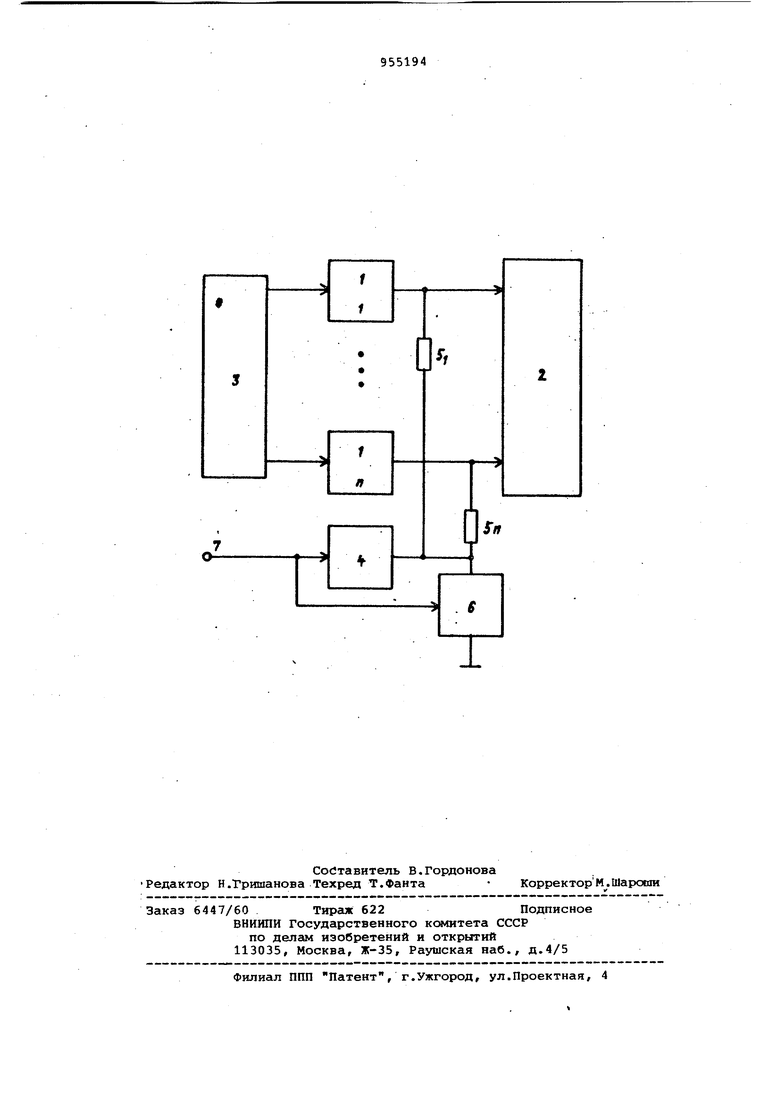

На чертеже представлена структур- .

30 Iная схема предлагаемого устройства.

. В его состав входят адресные формирователи 1 импульсов стирания, накогтитель 2, дешифратор 3 адреса, Дополнительный адресный формировател 4,нагрузочные элементы на резисторах

5и слюч 6.

Устройство работает следующим обрайом.

В режиме выборочного стирания клю

6открыт и нагрузочные резисторы 5 подключены к нулевой шине. В режиме общего стирания информации внешний сигнал запуска поступает на шину 1, .объединяющий входы дополнительного адресного формирователя 4 и ключа б, который при этом закрывается и импульсы стирания с выхода формирователя 4 подаются через резистрры 5

на входы накопителя. При этом производится стирание информации по всем адресам одновременно. Выборочное c-SK рание информации по отдельным адресам осуществляется также,, как и в устройстве, взятом за прототип, с по мощью формирователей 1, запускаелвлх с дешифратора 3 адреса,

В предлагаемом устройстве достигается более высокая надежность одновременного стирания информации в накопителе по всему массиву, так как используется только один формирователь импульсов стирания (Вместо п фо мирователей) и потребляемая мощность уменьшается в п раз. Возможное при этом уменьшение напряжения стирания на входах накопителя за счет падения напряжения на нагрузочных резисторах незначительно, так как определяется

лишь утечки j по адресным входам накопителя (амплитуда импульса напряжения стирания в накопителях на МНОП-транзисторах составляет 48В, а потери напряжения от токов утечки не превышают 1в).

Формула изобретения

Устройство для стирания информации в блоках памяти на МНОП-транзисторах, содержащее адресные формирователи, входы которых подключены к выходам дешифратора, а выходы - к входам накопителя и нагрузочным элементам, выполненным на резисторах, отличающееся тем, что, с целью порьшенпя надежности устройства и уменьшения потребляемой мощности в режиме общего стирания информации, оно содержит дополнительный : адресный формирователь и ключ, входы которых объединены и являются входом запуска устройства, а выход дополнительного адресного форфшрователя подключен к другим выводам резисторов и через ключ - к шине нулевого потенцигша. ,

Источники информации, принятые во внимание при экспертизе

1.Микросхема ПАЗУ с электрической сменой информации К519РБ2 (А,Б), изд-во ЦНИИ Электроника, 1976, с.50

2.интегральные микросхемы. Технический каталог. Изд-во ЦНИИ Электро1979, С.29 (прототип).

ника ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство записи и считывания информациидля НАКОпиТЕлЕй HA МНОп ТРАНзиСТОРАХ | 1979 |

|

SU830563A1 |

| Программируемое постоянное запоминающее устройство | 1980 |

|

SU886055A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1365133A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Программируемый элемент памяти | 1977 |

|

SU649035A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

Авторы

Даты

1982-08-30—Публикация

1981-01-27—Подача