ю

Oi

to ел

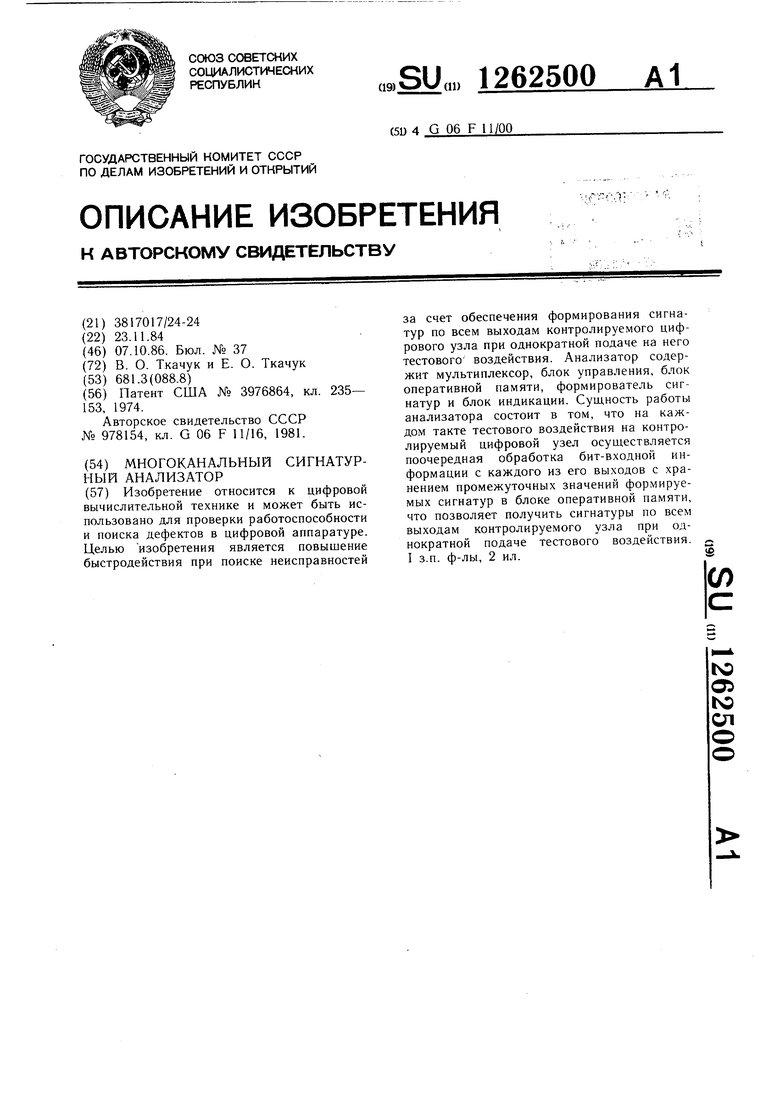

Изобретение относится к цифровой вычислительной технике и может быть использовано для проверки работоспособности и поиска дефектов в цифровой аппаратуре.

Целью изобретения является повышение быстродействия при поиске неисправностей за счет обеспечения формирования сигнатур по всем выходам контролируемого цифрового узла при однократной подаче на него тестового воздействия.

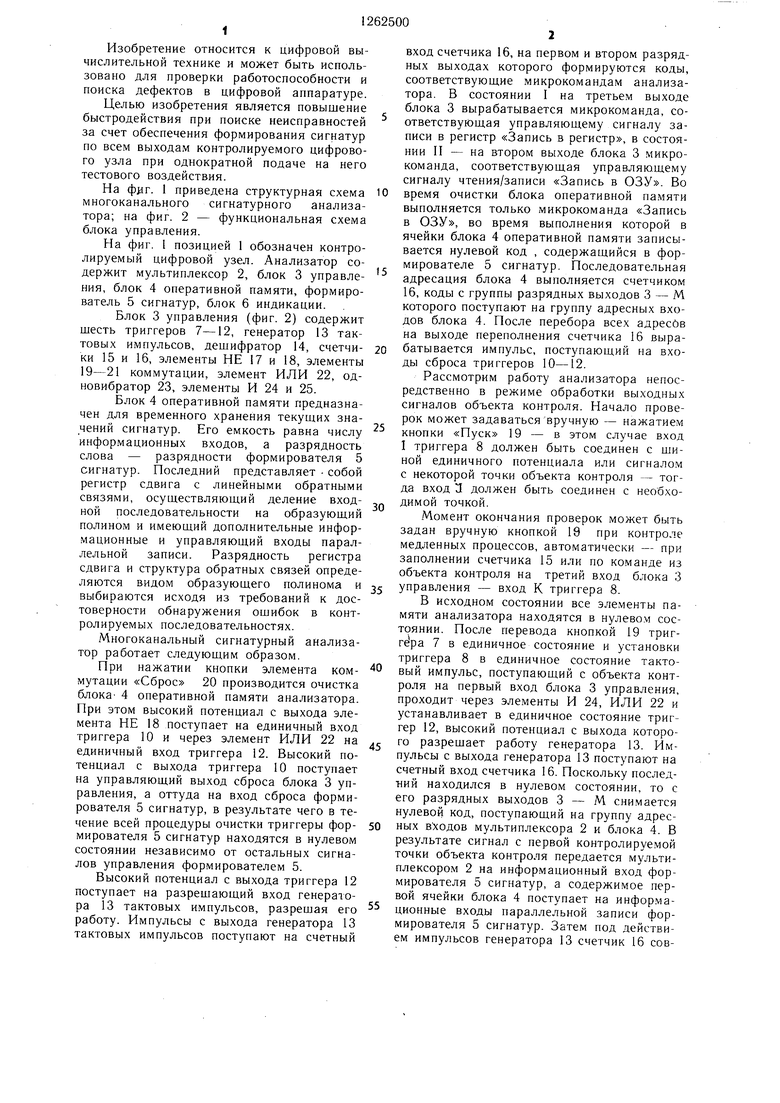

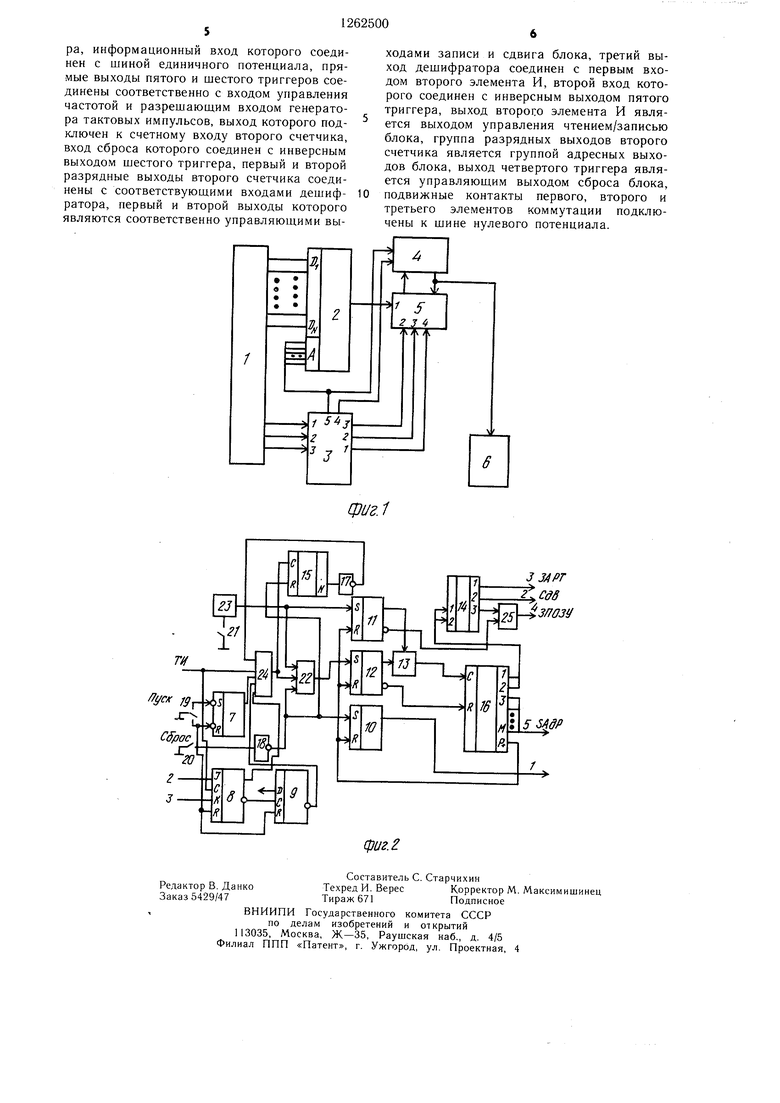

На флг. 1 приведена структурная схема многоканального сигнатурного анализатора; на фиг. 2 - функциональная схема блока управления.

На фиг. 1 позицией 1 обозначен контролируемый цифровой узел. Анализатор содержит мультиплексор 2, блок 3 управления, блок 4 оперативной памяти, формирователь 5 сигнатур, блок 6 индикации.

Блок 3 управления (фиг. 2) содержит шесть триггеров 7-12, генератор 13 тактовых импульсов, дешифратор 14, счетчики 15 и 16, элементы НЕ 17 и 18, элементы 19-21 коммутации, элемент ИЛИ 22, одновибратор 23, элементы И 24 и 25.

Блок 4 оперативной памяти предназначен для временного хранения текущих значений сигнатур. Его емкость равна числу информационных входов, а разрядность слова - разрядности формирователя 5 сигнатур. Последний представляет - собой регистр сдвига с линейными обратными связями, осуш,ествляюший деление входной последовательности на образуюший полином и имеющий дополнительные информационные и управляющий входы параллельной записи. Разрядность регистра сдвига и структура обратных связей определяются видом образующего полинома и выбираются исходя из требований к достоверности обнаружения ошибок в контролируемых последовательностях.

Многоканальный сигнатурный анализатор работает следующим образом.

При нажатии кнопки элемента коммутации «Сброс 20 производится очистка блока- 4 оперативной памяти анализатора. При этом высокий потенциал с выхода элемента НЕ 18 поступает на единичный вход триггера 10 и через элемент ИЛИ 22 на единичный вход триггера 12. Высокий потенциал с выхода триггера 10 поступает на управляющий выход сброса блока 3 управления, а оттуда на вход сброса формирователя 5 сигнатур, Б результате чего в течение всей процедуры очистки триггеры формирователя 5 сигнатур находятся в нулевом состоянии независимо от остальных сигналов управления формирователем 5.

Высокий потенциал с выхода триггера 12 поступает на разрешающий вход генераюра 13 тактовых импульсов, разрещая его работу. Импульсы с выхода генератора 13 тактовых импульсов поступают на счетный

вход счетчика 16, на первом и втором разрядных выходах которого формируются коды, соответствующие микрокомандам анализатора. В состоянии I на третьем выходе блока 3 вырабатывается микрокоманда, соответствующая управляющему сигналу записи в регистр «Запись в регистр, в состоянии II - на втором выходе блока 3 микрокоманда, соответствующая управляющему сигналу чтения/записи «Запись в ОЗУ. Во время очистки блока оперативной памяти выполняется только микрокоманда «Запись в ОЗУ, во время выполнения которой в ячейки блока 4 оперативной памяти записывается нулевой код , содержащийся в формирователе 5 сигнатур. Последовательная адресация блока 4 выполняется счетчиком 16, коды с группы разрядных выходов 3 - М которого поступают на группу адресных входов блока 4. После перебора всех адресбв на выходе переполнения счетчика 16 вырабатывается импульс, поступающий на входы сброса триггеров 10-12.

Рассмотрим работу анализатора непосредственно в режиме обработки выходных сигналов объекта контроля. Начало проверок может задаваться вручную - нажатием кнопки «Пуск 19 - в этом случае вход I триггера 8 должен быть соединен с шиной единичного потенциала или сигналом с некоторой точки объекта контроля - тогда вход U должен быть соединен с необходимой точкой.

Момент окончания проверок может быть задан вручную кнопкой 19 при контроле медленных процессов, автоматически - при заполнении счетчика 15 или по команде из объекта контроля на третий вход блока 3 управления - вход К триггера 8.

В исходном состоянии все эле.менты памяти анализатора находятся в нулевом состоянии. После перевода кнопкой 19 триггера 7 в единичное состояние и установки триггера 8 в единичное состояние тактовый импульс, поступающий с объекта контроля на первый вход блока 3 управления, проходит через элементы И 24, ИЛИ 22 и устанавливает в единичное состояние триггер 12, высокий потенциал с выхода которого разрешает работу генератора 13. Импульсы с выхода генератора 13 поступают на счетный вход счетчика 16. Поскольку последний находился в нулевом состоянии, то с его разрядных выходов 3 - М снимается нулевой код, поступающий на группу адресных входов мультиплексора 2 и блока 4. В результате сигнал с первой контролируемой точки объекта контроля передается мультиплексором 2 на информационный вход формирователя 5 сигнатур, а содержимое первой ячейки блока 4 поступает на информационные входы параллельной записи формирователя 5 сигнатур. Затем под действием импульсов генератора 13 счетчик 16 совместно с дешифратором 14 и элементом И 25 вырабатывает микрокоманды: «Запись в регистр, по которой код предыдущего состояния регистра данной контролируемой точки, выставленный блоком 4, записывается в формирователь 5; «Сдвиг, по которой состояние данной контролируемой точки сдвигается в формирователь 5, формируя новый код текущей сигнатуры; «Запись в ОЗУ, по которой полученное в результате сдвига новое состояние формирователя 5 записывается в блок 4 на место старого состояния. После выполнения всех микроопераций состояние разрядных выходов 3 - М счет.чика 16 увеличивается на единицу, и анализатор приступает к обработке значения сигнала в следующей контролируемой точке. Аналогично проводится обработка состояний всех контролируемых точек, после чего сигналом переполнения счетчика 16 триггер 12 сбрасывается и находится в таком состоянии до поступления следующего тактового импульса с выхода объекта контроля на первый вход блока 3. Сигналом об окончании проверки является заполнение счетчика 15 или установка в ноль триггера 8 и в единицу триггера 9, в результате чего на пятом или третьем и четвертом входах элемента И 24 устанавливается низкий логический потенциал, не допускающий прохождения тактовых импульсов. При нажатии оператором кнопки «Вывод 21 запускается одновибратор 23, который своим выходным импульсом устанавливает в единицу триггер 11 и через элемент ИЛИ 22 триггер 12. Высокий потенциал с прямого выхода триггера 11 поступает на вход управления частотой генератора 13 тактовых импульсов, вызывая снижение частоты тактовых импульсов. Низкий потенциал с инверсного выхода триггера 11 поступает на второй вход элемента И 25, запрещая выдачу микрокоманды «Запись в ОЗУ. Счетчик 16 последовательно перебирают адреса блока 4, причем на каждом такте работы содержимое выбранной ячейки передается в блок 6 индикации. После окончания переборка всех адресов импульс переполнения с выхода счетчика 16 устанавливает в исходное состояние триггеры. 11 и 12. В качестве блока 6 индикации может быть использовано печатающее устройство, алфавитно-цифроБОИ дисплеи или панель индикации. Формула изобретения I. Многоканальный сигнатурный анализатор, содержащий мультиплексор, блок управления, формирователь сигнатур и блок 55 индикации, причем группа информационных входов мультиплексора является группой информационных входов анализатора, группа адресных входов мультиплексора подключена к группе адресных выходов блока управле ния, выход мультиплексора соединен с информационным входом формирователя сигнатур, управляющие входы записи, сдвига и сброса которого соединены с соответствующими выходами блока управления, синхровход, вход запуска и вход останова блока управления являются соответствующими входами анализатора, отличающийся тем, что, с целью повышения быстродействия при поиске неисправностей, он содержит блок оперативной памяти, группа адресных входов которого соединена с группой адресных выходов блока управления, группа информационных входов - с группой выходов формирователя сигнатур, а группа выходов - с группой информационных входов параллельной записи формирователя сигнатур и группой входов блока индикации, вход чтения/записи блока оперативной памяти подключен к выходу управления чтением/ записью блока управления. 2. Анализатор по п. 1, отличающийся тем, что блок управления содержит шесть триггеров, два счетчика, два элемента И, элемент ИЛИ, генератор тактовых импульсов. дешифратор, одновибратор, два элемента НЕ и три элемента коммутации, причем единичный вход первого триггера соединен с замыкающим контактом первого элемента коммутации, размыкающий контакт которого соединен с входами сброса первого, второго и третьего триггеров, выход первого триггера соединен с первым входом первого элемента И, второй вход которого соединен с синхровходом второго триггера и является синхровходом блока, третий и четвертый входы первого элемента И соединены соответственно с инверсным выходом третьего и прямым выходом второго триггеров, пятый вход первого элемента И через первый элемент НЕ соединен с выходом первого счетчика, счетный вход которого соединен с выходом первого элемента И и первым входом элемента ИЛИ, вход сброса первого счетчика соединен с единичным входом четвертого триггера, вторым входом элемента ИЛИ и через второй элемент НЕ с замыкающим контактом второго элемента коммутации, третий вход элемента ИЛИ соединен с единичным входом пятого триггера и выходом одновибратора, вход которого подключен к замыкающему контакту третьего элемента коммутации, выход элемента ИЛИ соединен с единичным входом шестого триггера, входы сброса четвертого, пятого и шестого триггеров объединены и подключены к выходу переполнения второго счетчика, входы 3 и К второго триггера являются соответственно входами запуска и останова блока, инверсный выход второго триггера соединен с синхровходом третьего тригге

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1987 |

|

SU1520521A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1529221A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для проверки работоспособности и поиска дефектов в цифровой аппаратуре. Целью изобретения является повышение быстродействия при поиске неисправностей за счет обеспечения формирования сигнатур по всем выходам контролируемого цифрового узла при однократной подаче на него тестового воздействия. Анализатор содержит мультиплексор, блок управления, блок оперативной памяти, формирователь сигнатур и блок индикации. Сущность работы анализатора состоит в том, что на каждом такте тестового воздействия на контролируемый цифровой узел осуществляется поочередная обработка бит-входной информации с каждого из его выходов с хранением промежуточных значений формируемых сигнатур в блоке оперативной памяти, что позволяет получить сигнатуры по всем выходам контролируемого узла при однократной подаче тестового воздействия. (С I з.п. ф-лы, 2 ил.

| Патент США № 3976864, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1984-11-23—Подача