-)

Изобретение относится к области вычислительной техники и может быть использовано в составе гибридных вычислительных машин при организации итерационных процедур в функциональных пространствах.

Известны магнитные аналоговые запоминающие устройства временных функций, предназначенные для записи и последующего воспроизведения различных непрерывных процессов, протекающих по времени и содержащие в качестве накопителей информации либо подвижные носители (магнитный барабан, лента) либо цепочки магнитных аналоговых элементов памяти, управляемых внешним коммутатором I.

Наиболее близким техническим решением является аналоговое запоминающее устройство, содержащее блок памяти, соединенный с формирователями импульсов считывания, один из которых связан со сдвиговым регистром и с формирователями импульсов записи, одни из которых связаны с распределителем импульсов, подключенным к шинам «сдвиг влево и «сдвиг вправо, сдвиговому регистру и выходу первого элемента И, первый вход которого соединен с шиной «запись и генератором импульсов, второй вход - с первым элементом задержки, связанным с генератором импульсов, подключенным к шине «считывание, и со сдвиговым регистром непосредственно и через второй элемент задержки, выпрямитель, соединенный с блоком памяти и через фильтр низких частот с выходом устройства и блоком вычитания, связанным с блоком памяти, подключенным к шине сброса, и входом устройства 2.

Такое устройство предназначено для запоминания функции

Y f (t),

t е tK, t,,

где t - время,

t( - начальная точка замкнутого интервала,

IK - конечная точка интервала, и производит автоматическое квантование интервала на ш равных частей m + 1 точками

to ta.tj Да,..., t „-/ , tr,, tn4i ,..., tm-i, tjj, i.

Процесс запоминания представляет собой последовательную выборку информации о характере функции в точках последовательности и запись ее в запоминающие ячейки (разряды) накопителя, число которых равно числу точек квантования.

Однако на практике, при организации итерационных процедур в функциональных пространствах часто имеют место случаи, когда направление изменения аргумента функции при

считывании противоположно направлению изменения аргумента при записи, т.е. имеют место операции считывания с реверсом времени. Выполнение таких операций известным устрой- . ством невозможно, что сужает его возможности.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения выполнения дополнительных операций считывания с реверсом времени.

Это достигается тем, что предлагаемое устройство содержит блок коммутации, второй, третий и четвертый элементы И и триггер признака записи, один из входов которого подключен к шине сброса, второй вход - к выходу второго элемента И, первый вход которого соединен с шиной «запись, второй вход его - с шиной «сдвиг влево, первый выход триггера признака записи подключен к одному из входов третьего элемента И, другой вход которого подключен к шине «сдвиг вправо, выход его - к блоку коммутации и сдвиговому регистру, второй выход триггера признака записи подключен к первому входу четвертого элемента И, второй вход которого подключен к шипе «сдвиг влево, блоку коммутации и сдвиговому регистру, выход его - к сдвиговому регистру и блоку коммутации, связанному с блоком памяти, формирователями и.мпульсов считывания, другими формирователями импульсов записи, распределителем импульсов и сдвиговым регистром.

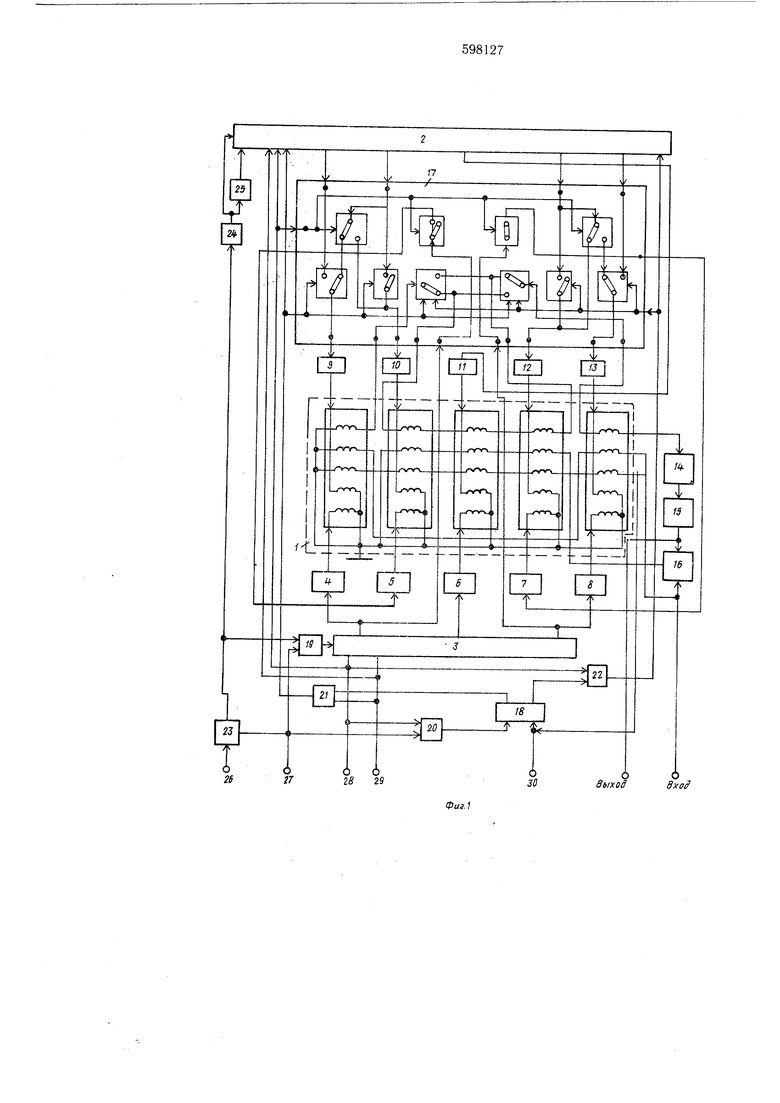

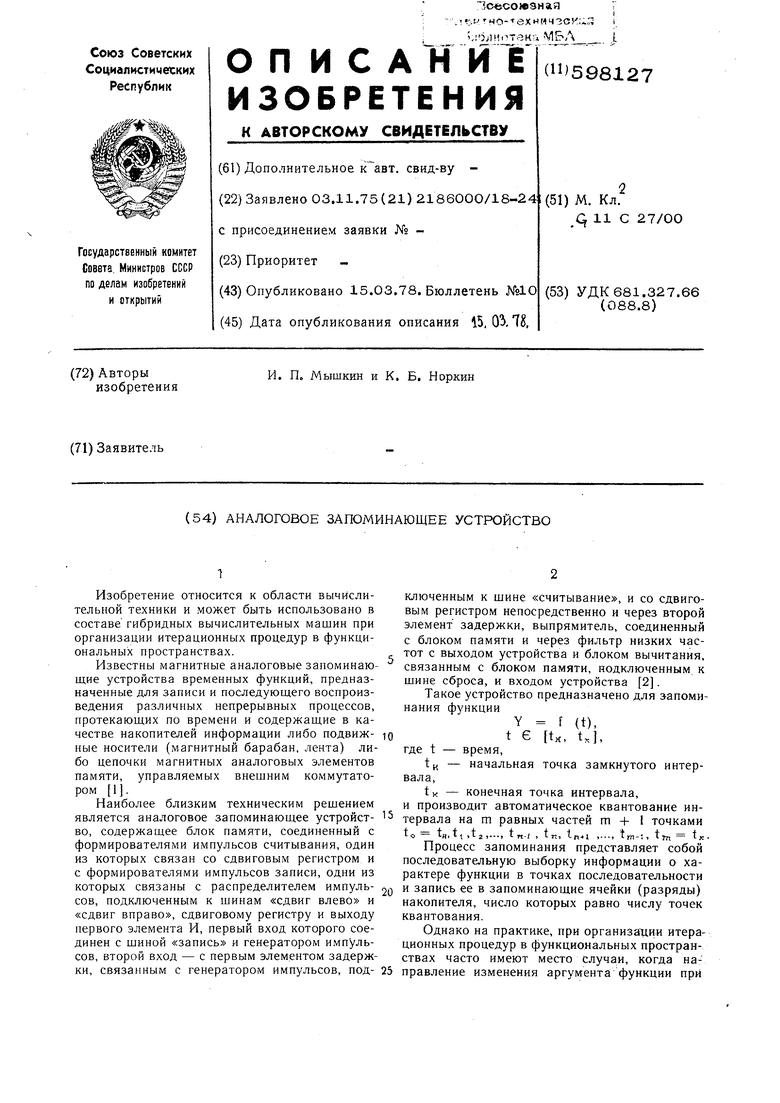

На фиг. 1 представлена блок-схема аналогового запоминающего устройства; на фиг. 2 - пример запоминаемой функции Y f (t) для пояснения работы устройства.

Устройство содержит блок памяти 1, сдвиговый регистр 2, распределитель импульсов 3, формирователи 4-8 импульсов записи, формирователи 9-13, импульсов считывания, выпрямитель 14, фильтр 15 низких частот, 16 вычитания, блок коммутации 17, собранный на управляемых ключах и переключателях, триггер 18 признака записи, элементы И 19-22, генератор 23 импульсов, элементы 24 и 25 задержки и шины считывания 26, записи 27 и «сдвиг влево 28, «сдвиг вправо 29 и сброса 30.

Устройство работает в следующих режимах: режим прямой записи, режим обратной записи, режим прямого считывания прямо записанной функции, режим обратного считывания обратно записанной функции, режим прямого считывания обратно записанной функции, режим обратного считывания прямо записанной функции.

Рассмотрим в качестве примера работу устройства в режиме прямой записи.

Перед записью информации на шину сброса 30 подается импульс, который все запоминающие ячейки блока памяти 1 ставит в исходное состояние. В исходное состояние ставится также триггер 18.Регистр 2 и распределитель 3 очищены. На шинах «считывания 26 и «сдвиг влево 28,сигналы управления отсутствуют. На LiniHy «сдвиг вправо. 29 подана команда, поэтому решстр 2 и распределитель 3 подготовлены для работы в режиме сдвига

вправо. Выходные сигналы элементов И 21 и 22 имеют низкий уровень, лоэтому входной сигнал может сразу пройти на единичный вход второго разряда.

, При записи одновременно с подачей на вход устройства запоминаемой функции Y f (t) на шину «запись 27 подается сигнал управления. Этот сигнал запускает генератор 23, разрешает прохождение импульсов генератора на вход распределителя 3 и поступает на вход 0 элемента И 20. ,Первый импульс генератора, поступая на распределитель, вызывает срабатывание формирователя 4, который вырабатывает короткий импульс тока. При этом в запоминающую ячейку блока па.мяти 1 записывается значение функции Y f (tl (фиг. 2) в момент времени t 0. Первый же импульс генератора через время, определяемое параметрами элемента 24 задержки, производит запись единицы в регистр 2. При этом единица проходит сразу на второй разряд. Тогда выходf НОЙ сигнал второго разряда регистра 2 через блок 17 подается на вход формирователя 9, который начинает работать в режиме непрерывной генерации импульсов тока. Эти импульсы опрашивают состояние запоминающей ячейки. В результате на вход выпрямителя 14 посту5 пает последовательность импульсов, соответствующая состоянию первой ячейки блока памяти. Эта последовательность выпрямляется выпрямителем 14, сглаживается фильтром 15 и поступает на вход блока вычитания 16, который производит вычисление разности текущего значения функции Y f (t) и значения этой же функции в момент t 0. К моменту прихода второго импульса генератора с выхода блока вычитания 16 на блок памяти 1 будет . подаваться приращение значения функции 5 Y f ( I ) в момент t 1 по отношению к значению той же функции в момент t 0. С приходом второго импульса генератора на распределитель срабатывает формирователь 6 и это приращение запишется в соответствующую ячейку блока 1. Сразу за записью информа0 ции в регистре 2 производится сдвиг (вправо) и запись новой единицы. При этом сдвиг осуществляется первым импульсом генератора, за-. держанным элементом 25 задержки, а запись новой единицы производится вторым импульсом генератора 23 (тем самым происходит заполнение регистра единицами, что необходимо для удержания уже запущенных в предыдущие такты формирователей импульсов считывания в состоянии генерации). Теперь опрашиваются уже две запоминающие ячейки, в результате на выходе фильтра 15 образуется напряжение, равное значению функции Y f (t) в момент времени t . К приходу третьего импульса генератора с выхода блока вычитания 16 снимается напряжение, равное приращению функции Y f (t) в момент t 2 по отношению к моменту t 1. В дальнейшем, если бы точка t 2 была внутренней точкой временного интервала, процесс запоминания протекал бы ана логично. Однако в данном случае точка t 2 является крайней точкой и поэтому работу последнего (третьего) разряда накопителя следует описать отдельно. С приходом третьего импульса на распределитель 3 запускаются формирователи 7 и 8. При этом в одну соответствующую запоминающую ячейку записывается приращение, а в другую запоминающую ячейку - полное значение функции в момент t 2. Сразу за записью информации в третий разряд накопителя в регистре 2 происходит сдвиг (вправо) записанных ранее единиц (задержанных в элементе 25 вторым импульсом) и запись новой единицы (третьим импульсом), запускается формирователь 12 через замкнутые контакты переключателя блока 17. В результате опращиваются одновременно соответствующие ячейки и на выходе фильтра образуется напряжение, равное значению функции Y f (t) в момент t 2.

На этом Процесс прямой записи заканчивается. Генератор 37 останавливается, регистр б и распределитель приводятся в исходное состояние. Триггер 32 сохраняет то состояние, в которое он был поставлен перед записью, т.е. хранит признак записи.

Далее наступает режим хранения информации.

Формула изобретения

Аналоговое запоминающее устройство, содержащее блок памяти, соединенный с формирователями импульсов считывания, один из которых связан со сдвиговым регистром и с формирователями импульсов записи, одни из которых связаны с распределителем импульсов, подключенным к щинам «сдвиг влево и «сдвиг вправо, сдвиговому регистру и выходу первого элемента И, первый вход которого соединен с щиной «запись и генератором импульсов, второй вход - с первым элементом задержки, связанным с генератором импульсоа, подключенным к щине «считывание, и со сдвиговым регистром непосредственно и через второй элемент задержки, выпрямитель, соединенный с блоком памяти и через фильтр низких частот с выходом устройства и блоком вычитания, связанным с блоком памяти, подключенным к щине сброса, и входом устройства, отличающееся тем, что, с целью расщирения функциональных возможностей устройства, оно содержит блок коммутации, второй, третий и четвертый элементы И и триггер признака записи, один из входов которого подключен к шине сброса, второй вход - к выходу второго элемента И, первый вход которого соединен с щиной «запись, второй вход его - с шиной

5 «сдвиг влево, первый выход триггера признака записи подключен к одному из входов третьего элемента И, другой вход которого подключен к щине «сдвиг вправо, выход его - к блоку коммутации и сдвиговому регистру, второй вы ход триггера признака записи подключен к первому входу четвертого элемента И, второй вход которого подключен к щине «сдвиг влево, блоку коммутации и сдвиговому регистру, выход его - к сдвиговому регистру и блоку коммутации, связанному с блоком памяти, формирователями импульсов считывания, другими формирователями импульсов записи, распределителем импульсов и сдвиговым регистром.

Источники информации, принятые во внимание при экспертизе;

1.Витенберг И. М. и др. Запоминающее устройство для АВМ ЗУАМ-К, сб. «Вопросы

радиоэлектроники,серия «Электронная вычислительная техника, выпуск 11, 1971, с. 94.

2.Сидоров В. М. Магнитные аналоговые запоминающие устройства временных функций,

сб. «Магнитные элементы непрерывного дейстВИЯ, М., 1972, с. 140.

f

| название | год | авторы | номер документа |

|---|---|---|---|

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Устройство для сопряжения | 1979 |

|

SU842772A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386442A1 |

| Устройство для управления записью и считыванием информации | 1981 |

|

SU1014028A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для сопряжения | 1977 |

|

SU739516A1 |

| Устройство для считывания и отображения графической информации | 1982 |

|

SU1084839A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

Авторы

Даты

1978-03-15—Публикация

1975-11-03—Подача