{5) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Устройство для деления @ -разрядных чисел | 1984 |

|

SU1223224A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления | 1988 |

|

SU1621034A1 |

| Асинхронное матричное устройство для деления | 1982 |

|

SU1022157A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин последовательного действия.

Известно устройство для деления последовательного типа, которое содержит сдвиговые регистры, схему округления, схему определения знлка, сумматор, логические элементы и триггеры l.

Известно также двоичное устройство для деления, содержащее сдвиговые регистры с параллельной записью информации, два одноразрядных сумматора-вычислителя последовательного действия, блок анализа.знаков, блок анализа сходимости процесса, логические элементы 2.

Однако принцип работы таких устройств не позволяет в полной мере использовать в нем динамические регистры с большой степенью интеграции, требует больших аппаратурных затрат.

Наиболее близким по технической сущности к изобретению является устройство для деления чисел последовательного типа, содержащее регистры делителя, делимого, частотного, одноразрядный сумматор, триггер, два логических элемента И, логический элемент И-ИЛИ, причем выход регистра делителя соединен с его входом, выход регистра частного соединен с первым

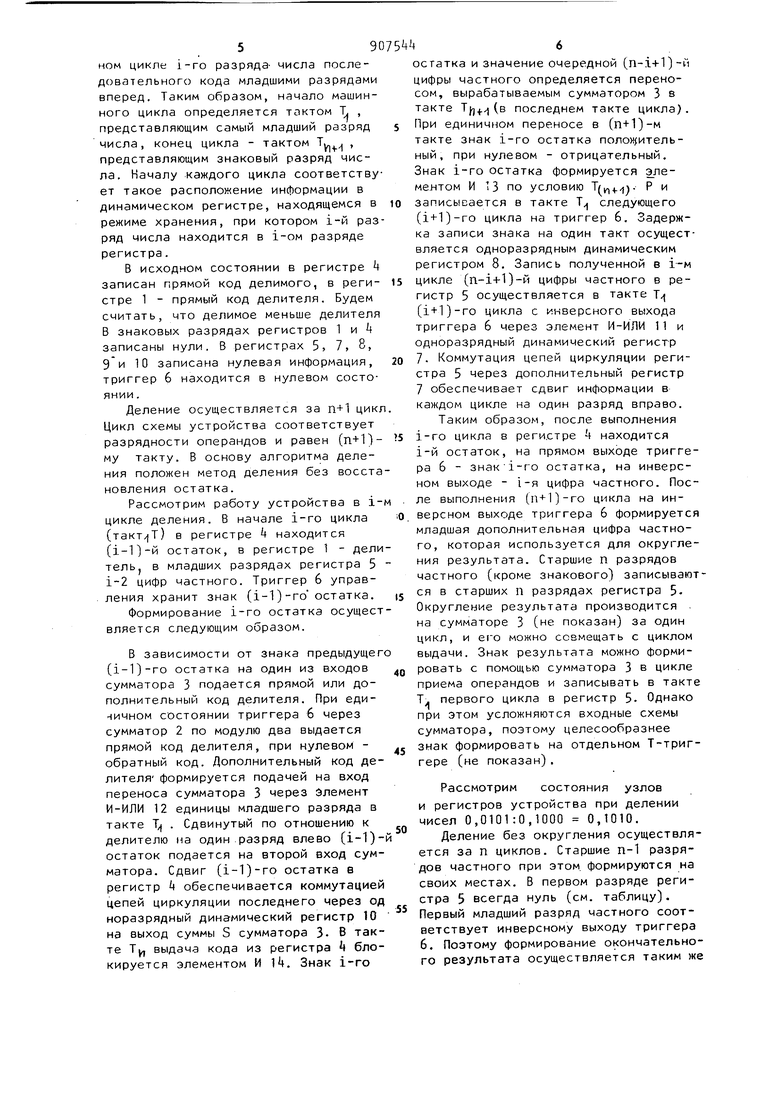

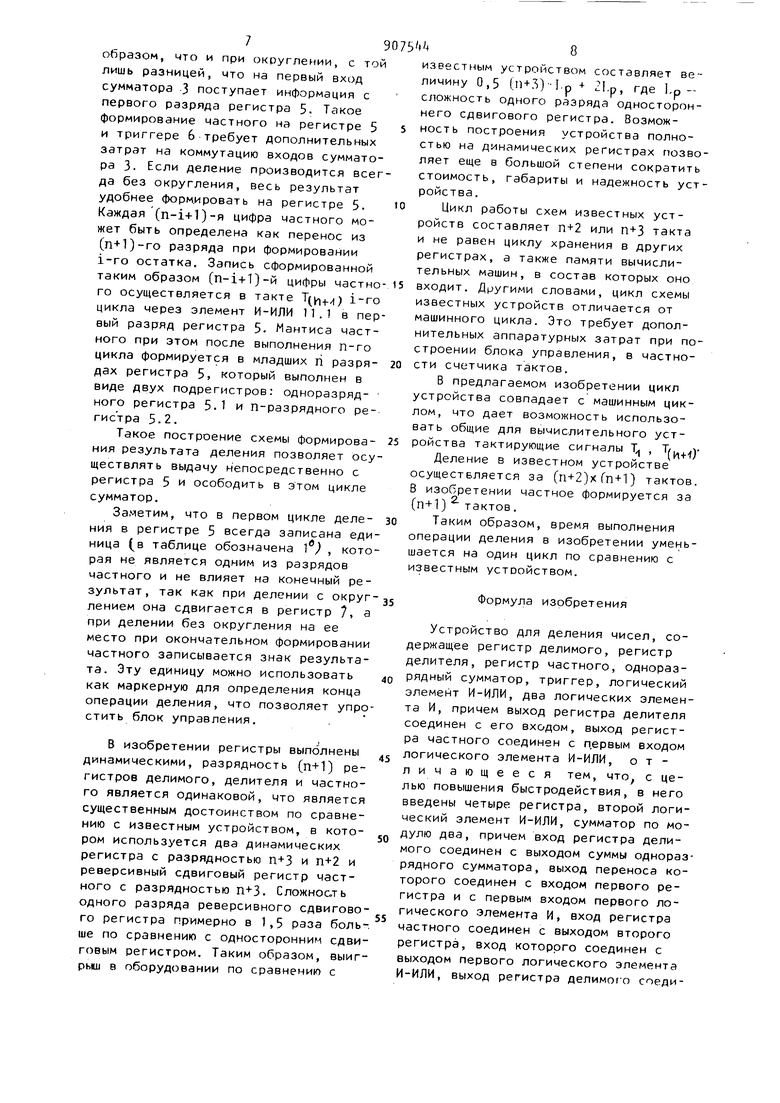

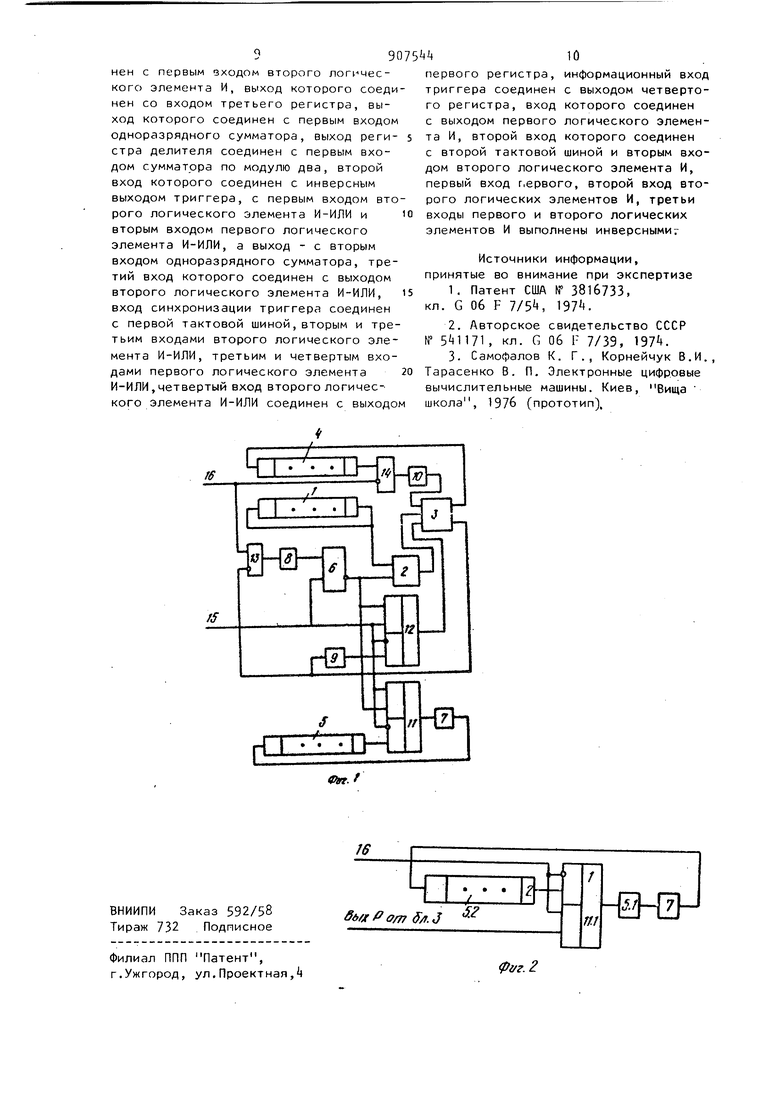

10 входом логического элемента И-ИЛИ. В устройстве в каждом цикле определяется одна цифра частного, которая записывается в реверсивный статический сдвиговый регистр. Цикл схемы устройства составляет (п+2) такта fЗ. Недостатками данного устройства является невысокое быстродействие и большие аппаратурные затраты, связанные с длиной регистров делимого и де20лителя, невозможностью использования в нем в полной мере динамических регистров с большей степенью интеграции. Цель изобретения - повышение быст родействия. Поставленная цель достигается тем что в устройство для деления введены четыре регистра, второй логический элемент И-ИЛИ, сумматор по модулю два, причем вход регистра делимого соединен с выходом суммы одноразрязного сумматора, выход переноса которого соединен с входом первого регистра и с первым входом первого логического элемента И, вход регистра частного соединен с выходом второго регистра, вход которого соединен с выходом первого логического элемента И-ИЛИ, выход регистра делимого соеди нен с первым входом второго логического элемента И, выход которого соед нен со входом третьего регистра, выход которого соединен с первым входом 20 одноразрядного сумматорй, выход реги стра делителя соединен с первым входом сумматора по модулю два, второй вход которого соединен с инверсным выходом триггера, с первым входом второго логического элемента И-ИЛИ и вторым входом первого логического элемента И-ИЛИ, а выход - с вторым входом одноразрядного сумматора, третий вход которого соединен с выходом второго логического элемента И-ИЛИ, вход синхронизации триггера соединен с первой тактовой шиной, вторым и тре тьим входами второго логического элемента И-ИЛИ, третьим и четвертым входами первого логического элемента ИИЛИ, четвертый вход второго логического элемента И-ИЛИ соединен с выходом первого регистра, информационный вход триггера соединен с выходом четвертого регистра, вход которого соединен с выходом первого логического элемента И, второй вход которого соединен с второй тактовой шиной и вторым входом второго логического элемен та И, первый вход первого, второй вход второго логических элементов И, третьи входы первого и второго логических элементов И выполнены инверсными , На фиг. 1 представлена функциональная схема предлагаемого устройст ва; на фиг. 2 - вариант построения регистра частного. . Устройство содержит п+1-разрядный. (п - разрядность мантисы, 1 - разрядность представления знака) регистр делителя 1, сумматор 2 по модулю два одноразрядный сумматор 3 последовательного действия, п+1-разрядные регистры делимого k и частного 5, CDтриггер 6 управления, первый 7, второй 8, третий 9 и четвертый 10 одноразрядные (динамические ) регистры, первый и второй элементы И-ИЛИ 11 и 12, первый и второй логические элементы И 13 и 1, первую и вторую тактовые шины 15 и 1б. Выход регистра 4 делимого соединен с его входом, выход регистра 5 частного соединен с первым входом логичес кого элемента И-ИЛИ 11, вход регистра k делимого соединен с выходом суммы одноразрядного сумматора 3, выход переноса которого соединен с входом регистра 9 и с первым входом логического элемента И 13, вход регистра 5 частного соединен с выходом регистра 7, вход которого соединен с выходом логического элемента И-ИЛИ 11, выход регистра делимого соединен с первы,входом логического элемента И 14, выход которого соединен с входом регистра 10, выходом соединенного с первым входом одноразрядного сумматора 3, выход регистра 1 делителя соединен с первым входом сумматора 2 по модулю два, второй вход которого соединен с инверсным выходом триггера 6, с первым входом .логического элемента И-ИЛИ 12 и вторым входом логического элемента И-ИЛИ 11, а выход с вторым входом одноразрядного сумматора 3, третий вход которого соединен с выходом логического элемента И-ИЛИ 12, вход синхронизации триггера 6 соединен с тактовой иииной 15, вторым и третьим входами логического элемента И-ИЛИ 12, третьим и четвертым входами логического элемента 11, четвертый вход логического элемента И-ИЛИ 12 соединен с выходом регистра Э, информационный вход триг гера 6 соединен с выходом регистра 8, вход которого соединен с выходом логического элемента И 13, вторым входом соединенного с тактовой шиной 1б и вторым входом Логического элемента И И, первый вход логическэго элемента И 13, второй вход логическо го элемента И 14, третьи входы логических элементов И-ИЛИ 11 и 12 выполнены, инверсными. Устройство работает следующим образом. Тактом будем называть временной интервал представления в машинном цикле i-ro разряда- числа последовательного кода младшими разрядами вперед. Таким образом, начало машинного цикла определяется тактом Т. , представляющим самый младший разряд числа, конец цикла - тактом Т,,.. , представляющим знаковый разряд числа. Началу каждого цикла соответству ет такое расположение информации в динамическом регистре, находящемся в режиме хранения, при котором 1-й раз ряд числа находится в i-ом разряде регистра. В исходном состоянии в регистре k записан прямой код делимого, в регистре 1 - прямый код делителя. Будем считать, что делимое меньше делителя 8знаковых разрядах регистров 1 и h записаны нули. В регистрах 5, 7, 8, 9и 10 записана нулевая информация, триггер 6 находится в нулевом состоянии . Деление осуществляется за п+1 цикл Цикл схемы устройства соответствует разрядности операндов и равен (n-f-1)му такту. В основу алгоритма деления положен метод деления без восста новления остатка. Рассмотрим работу устройства в 1цикле деления. В начале i-ro цикла (такт/|Т) а регистре находится (i-11-й остаток, в регистре 1 - дели тель, в младших разрядах регистра 5 i-2 цифр частного. Триггер 6 управления хранит знак (i-1)-го остатка. Формирование i-ro остатка осущест вляется следующим образом. В зависимости от знака предыдущег (i-1)-го остатка на один из входов сумматора 3 подается прямой или дополнительный код делителя. При единичном состоянии триггера 6 через сумматор 2 по модулю два выдается прямой код делителя, при нулевом обратный код. Дополнительный код делителя формируется подачей на вход переноса сумматора 3 через Элемент И-ИЛИ 12 единицы младшего разряда в такте Т . Сдвинутый по отношению к делителю на один разряд влево (1-1)остаток подается на второй вход сумматора. Сдвиг (i-l)-ro остатка в регистр А обеспечивается коммутацией цепей циркуляции последнего через од поразрядный динамический регистр 10 на выход суммы S сумматора 3- В такте Ту выдача кода из регистра Ц блокируется элементом И 1. Знак 1-го остатка и значение очередной (п-1+1)-й цифры частного определяется переносом, вырабатываемым сумматором 3 в такте Т (в последнем такте цикла). При единичном переносе в (п+1)-м такте знак i-ro остатка полои ительный, при нулевом - отрицательный. Знак i-ro остатка формируется элементом И 13 по условию T(ti+.-l)- Р и записывается в такте Т следующего (i-t-l)-ro цикла на триггер 6. Задержка записи знака на один такт осуществляется одноразрядным динамическим регистром 8. Запись полученной в i-м цикле (n-i+1)-й цифры частного в регистр 5 осуществляется в такте т, (i+1)-ro цикла с инверсного выхода триггера 6 через элемент И-ИЛИ 11 и одноразрядный динамический регистр 7. Коммутация цепей циркуляции регистра 5 через дополнительный регистр 7 обеспечивает сдвиг информации в каждом цикле на один разряд вправо. Таким образом, после выполнения i-ro цикла в регистре находится остаток, на прямом выходе триггера 6 - знак1-го остатка, на инверс ° выходе - i-я цифра частного. После выполнения ( цикла на инверсном выходе триггера 6 формируется младшая дополнительная цифра частного, которая используется для округле результата. Старшие п разрядов частного (кроме знакового) записываются в старших п разрядах регистра 5Округление результата производится . на сумматоре 3 (не показан) за один цикл, и eio можно совмещать с циклом выдачи. Знак результата можно формировать с помощью сумматора 3 в цикле приема операндов и записывать в такте Т. первого цикла в регистр 5- Однако при этом усложняются входные схемы сумматора, поэтому целесообразнее знак формировать на отдельном Т-триггере (не показан). Рассмотрим состояния узлов и регистров устройства при делении чисел 0,0101:0,1000 0,1010. Деление без округления осуществляется за п циклов. Старшие п-1 разрядов частного при этом, формируются на своих местах. В первом разряде регистра 5 всегда нуль (см. таблицу). Первый младший разряд частного соответствует инверсному выходу триггера 6. Поэтому формирование окончательного результата осуществляется таким же

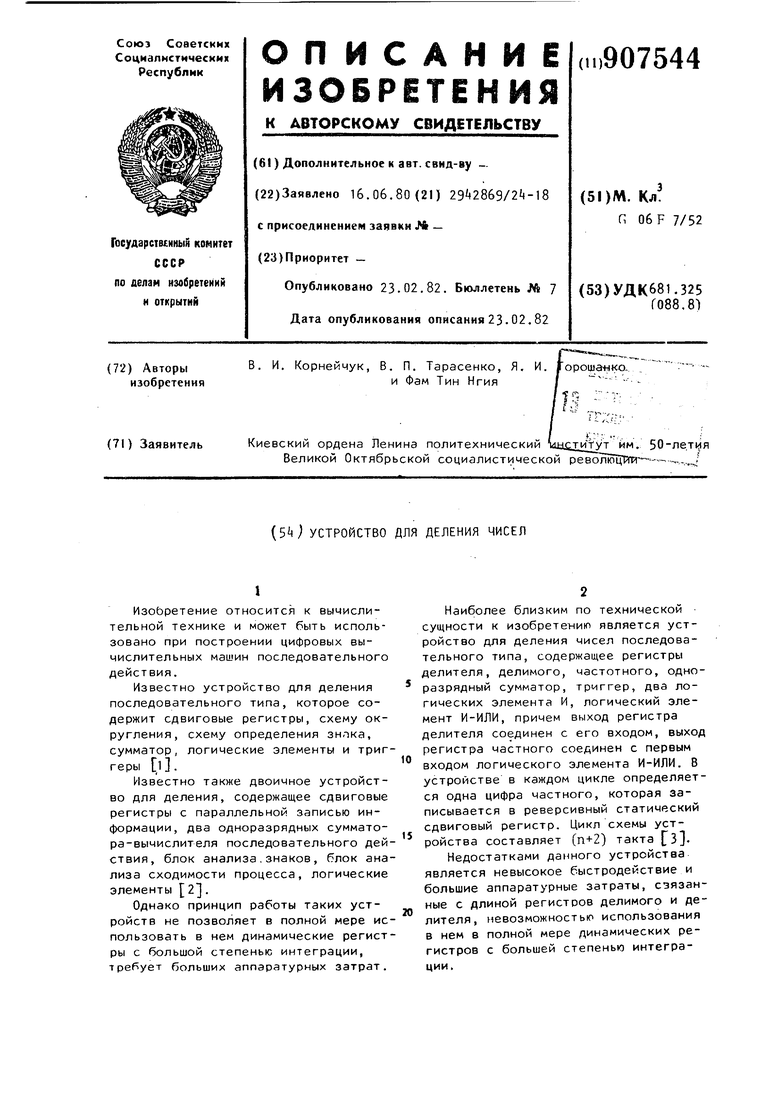

образом, что и при округлении, с той лишь разницей, что на первый вход сумматора 3 поступает информация с первого разряда регистра 5. Такое формирование частного на регистре 5 и триггере 6 требует дополнительных затрат на коммутацию входов сумматора 3. Если деление производится всегда без округления, весь результат удобнее форм.ировать на регистре 5. Каждая (п-1+1)-я цифра частного может быть определена как перенос из (п+1)-го разряда при формировании i-ro остатка. Запись сформированной таким образом (п-1+1)-й цифры частного осуществляется в такте ) i-ro цикла через элемент И-ИЛИ 11.1 в первый разряд регистра 5. Мантиса частного при этом после выполнения п-го цикла формируется в младших п разрядах регистра 5, который выполнен в виде двух подрегистров: одноразрядного регистра 5.1 и п-разрядного регистра 5.2.

Такое построение схемы формирования результата деления позволяет осуществлять выдачу непосредственно с регистра 5 и осободить в этом цикле сумматор.

Заметим, что в первом цикле деления в регистре 5 всегда записана единица (в таблице обозначена 1 ) , которая не является одним из разрядов частного и не влияет на конечный результат, так как при делении с округлением она сдвигается в регистр 7, а при делении без округления на ее место при окончательном формировании частного записывается знак результата. Эту единицу можно использовать как маркерную для определения конца операции деления, что позволяет упростить блок управления.

В изобретении регистры выполнены динамическими, разрядность (п+1) регистров делимого, делителя и мастного является одинаковой, что является существенным достоинством по сравнению с известным устройством, в котором используется два динамических регистра с разрядностью п+З и п+2 и реверсивный сдвиговый регистр частного с разрядностью п+3. Сложность одного разряда реверсивного сдвигового регистра примерно в 1,5 раза больше по сравнению с односторонним сдвиговым регистром. Таким образом, выигрыш в оборудовании по сравнению с

известным устройством составляет величину 0,5 (n + .3)-J.p + 2.р, где 1,рсложность одного разряда одностороннего сдвигового регистра. Возможность построения устройства полностью на динамических регистрах позволяет еще в большой степени сократить стоимость, габарить и надежность устройства.

Цикл работы схем известных устройств составляет п+2 или п+3 такта и не равен циклу хранения в других регистрах, а также памяти вычислительных машин, в состав которых оно

входит. Другими словами, цикл схемы известных устройств отличается от машинного цикла. Это требует дополнительных аппаратурных затрат при построении блока управления, в частности счетчика тактов.

В предлагаемом изобретении цикл устройства совпадает с машинным циклом, что дает возможность использовать общие для вычислительного устройства тактирующие сигналы I, ,

Деление в известном устройстве осуществляется за (п+2)хГп+1) тактов. В изобретении частное формируется за (п+1) тактов.

Таким образом, время выполнения операции деления в изобретении уменьшается на один цикл по сравнению с известным УСТРОЙСТВОМ.

Формула изобретения

35

Устройство для деления чисел, содержащее регистр делимого, регистр делителя, регистр частного, одноразрядный сумматор, триггер, логический элемент И-ИЛИ, два логических элемента И, причем выход регистра делителя соединен с его входом, выход регистра частного соединен с первым входом

логического элемента И-ИЛИ, отличающееся тем, что с целью повышения быстродействия, в него введены четыре регистра, второй логический элемент И-ИЛИ, сумматор по модулю два, причем вход регистра делимого соединен с выходом суммы одноразрядного сумматора, выход переноса которого соединен с входом первого регистра и с первым входом первого логического элемента И, вход регистра частного соединен с выходом второго регистра, вход которого соединен с выходом первого логического элемента И-ИЛИ, выход регистра делимого соединен с первым зходом второго логического элемента И, выход которого соединен со входом третьего регистра, выход которого соединен с первым входом одноразрядного сумматора, выход регистра делителя соединен с первым входом сумматора по модулю два, второй вход которого соединен с инверсным выходом триггера, с первым входом второго логического элемента И-ИЛИ и вторым входом первого логического элемента И-ИЛИ, а выход - с вторым входом одноразрядного сумматора, третий вход которого соединен с выходом второго логического элемента И-ИЛИ, вход синхронизации триггера соединен с первой тактовой шиной, вторым и третьим входами второго логического элемента И-ИЛИ, третьим и четвертым входами первого логического элемента И-ИЛИ,четвертый вход второго логического элемента И-ИЛИ соединен с выходо

Ц I-.

fff

первого регистра, информационный вход триггера соединен с выходом четвертого регистра, вход которого соединен с выходом первого логического элемента И, второй вход которого соединен с второй тактовой шиной и вторым входом второго логического элемента И, первый вход г.ервого, второй вход второго логических элементов И, третьи входы первого и второго логических элементов И выполнены инверсными

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-02-23—Публикация

1980-06-16—Подача