(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Устройство для деления | 1980 |

|

SU898425A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин последовательного действия.

Известно устройство для деления последовательного типа, схема которого содержит сдвиговые регистры, схему округления, схему определения знака, сумматор, логические элементы, триггеры 1.

Недостатком работы такого устройства является то, что оно не позволяет в полной мере использовать в нем динамические регистры с большой степенью интеграции и требует больших аппаратурных затрат.

Наиболее близким к предлагаемому по технической суш,ности является устройство для деления чисел последовательного действия, содержаш.ее регистры делителя, делимого и частного, одноразрядный сумматор

последовательного действия, триггер, сумматор по МОДУЛЮ два, логические элементы И и И-ИЛИ. В таком устройстве в каждом цикле определяется одна цифра частного, которая записывается в регистр частного. Цикл схемы устройства составляет п+1

такт (п - разрядность мантиссы операндов) 2.

Недостатками известного устройства являются невысокое быстродействие и большие аппаратурные затраты, связанные с увеличенной длиной регистров делимого, делителя и частного, не соответствующей разрядности обрабатываемых чисел.

Цель изобретения - повышение быстродействия и сокращение аппаратурных затрат.

Поставленная цель достигается тем, что устройство для деления чисел, содержащее регистры делителя, делимого и частного, первый сумматор по модулю два, одноразрядный сумматор, элемент И, одноразрядные регистры, элементы И-ИЛИ и триггер управления, причем вход и выход регистра делителя объединены и подключены к первому входу первого сумматора по модулю два, выход которого подключен к первому входу одноразрядного сумматора, выход суммы которого соединен с входом регистра делимого, выход которого соединен с первым входом элемента И, выход которого подключен к входу первого одноразрядного регистра, выход которого подключен к второму входу одноразрядного сумматора, выход переноса которого подключен к входу второго одноразрядного регистра., выход которого соединен с первым информационным входом первого элемента И-ИЛИ, выход которого подключен к третьему входу одноразрядного сумматора, второй вход первого сумматора по модулю два и второй информационный вход первого элемента И-ИЛИ соединены с инверсным выходом триггера управления, С-вход которого соединен с управляющими входами первого элемента И-ИЛИ и с первой тактовой шиной устройства, второй вход элемента И соединен с второй тактовой шиной устройства, выход регистра частного соединен с первым информационным входом второго элемента И-ИЛИ, выход которого соединен с входом третьего одноразрядного регистра, выход которого соединен с входом регистра частного, содержит второй сумматор по модулю два, и четвертый одноразрядный регистр, причем выход регистра делимого подключен к первому входу второго сумматора по модулю два, второй вход которого соединен с инверсным выходом триггера управления, D-вход которого соединен с выходом четвертого одноразрядного регистра, вход которого соединен с вторым информационным входом,второго элемента И-ИЛИ и с выходом второго сумматора по модулю два, третий вход которого соединен с выходом переноса одноразрядного сумматора, управляюшие входы второго элемента И-ИЛИ соединены с второй тактовой шиной устройства.

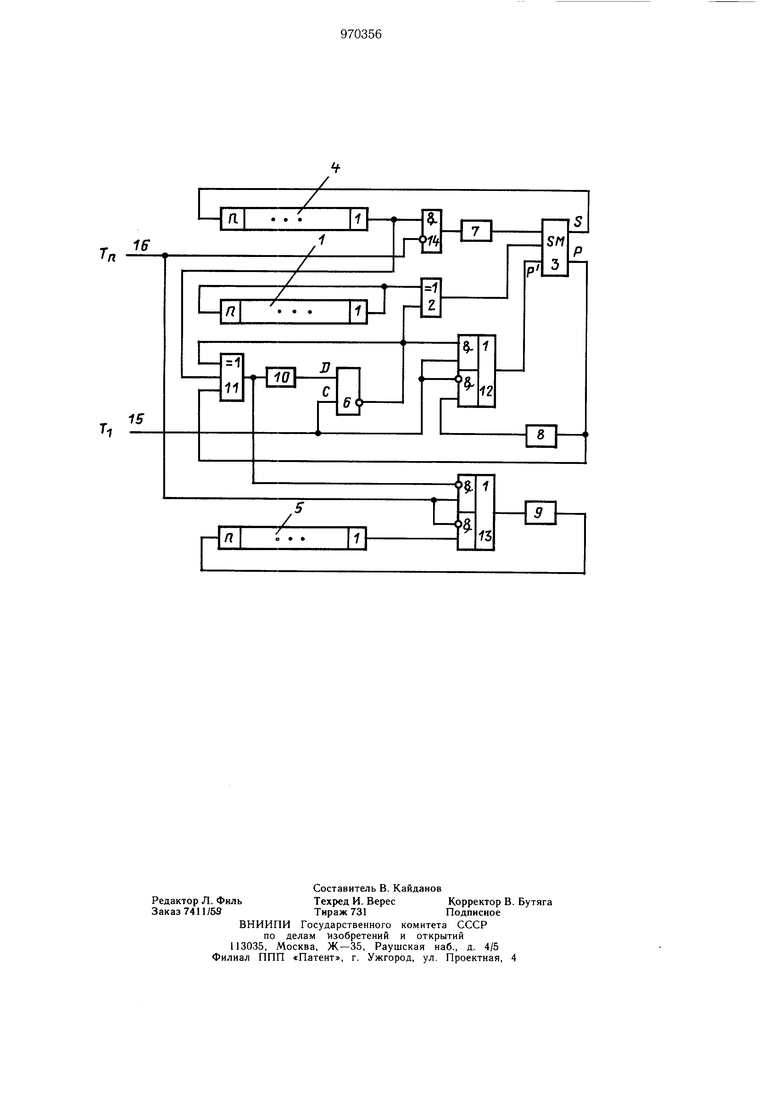

На чертеже приведена функциональная схема устройства.

Устройство содержит п-разрядный (п - разрядность мантиссы) регистр 1 делителя, вход и выход которого объединены и через сумматор 2 по модулю два соединены с входом одноразрядного сумматора 3, п-разрядные регистры делимого 4 и частного 5, СДтриггер 6 управления, первый 7, второй 8, третий 9 и четвертый 10 одноразрядные регистры, второй сумматор 11 по модулю два, первый 12, второй 13 элементы И-ИЛИ и элемент И 14. Вход регистра 5 соединен со своим выходом через последовательно соединенные регистр 9, второй инверсный вход которого соединен с выходом второго сумматора по модулю два и входом четвертого одноразрядного регистра 10, выход которого подключен к D-входу триггера 6, инверсный выход которого связан с вторым входом второго сумматора 11 по модулю два, вторым входом первого сумматора 2 по модулю два и вторым входом первого элемента И-ИЛИ 12, выход которого соединен с входом переноса одноразрядного сумматора 3, выход суммы которого подключен к входу регистра 4, выход которого соединен с первым входом сумматора 11 и через последовательно соединенные элемент И 14 и первый одноразрядный регистр 7 подключен к входу сумматора 3, выход переноса которого связан с третьим входом сумматора 11 и с входом второго одноразрядного регистра 8, выход которого подключен к первому входу первого элемента И-ИЛИ 12. С-вход триггера 6 и управляющие первого элемента И-ИЛИ 12 связаны с первой тактовой шиной 15, инверсный вход элемента И 14 и управляюшие второго элемента И-ИЛИ 13 соединены с второй тактовой шиной 16.

Устройство позволяет вычислять п+1 разрядов мантиссы частного (без знака). В исходном состоянии в регистре 4 записан прямой код делимого, в регистре 1 - прямой код делителя. Триггер 6 находится в Нулевом состоянии.

Деление осуществляется за п+1 цикл. При этом в первых п циклах определяются п старших разрядов частного, в п+ 1-м цикле определяется младшая цифра частного, используемая для-округления. Цикл работы схемы устройства соответствует разрядности операндов и равен п тактов. В основу алгоритма деления положен метод деления без восстановления остатка.

Рассмотрим работу устройства в i-м цикле деления. В начале каждого i-ro цикла (такт II) в регистре 4 находится i-1-й остаток, в i-2-x .младших разрядах регистра 5 находятся i-2 старших цифр частного, в одноразрядном регистре 9 находится n-i + + 2 я цифра частного. На триггер 6 записан знак i-1-го остатка и сохраняется в течение всего i-ro цикла.

Формирование i-ro остатка осуществляется следуюш,им образом. В зависимости от знака предыдущего i-1-го остатка на один из входов сумматора 3 подается прямой или дополнительный код делителя. При единичном состоянии триггера 6 через сумматор 2 по модулю два будет выдан прямой код делителя, при нулевом - обратный код. Дополнительный код делителя формируется подачей на вход переноса сумматора 3 через элемент И-ИЛИ 12 единицы младшего разряда в такте II. Сдвинутый по отношению к делителю на один разряд влево i-1-й остаток нодается на второй вход сумматора. Такое подключение регистра 1 к сумматору 3, а также коммутация цепей циркуляции регистра 4 через одноразрядный динамический регистр 7 и сумматор 3 обеспечивает совмещение в одном цикле микрооперации сдвига влево i-1-го остатка, преобразование в дополнительный код делителя и суммирование их с записью результата, т. е. i-ro остатка, в регистр 4. В такте Т выдача кода из регистра 4 блокируется элементом И 14. Знак i-ro остатка формируется как сумма по модулю два переноса из п-го разряда при определении i-ro остатка, обратного кода знака i-1-го остатка З., и значения п-го разряда i-1-го остатка , который в п-м такте i-ro цикла будет находиться на выходе первого разряда регистра 4. Таким образом, логическое выражение для определения знака i-ro остатка будет иметь вид: + 3%- + Знак i-ro остатка формируется сумматором 11 по модулю два и записывается в такте Т следующего (i + 1)-го цикла на триггер 6. Задержка записей знака на один такт осуществляется одноразрядным динамическим регистром 10. Знак i-ro остатка определяется n-i+1-й цифрой частного. Запись n-i + 1-й цифры частного в одноразрядном регистре 9 осуществляется в такте Тп с выхода сумматора 11 через инверсный вход элемента И- ИЛИ 13. Коммутация цепей циркуляции регистра 5 через дополнительный одноразрядный регистр 9 обеспечивает сдвиг кода частного в каждом цикле на один разряд влево. Таким образом, после выполнения i-ro цикла в регистре 4 будет находиться i-й остаток, Б одноразрядном регистре 10 - знак i-ro остатка, в регистре 9 - п-i + + 1-Я цифра частного. После выполнения п+ 1-го цикла в регистре 5 находится п-я цифра частного, на инверсном выходе триггера б или в регистре 9 будет сформирована младшая дополнительная цифра частного, которая используется для округления результата. Округление результата можно производить на сумматоре 3 за один цикл, который можно совмещать с циклом выдачи. Знак результата можно формировать с помощью Т-триггера в цикле приема операндов. Известное устройство и предлагаемое содержит равное количество логических элементов И и ИЛИ, сумматор по модулю два. В устройстве-прототипе используется три динамических регистра с разрядностью п+1, в предлагаемом - три динамических регистра с разрядностью п. Таким образом, выигрыщ в оборудовании по сравнению с устройством-прототипом составляет величину 3LP, где LP - сложность одного разряда динамического регистра. Деление в устройстве-прототипе осуществляется за (п+1). тактов. В предлагаемом устройстве частное формируется за п(п+ 1 ) тактов. Таким образом, время выполнения операции деления в предлагаемом устройстве уменьщается на один цикл. Формула изобретения Устройство для деления чисел, содержащее регистры делителя, делимого и частного, первый сумматор по модулю дра, одноразрядный сумматор, элемент И, одноразрядные регистры, элементы И-ИЛИ и триггер управления, причем вход и выход регистра делителя объединены и подключены к первому входу первого сумматора по модулю два, выход которого подключен к первому входу одноразрядного сумматора, выход суммы которого соединен с входом регистра делимого, выход которого соединен с первым входом элемента И, выход которого подключен к входу первого одноразрядного регистра, выход которого подключен к второму входу одноразрядного сумматора, выход переноса которого подключен к входу второго одноразрядного регистра, выход которого соединен с первым информационным входом первого элемента И-ИЛИ, выход которого подключен к третьему входу одноразрядного сумматора, второй вход первого сумматора по модулю два и второй информационный вход первого элемента И-ИЛИ соединены с инверсным выходом триггера управления, С-вход которого соединен с управляющими входами первого элемента И-ИЛИ и с первой тактовой щиной устройства, второй вход элемента И соединен с второй тактовой щиной устройства, выход регистра частного соединен с первым информационным входом второго элемента И-ИЛИ, выход которого соединен с входом третьего одноразрядного регистра, выход которого соединен с входом регистра частного, отличающееся тем, что, с целью увеличения быстродействия и сокращения аппаратурных затрат, оно содержит второй сумматор по модулю два и четвертый одноразрядный регистр, причем выход регистра делимого подключен к первому входу второго сумматора по модулю два, второй вход которого соединен с инверсным выходом триггера управления, D-вход которого соединен с выходом четвертого одноразрядного регистра, вход которого соединен с вторым информационным входом второго элемента И-ИЛИ и с выходом второго сумматора по модулю два, третий вход которого соединен с выходом переноса одноразрядного сумматора, управляющие входы второго элемента И-ИЛИ соединены с второй тактовой щиной устройства. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3816733, кл. 235-164, 1975. 2.Авторское свидетельство № СССР по заявке № 2942869/24, кл. G 06 F 7/54, 1980 (прототип). HII

Авторы

Даты

1982-10-30—Публикация

1981-04-20—Подача