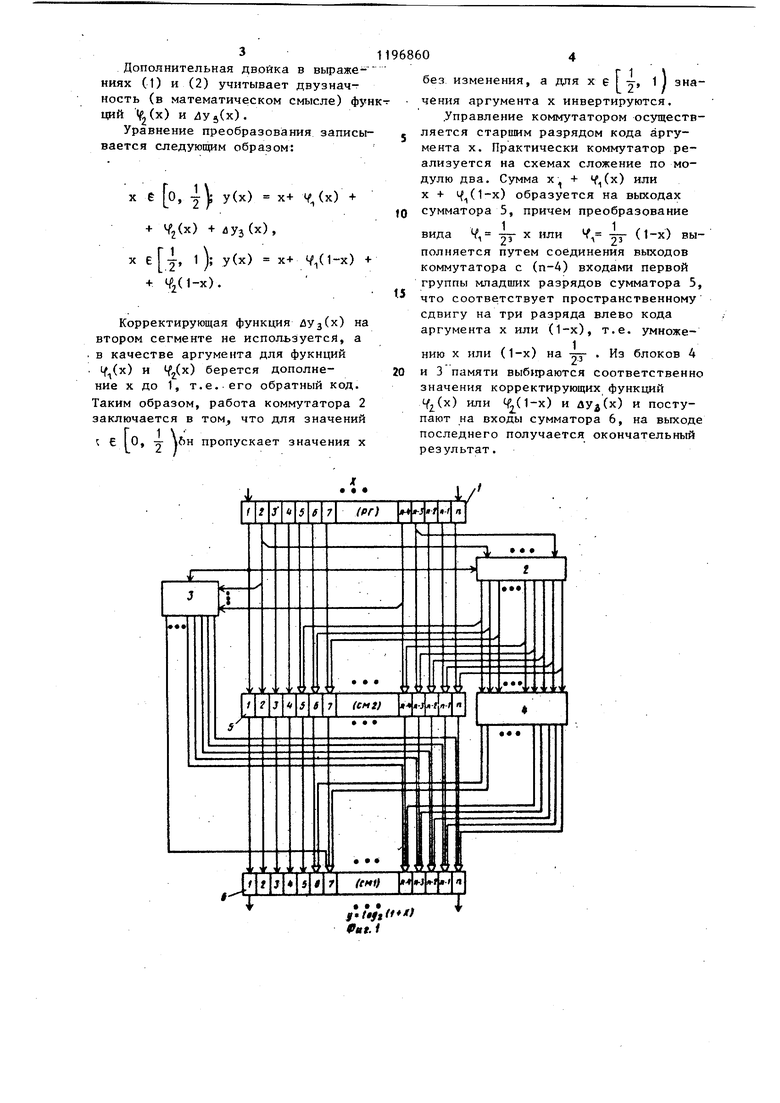

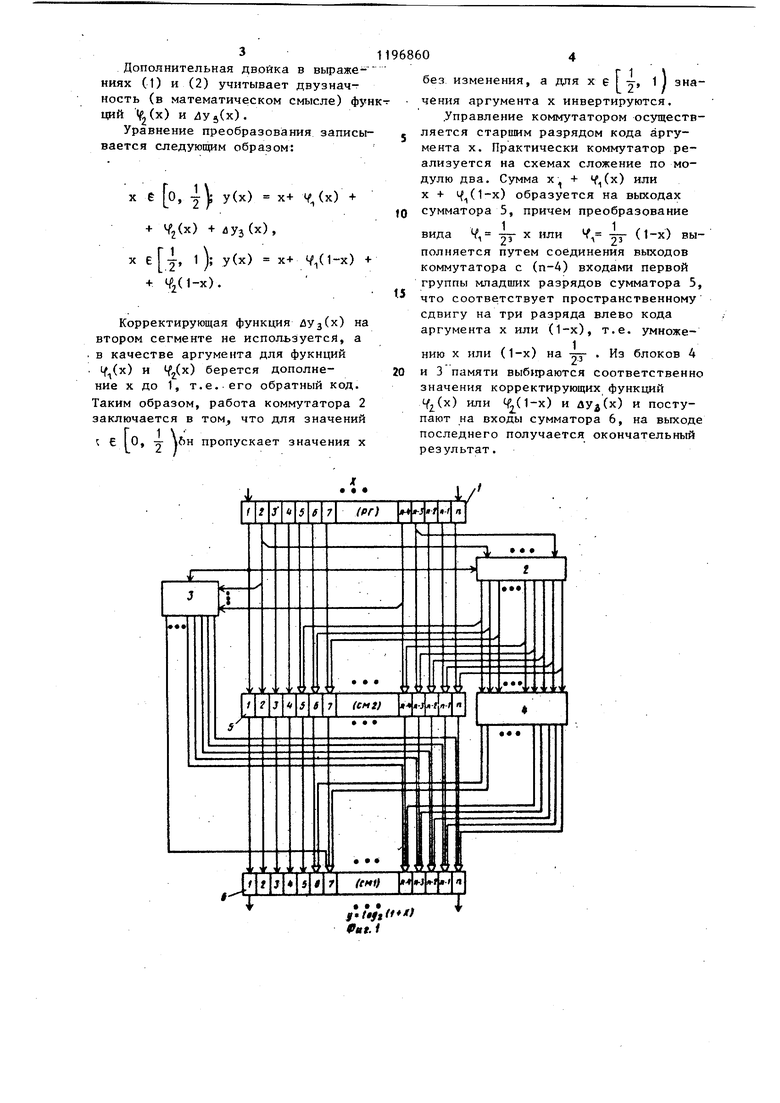

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении спе1щализированных вычислителей, гибридны функциональных преобразователей, и(ифровьгх фильтров и информационноизмерительных систем. Цель изобретения - уменьшение объема памяти. На фиг. 1 приведена структурная схема логарифмического преобразователя, на фиг. 2 - эпюры, поясняющие принцип преобразования. Логарифмический преобразователь содержит регистр 1, коммутатор 2, второй 3 и первьй 4 блоки памяти, второй 5 и первый 6 сумматоры. Работа преобразователя основана на кусочно-линейной аппроксимации логарифмической функции у log (1+ X 6fO,lJ, с последующей коррекцией разности между исходной функцией и ее линейным приближением, называемо функцией коррекции. Аппроксимация функции у log.2(1+x), X е 0,1 показана (фиг.2а) прямой линией, следователь но входной код X содержит часть информации о выходной величине у и Может использоваться как грубое приближение исходной функции. Разность ,y исходной функцией и ее линейным приближением лу (х) log 2()-х показана на фиг.26. . Строят функцию (х), аппроксимирую щую/iy(k) таким образом, что . Л f,M . J JT (1-х), Т.е. (f (х) - симметрична относительно оси, проведенной через точку V(x) на интерваX -J. Вычисление o.I). умножение кода ар1гумента х на коэффициент соответ

ствует операции сдвига на три разряда влево и не представляет трудностей при практической реализации, а

-1. J

вычисление f(x) на интервале

может вьтолняться аналогично, если в качестве аргумента брать дополнительно X до 1, т.е. обратный код X, что возможно вследствие симметрии функции V,(x).

Таким образом, объемы блоков памяти, необходимых для запоминания корректирующих функций f,j(x) и . . dVj(х), равны

Q, (l(fiM (п-5) .,. С«-Ч. )

(а-5).2

n-t Q, Q ЛУз(х) (п-6) 2

2

(2)1

/ г, Л- К

(п-6) 2 Разность между функциями (фиг.2 ) 4У(х) и 1((х) равна ) ду (х) - t(x). Строят функцию у,, которая являет ся симметричным отображением ду(х) для значений хе I , 1 1 относительно оси, проведенной через точку х (фиг.2в). Значения функции ) рассчитываются заранее и помещаются в первый блок памяти. Очевидно, что, как и ля функции (х), если при переходе через X у брать дополнительные аргументы до 1, то %(х) совпадает с функцией у (х) на сегменте -j, 1 1 вследствие построенной симметрии. Показана также функция разности (фиг.2г) йУз(х) uyj,(x) (x), , значения которой запоминаются во втором блоке памяти и служат для получения точного результата преобра о. Л зования для значений х 6 Записывают уравнения для аппроксимирующих и корректирующих функций ду(х) 1ор2(1+х)-х, хе 0,1), «D o. т X 4yV(x)- ,м, &У- (х) .), - ), 4) ЛУ2(1-х), ayj(x) 4у(х) - ), Анализ функций 1.(х) и у казывает. 2м«кс

31

Дополнительная двойка в вьфаже- ниях (1) и (2) учитывает двузначность (в математическом смысле) функ ций 2(х) и /зуз(х).

Уравнение преобразования записывается следующим образом:

X е о, -1 у(х) х+ V(x) + + Чг(х) + йУз (х),

X , 1 ); у(х) х-ь (1-х) + 4i,(1-x).

Корректирующая функция дуз(х) на втором сегменте не используется, а . в качестве аргумента для фукнций ((х) и ) берется дополнение X до 1, т.е. его обратный код. Таким образом, работа коммутатора 2 заключается в том, что для значений

Т г пропускает значения х

968604

без изменения, а дпя х е j, 1 ) зна. чения аргумента х инвертируются.

.Управление коммутатором осуществJ ляется старшим разрядом кода аргумента X. Практически коммутатор реализуется на схемах сложение по модулю два. Сумма х;, + V,(x) или X + 4i() образуется на выходах сумматора 5, причем преобразование

fO

1

V 4т (1-х)

вида V, yj- X или тд- выполняется путем соединения выходов коммутатора с (п-4) входами первой группы младших разрядов сумматора 5, что соответствует пространственному сдвигу на три разряда влево кода аргумента х или (1-х), т.е. умножению X или (1-х) на . Из блоков 4 и 3 памяти выб1фаются соответственно значения корректирующих функций 4fi(x) или if,(-x) и и поступают на входы сумматора 6, на выходе последнего получается окончательный результат.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический преобразователь | 1986 |

|

SU1401457A1 |

| Логарифмический преобразователь | 1985 |

|

SU1269126A1 |

| Логарифмический преобразователь | 1981 |

|

SU959073A1 |

| Устройство для вычисления функции двоичной экспоненты | 1985 |

|

SU1305675A1 |

| Цифровой логарифмический преобразователь | 1987 |

|

SU1425665A1 |

| Устройство для потенцирования | 1986 |

|

SU1348833A1 |

| Функциональный преобразователь | 1986 |

|

SU1397905A1 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Устройство для вычисления функций | 1984 |

|

SU1206767A1 |

| Устройство для вычисления функции двоичной экспоненты | 1984 |

|

SU1238066A1 |

ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий регистр, первый и второй блоки памяти, коммутатор и первый сумматор, выходы которого являются выходами логарифмического преобразователя, (п-5), входов первой группы младших разрядов первого сумматора (где п - разрядность регистра и сумматоров) соединены с выходами первого блока памяти, ад.ресные входы которого подключены к выходам коммутатора, управляющий вход которого соединен с управляющим входом управления чтением второго, блока памяти и выходом первого старшего разряда регистра, входы которого являются входами логарифмического преобразователя, (п-4) выхода старших разрядов регистра, начиная с второго, подключены к входам коммутатора (п-5) выходов старших разрядов регистра, начиная с второго, подключены к адресным входам второго блока памяти, вькоды которого соединены с (п-6) входами второй группы младших разрядов первого сумматора, отличающийся тем, что, с целью уменьшения объема (Л памяти, в него введен второй сумматор, (п-4) входа первой группы младших разрядов которого подключены к выходам коммутатора, входы второй группы второго сумматора подключены к выходам регистра, выходы второго сумматора соединены с входами третьей группы первого сумматора, ;о Од 00 Од

| Цифровой логарифмический преобразователь | 1979 |

|

SU881741A1 |

| Логарифмический преобразователь | 1981 |

|

SU959073A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-21—Подача