tsD

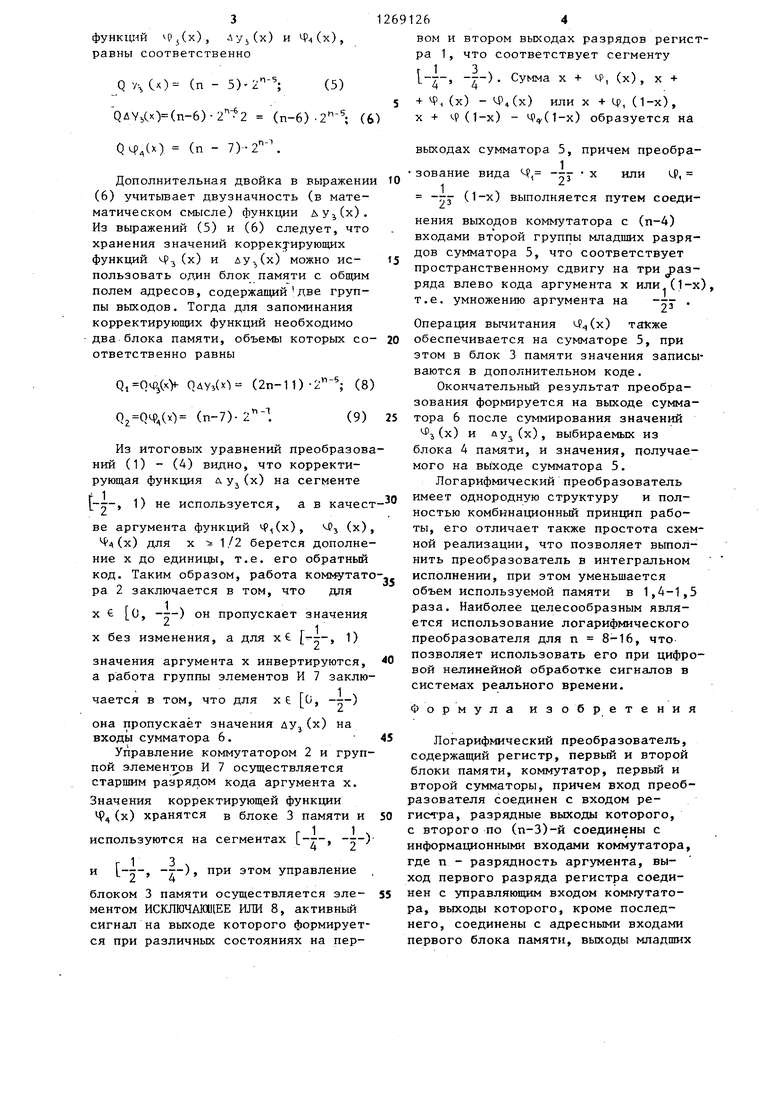

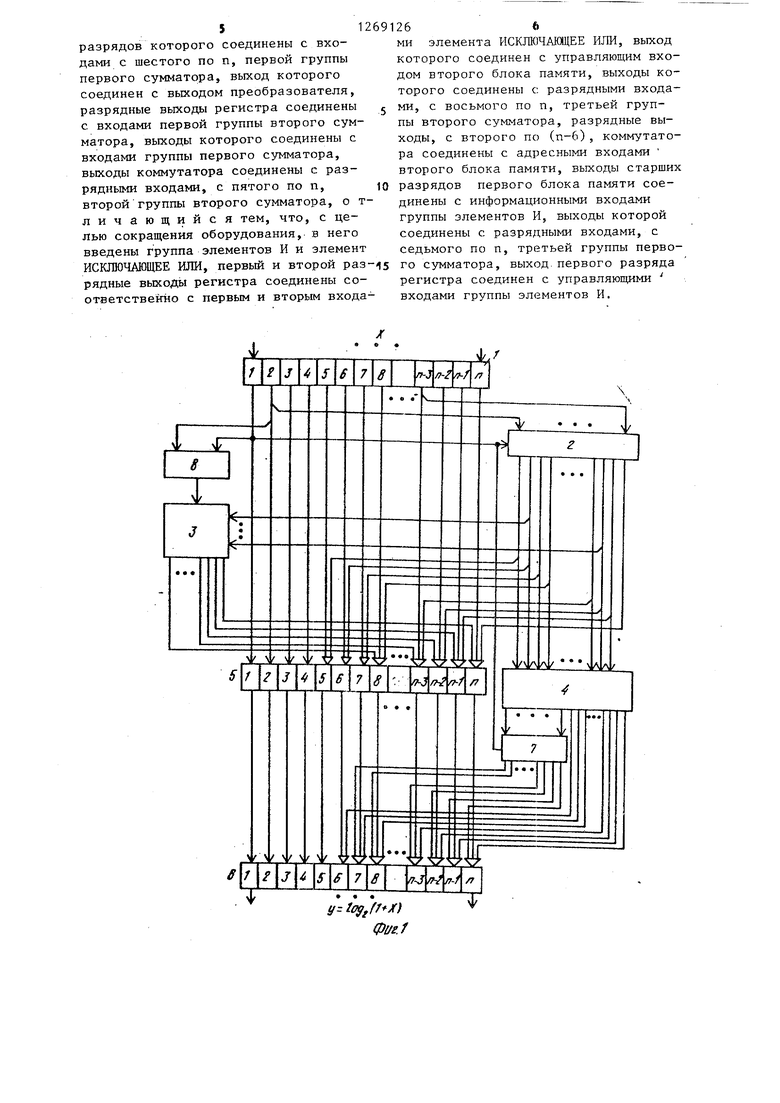

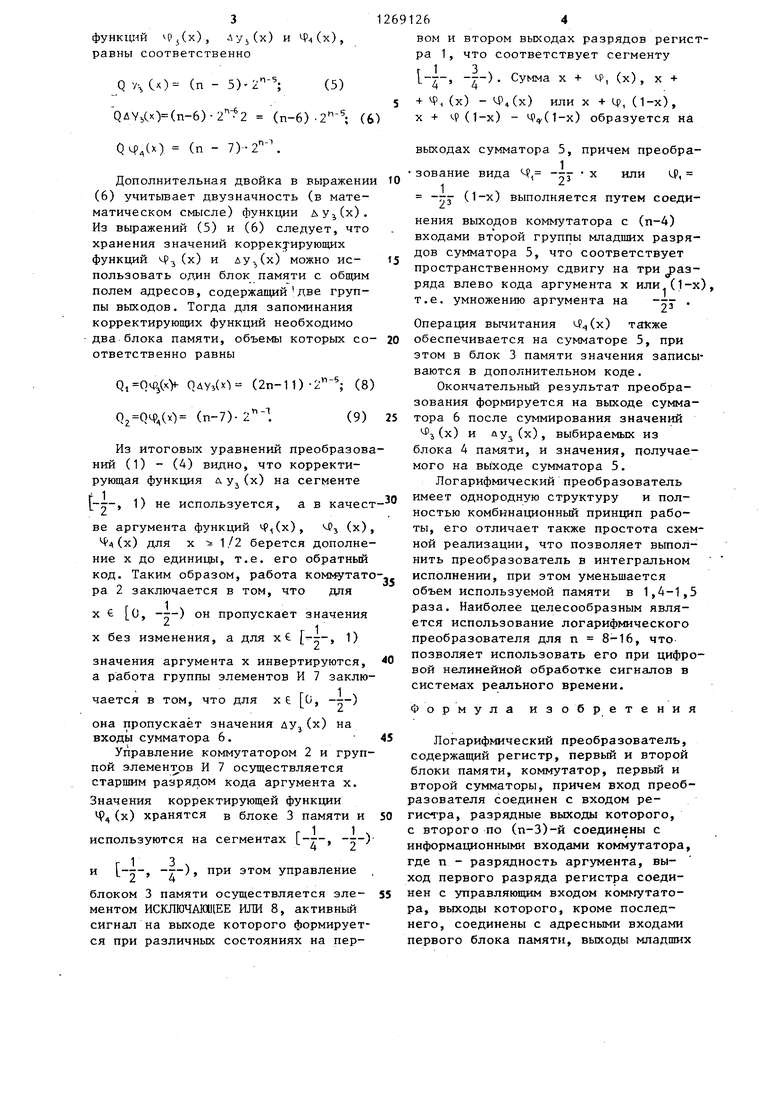

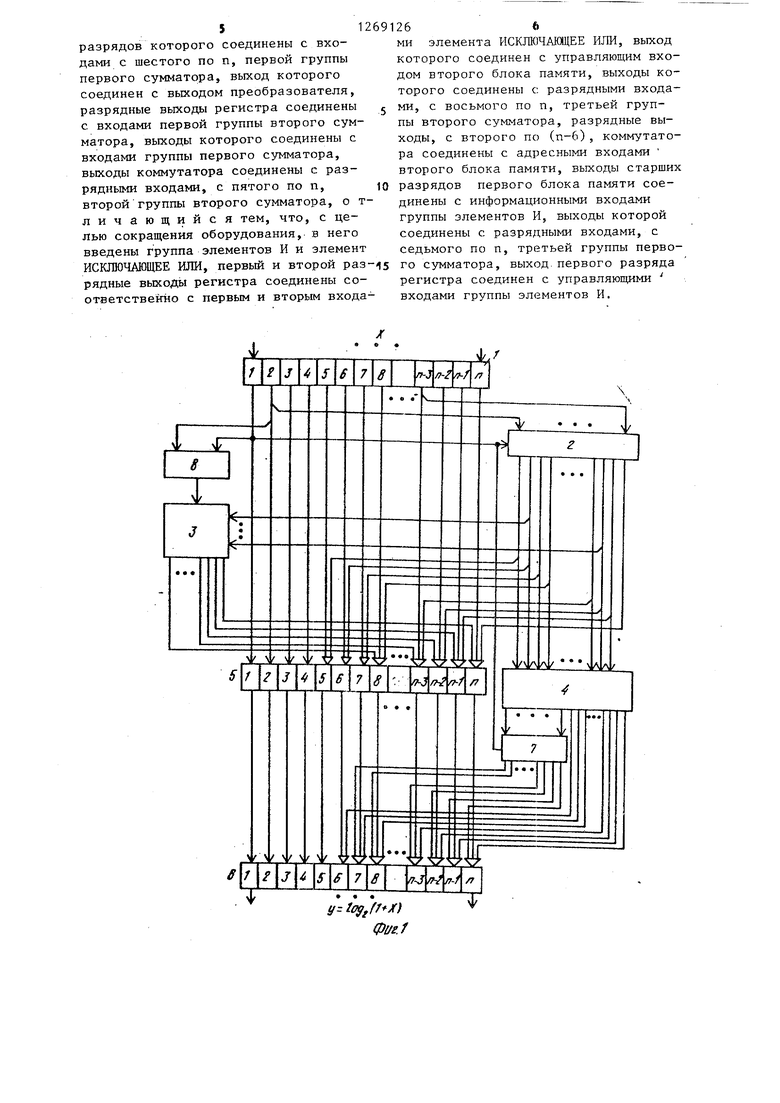

о Изобретение относится к цифровой вычислительной технике и может быть использовано при построении цифровых устройств для обработки сигнало информационно-измерительных систем специализированных вычислителей и гибридных функциональных преобразов телей. Цель изобретения - сокращение об рудования. На фиг. 1; приведена структурная схема логарис)мического преобразователя; на фиг. 2 - эпюры, поясняющие принцип преобразования. , Логарифмический преобразователь содержит регистр 1, коммутатор 2, второй 3 и первый 4 блоки памяти, второй и первьш сумматоры 5 и 6, группу элементов И 7, элемент ИСКЛЮ ЧАЮЩЕЕ ИЛИ 8. Работа преобразователя основана на кусочно-линейной аппроксимации функции (1+х), ,1). Из графика воспроизводимой функции у(х) и аппроксимирующей прямой линии (фиг. 2а) видно, что код х содержит часть информации о величине у и является грубьм приближением исходной функции. Разность между функцией (1+х) и ее линейным приближением 4у(х)1ор, (1+х)-х (фиг, 25). Построим функцию (х) следующим образом: I хб о, ---) 2 М,(х) -i -d-x), , 1 Из фиг. 7.6 следует, чтофДх) симметрична относительно оси, пров денной через точку х 1/2. Таким образом, определение р, (х) на инт сегмент х О,) : у(х) х сегмент х ---, -2-) :у(х) х О сегмент х е ---, ):у(х) х О -1 сегмент х€ , --) :у(х) х Значения функций vp (х), vp . (х) и лу, (х) запоминаются в блоках па- 55 мяти и служат для получения точного результата преобразования, выступая в роли корректирующих функций, Ана+ Ф, (х) + ,,{уС) + 4у(х); (1) + ф(х) - ) + (х) + дУз (х); (2) ),- 4(1-х) + Ц)(1-х); (3) + Ц),(1-х) + .о(1-х).(4) 26 вале Со, ---) сводится к операции сдвига на три разряда влево, а определение Ц), (х) на интервале ,1) может выполняться аналогично, если в качестве аргумента брать дополнение X до 1, что возможно ввиду симметрии функции ф (х). На фиг. 2Ь показана пунктиром разность меж,цу функциями ду, (х) и ЧДх), т.е. л у 2, ду, (х) - Ф (х) . Построим функцию vp (х), которая будет симметричным отображением ду(х) для xt п , 1) относительно построенной оси (фиг. 2 Ь ). Вследствие построенной симметрии при переходе черех X - 1/2 в качестве аргумента (х) следует брать дополнение х до 1, тогда Ф(х) будет совпадать с Лу(х) на сегменте , 1), а на сегменте i(, 7) дУ2(х) определяется (фиг. 2 ) как Ц),(х) и , (х) . Построим функцию vpj(x), , -) таким образом (фиг. 23), чтобы %(х), ,х,) 3(Х) .-9) HaUJ Ч макс, : где х - значение аргумента х, при котором функция Ч2(х) принимает максимальное значение P2.мaкc Нафиг.2е показана функция разности ФДх) Цъ(х) -ФгСх), хер-, ), 4 2 которую необходимо учитывать при определении -Р2.Сх) через Фз (х) ;11 на сегменте -7-, -j-}- Тогда итоговые уравненш преобразований можно записать следукяцим образом: лиз корректирующих функций показывает, что Ф (х)„д, ду(х) 2.; (х), Таким образом, объемы блоков памяти, необходимых для запоминания

функгц й .р.((х), Ду,,(х) и Фц (х), равны соответственно

Q У, СО (п - 5)(5)

рдУ,Ск)(п-6) (п-6).

ОЧ)(х) (п - 7)-2 Дополнительная двойка в выражении (6) учитывает двузначность (в математическом смысле) функции ). Из выражений (5) и (6) следует, что хранения значений корректирующих функций (х) и ) можно использовать один блок памяти с общим полем адресов, содержащий две группы выходов. Тогда для запоминания корректирующих функций необходимо два блока памяти, объемы которых соответственно равны ( Оду,(х1 (2п-11)-2 (8) ,(v;) (п-7) (9) Из итоговых уравнений преобразова ний (1) - (4) видно, что корректирующая функция л у(х) на сегменте -г, 1) не используется, а в качест ве аргумента функций Ч(х), (х) Ч4 (х) для X 1 /2 берется дополнение X до единицы, т.е. его обратный код. Таким образом, работа коммутато ра 2 заключается в том, что для X € , 9 ° пропускает значения 1 X без изменения, а для х€ о значения аргумента х инвертируются, а работа группы элементов И 7 заключается в том, что для х о, -5) она пропускает значения ду(х) на входы сумматора 6. Управление коммутатором 2 и группой элементов И 7 осуществляется старшим разрядом кода аргумента х. Значения корректирующей функции Ц (х) хранятся в блоке 3 памяти и Г 1 1 используются на сегментах ) г Г 3 . и Р этом управление блоком 3 памяти осуществляется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 8, активный сигнал на выходе которого формируется при различных состояниях на первом и втором выходах разрядов регистра 1, что соответствует сегменту

1

, --} . Сумма X + М, (х), X +

+ 45, (х) - Ч),(х) или X + Ц), (1-х), X + (1-х) - Ц(1-х) образуется на

выходах сумматора 5, причем преобразование вида X или -г (1-х) выполняется путем соединения выходов коммутатора с (п-4) входами второй группы младщих разрядов сумматора 5, что соответствует пространственному сдвигу на три разряда влево кода аргумента х или (1-х), т.е. умножению аргумента на --j . Операция вычитания U(x) также обеспечивается на сумматоре 5, при этом в блок 3 памяти значения записываются в дополнительном коде. Окончательный результат преобразования формируется на выходе сумматора 6 после суммирования значений (х) и ay.j(x), выбираемых из блока 4 памяти, и значения, получаемого на выходе сумматора 5. Логарифмический преобразователь имеет однородную структуру и полностью комбинационный принцип работы, его отличает также простота схемной реализации, что позволяет вьтолнить преобразователь в интегральном исполнении, при этом уменьшается объем используемой памяти в 1,4-1,5 раза. Наиболее целесообразным является использование логарифмического преобразователя для п 8-16, что позволяет использовать его при цифровой нелинейной обработке сигналов в системах реального времени. Формула изобретения Логарифмический преобразователь, содержащий регистр, первый и второй блоки памяти, коммутатор, первый и второй сумматоры, причем вход преобазователя соединен с входом реистра, разрядные выходы которого, второго по (п-З)-й соединены с нформационными входами коьмутатора, де п - разрядность аргумента, выод первого разряда регистра соедиен с управляющим входом коммутатоа, выходы которого, кроме последего, соединены с адресными входами ервого блока памяти, выходы младщих

512

разрядов которого соединены с входами с шестого по п, первой группы первого сумматора, выход которого соединен с выходом преобразователя, разрядные вьпсоды регистра соединены с входами первой группы второго сумматора, выходы которого соединены с входами группы первого сумматора, выходы коммутатора соединены с разрядными входами, с пятого по п, второй группы второго сумматора, о тличающийся тем, что, с целью сокращения оборудования, в него введены группа элементов И и элемент ИСКПЮЧАЩЕЕ ИЖ, первый и второй разрядные выходы регистра соединены соответственно с первым и вторым входаЖ

266

ми элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с управляющим входом второго блока памяти, выходы которого соединены с разрядными входами, с восьмого по п, третьей группы второго сумматора, разрядные выходы, с второго по (п-6), коммутатора соединены с адресными входами второго блока памяти, вьпсоды старших разрядов первого блока памяти соединены с информационными входами группы элементов И, выходы которой соединены с разрядными входами, с седьмого по п, третьей группы первого сумматора, выход.первого разряда регистра соединен с управляюпщми входами группы элементов И. ТТ7 у toSffr Jf) ф1/г.1

У(Х1

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический преобразователь | 1984 |

|

SU1196860A1 |

| Логарифмический преобразователь | 1981 |

|

SU959073A1 |

| Устройство для потенцирования | 1986 |

|

SU1348833A1 |

| Логарифмический преобразователь | 1986 |

|

SU1401457A1 |

| Устройство для вычисления функции двоичной экспоненты | 1985 |

|

SU1305675A1 |

| Квадратор | 1986 |

|

SU1405053A1 |

| Устройство для вычисления функции двоичной экспоненты | 1984 |

|

SU1238066A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Квадратор | 1986 |

|

SU1325469A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных вычислителей, информационно-измерительных систем,: гибридных функциональных преобразователей и цифровых устройств для обработки сигналов в реальном времени. Цель изобретения- сокращение оборудования. В cocTdb преобразователя входят регистр, коммутатор, два блока памяти, два сумматора, группа элементов И и элемент ИСКЛЮЧАЩЕЕ ИЛИ. Уменьшение объема памяти достигается за счет использования кусочнолинейной функции коррекции, аппроксимирующей разность между исходной функцией и ее линейным приближением, а также за счет использования симметрии функции коррекции, устранения двузначности функции коррекции и введения третьего канала коррекции. Преобразователь целесообразно использовать для логарифмического пре« i образования 8-16-разрядных чисел при восстановлении и сжатии сигна(Л лов, при цифровой нелинейной обработке звуковых и видеосигналов в устройс ствах реального времени, а также для повышения производительности микропроцессорных систем. 2 нл.

Фиг.2

| Логарифмический преобразователь | 1981 |

|

SU959073A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Логарифмический преобразователь | 1984 |

|

SU1196860A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1985-03-19—Подача