(54) ЦИФРОВОЙ ФАЗОМЕТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1988 |

|

SU1626186A2 |

| Цифровой фазометр | 1980 |

|

SU932423A1 |

| Устройство для измерения угла фазового сдвига гармонических сигналов | 1990 |

|

SU1765781A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Следящий фазометр | 1986 |

|

SU1318927A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| Скважинный инклинометр | 1990 |

|

SU1721225A1 |

I

Изобретение относится к технике измерения электрических величин, в частности к фазовым измерениям и может быть использовано для измерения фазового сдвига между двумя периодическими сигналами с фиксированной частото

Известен цифровой фазометр, содержащий преобразователь фазового сдвига между двумя входными сигналами в длительность импульса, генерато высокой частоты, счетчик с индикацией, элемент И, триггер пуска, блок выделения спада сигнала преобразователя фазового сдвига, два пересчетных блока, один из которых подсоединен ко входу счетчика, а второй - ко входу триггера пуска fll.

Однако погрешность измерения такого фазометра в области нулевых разностей фаз высокая из-за усреднения перескока О -360 .

Известен также цифровой, фазометр, содержащий исследуемый и опорный датчики прямоугольных напряжений, преобразователь фаза-код, устройство анализа кодов, три элемента И, элемент ИЛИ вычислитель, делитель периода опорного сигнала, подключенный входом к опорному датчику прямоугольных напряжений и одновременно ко входу преобразователя фаза-число импульсов, входящего в преобразователь фаза-код, вьпсод которого соединен с одним из входов первого элемента И и через

0 счетчик с устройством анализа кодов, выход которого разведен на два входа первого элемента И, а третий его вход соединен с одним из выходов делителя периода опорного сигнала, при

5 этом другой его выход подключен ко второму входу второго элемента И, третий элемент И соединен одним входом с генератором импульсов эталонной частоты преобразователя фаза-код а другим - с выходом первого элемента И, при этом второй и третий элементы И через элемент ИШ подключены к вычислителю. Данное устройство производит коррекцию результатов вычисления разностей фаз 2.

Однако устройство обладает невысоким быстродействием и недостаточной точностью измерения. Цель изобретения

повьшение быстродействия наряду обеспечением высокой точности.

Поставленная цель достигается тем, что в цифровой фазометр, содержащий преобразователь фаза-код, датчики прямоугольных напряжений, выходы которых соединены со входами преобразователя фаза-код, и блок усреднения, введен блок вычисления целой части разности фаз, причем п выходов преобразователя фаза-код подключены к соответствующим п входам блока усреднения и к п входам блока вычисления целой части разности фаз, выход которой соединен с п + 1 - м входом блока усреднения.

При этом блок вычисления целой части разности фаз состоит из п-разрядного параллельного регистра памяти, п - разрядного параллельного сумматора и одноразрядного сумматора, первый вход которого подключен к прямому выходу п-го разряда регистра памяти, второй и третий входы - к выходам п-го разряда и переноса п-разрядного сумматора, один из п входов которого подключен к соответствующим п-инверсным выходам регистра памяти, другие п выходов соединены с соответствующими п входами регистра памяти и являются входами блока вычисления целой части разности фа а выход одноразрядного сумматора его выходом.

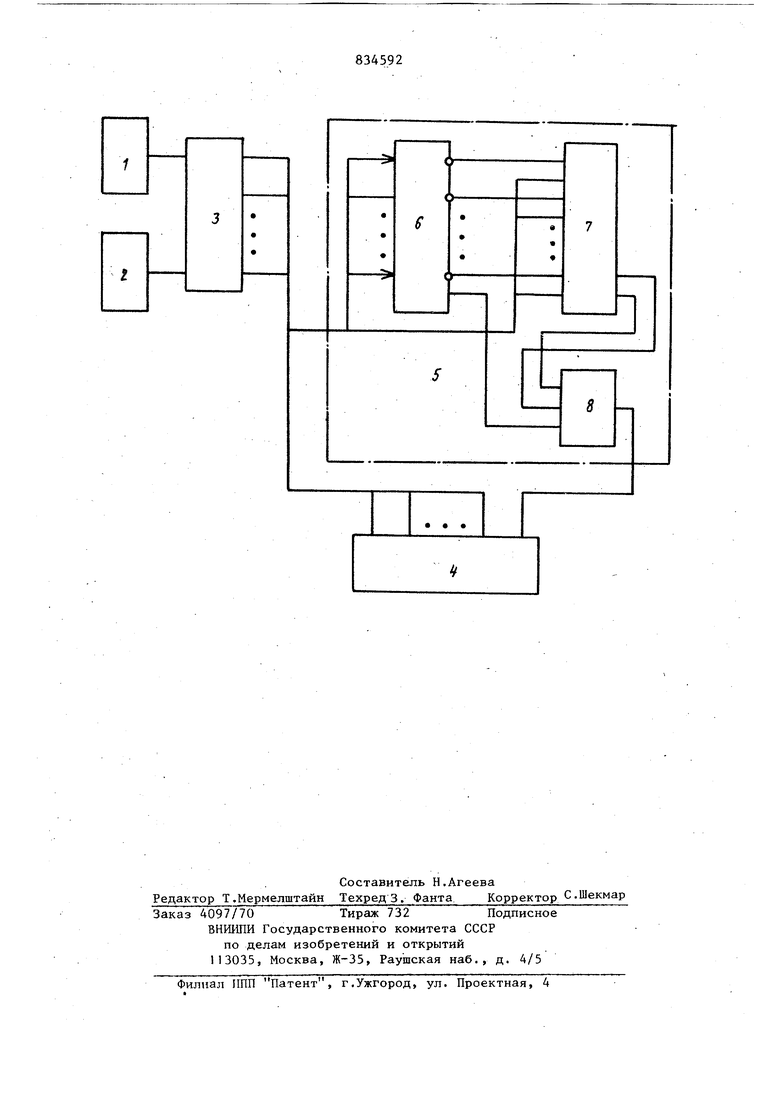

На чертеже представлена блок-схема предлагаемого устройства.

Устройство состоит из датчиков 1 и 2 прямоугольных напряжений, преобразователя 3 фаза-код, блока 4 усреднения, блока 5 вычисления целой части разности фаз, состоящего из napajv nejtemtfo п-раз рядного регистра 6 памяти, параллельного п-разрядного сумматора 7 и одноразрядного сумматора 8 Выходы датчиков 1 и 2 прямоугольных напряжений соединены со входами преобразователя 3 фаза-код, п выходов которого соединены с соответствующими П выходами блока 5 вычисления целой части разности фаз, и с п входами блока 4 усреднения, п + 1 - и вход которого подключен к выходу блока 5 вь числения целой части разности

фаз, причем первый вход одноразрядного сумматора 8 подключен к прямом выходу п -го разряда регистра 6 памяти, второй и третий входы - к выходам п -го разряда и переноса п разрядного сумматора 7. Одни из п входов п -разрядного сумматора 7 подключены к соответствующим п -инверсным выходам регистра 6 памяти, другие п входов соединены с соответствующими п входами зтого регистра и являются входами блока 5 вычисления целой части разности фаз, а выход одноразрядного сумматора 8 его выходом.

Устройство работает следзшщим образом.

С датчиков 1 и 2 прямоугольных напряжений сигналы поступают на входы преобразователя 3 фаза-код, где разность фаз преобразуется во временной интервал, который заполняется импульсами генератора квантующей частоты. Количество импульсов подсчитывается счетчиком и в виде двоичного параллельного кода поступает на выход преобразователя 3 фаза-код. Таким образом измеряется дробная част разности фаз.

С выхода преобразователя 3 фазакод кодь, соответствующие измеренным разностям фаз, поступают на входы блока 4 усреднения и входы блока 5 вычисления целой части разности фаз. В зависимости от значений кодов; соответствующих первому и последующим измерениям, с выхода блока 5 вычисления целой части разности фаз на вход п+1-го разряда блоки 4 усреднения поступает сигнал либо логического нуля, либо единицы. Логическая единица соответствует прибавлению к измеренному значению разности фаз 360. Это необходимо для выравнивания перескока 0-360 при усреднении значений разностей фаз.

В блоке 4 усреднения последовательно складываются N откорректированных значений разностей фаз.

В блоке 5 вычисления целой части разности фаз двоичный арифметический п-разрядный параллельный код, соответствукнций первой измеренной преобразователем 3 фаза-код разности фаз, поступает на соответствующие п выходов параллельного регистра 6 памяти, запоминается в нем и одновременно поступает ,на одни из п входов n-разрядного параллельного сумматора 7. Проинвертированный код с пинверсных выходов регистра 6 памяти поступает соответственно на другие входы параллельного сумматора 7, Пр сложений прямого и инверсного кода на выходе п-го разряда сумматора появляется сигнал, соответствующий ло гической единице, а на выходе переноса - логическому нулю. Эти значения кодов поступают на два одноразрядного сумматора 8, а на третий его вход - сигнал с прямого выхода п-го разряда регистра 6 памяти В сумматоре 8 происходит сложение по модулю два. С выхода его после nepiвого измерения разности фаз на выход блока 5 вычисления целой части разности фаз поступает сигнал, соответствующий проинвертированному значенйю п-го разряда регистра 6 памяти. Следовательно, если измеренная разность фаз О , если 360° ЛМ /180°,то QVH- 0. Это соответствует тому, что в схему 4 усреднения поступает код, соответствующей разности фаз . лЧ +360°, если О Л. Atf , если 180°: Д1 360 После измерения следующих значени разности фаз соответствующие по ступают на один из входов сумматора 7, а на другие входы - инверсный код первого измерения с регистра 6 памяти. Таким образом определяется разность между значениями разностей фаз первого и последующих измерений. Есл разность не превышает 180°, то с выхода одноразрядного сумматора 8 снимается сигнал, соответствующий инвер ному значению п-го разряда кода, соо ветствующего первому измерению разности фаз, записанному в регистре 6 .памяти. Если разность превышает 180° то снимается сигнал, соответствующий значению п-го разряда регистра памяти. Таким образом, блок 5 вычисления целой части разности фаз производит при необходимости добавление к измеренному значению разности фаз 360 и тем самым исключается перескок 0-36 Сравнение различных значений разностей фаз при вычислении целой части производи гся путем сравнения параллельных двоичных кодов и результат вычисления целой части поступает на 92 n 1 -и вход блока 4 усреднения почти одновременно с результатом очередного измерения разности фаз. За счет этого достигается высокое быстродействие. Предлагаемое устройство дозволяет измерять разности фаз между двумя сигналами при более быстром измененвд их значения за счет увеличения быстродействия и повышает технологичность за счет применения однотипных элементов. Формула изобретения . 1 .Цифровой фазометр,содержащий преобразователь фаза-код, датчики прямоугольных напряжений, выходы которых соединены со входами преобразователя фаза-код, и блок усреднения отличающийся тем, что с целью повьппения быстродействия наряду с обеспечением высокой точноста, в него введен блок вычисления целой части разности фаз, причем n выходов преобразователя фаза- код подключеш. к соответствующим n входам Фяока усреднения и к n входам блока вычисления целой части разности фаз, выход которой соединен с n + 1-м входом блока усреднения. 2. Фазометр по п.1, о т л и ч аю щ и и с я тем, что блок вычисления целой части разности фаз состоит из п-разрядного параллельного регистра памяти, п-разрядного параллельного сумматора и одноразрядного сум- матора, первый вход которого подключен к прямому выходу п-го разряда регистра памяти, второй и третий входы - к выходам п-го разряда и переноса п-разрядного сумматора, од1ш из n входов которого подключе1Ш: к соответствующим п-инверсным выходам регистра памяти, другие n входов соецкнены с соответствующими n входами регистра памяти и являются входами блока вычисления целой части разности фаз, а выход одноразрядного суматора - его выходом. Источники информации, ринятые во внимание при экспертизе 1.Авторской свидетельство СССР 216841, кл. G 01 R 25/00, 03.04.65. 2.Авторское свидетельство СССР 489047, кл. G 01 R 25/00, 26.03.74.

Авторы

Даты

1981-05-30—Публикация

1979-07-06—Подача