Изобоетение относится к технике фазовых измерений, мол ет быть использовано для измерения фаэово-о сдвига между двумя периодическими сигналами с фиксированной частотой и является усовершенствованием изобретения по авт.св. № 834592.

Целью изобретения является повышение помехозащищенности фазометра.

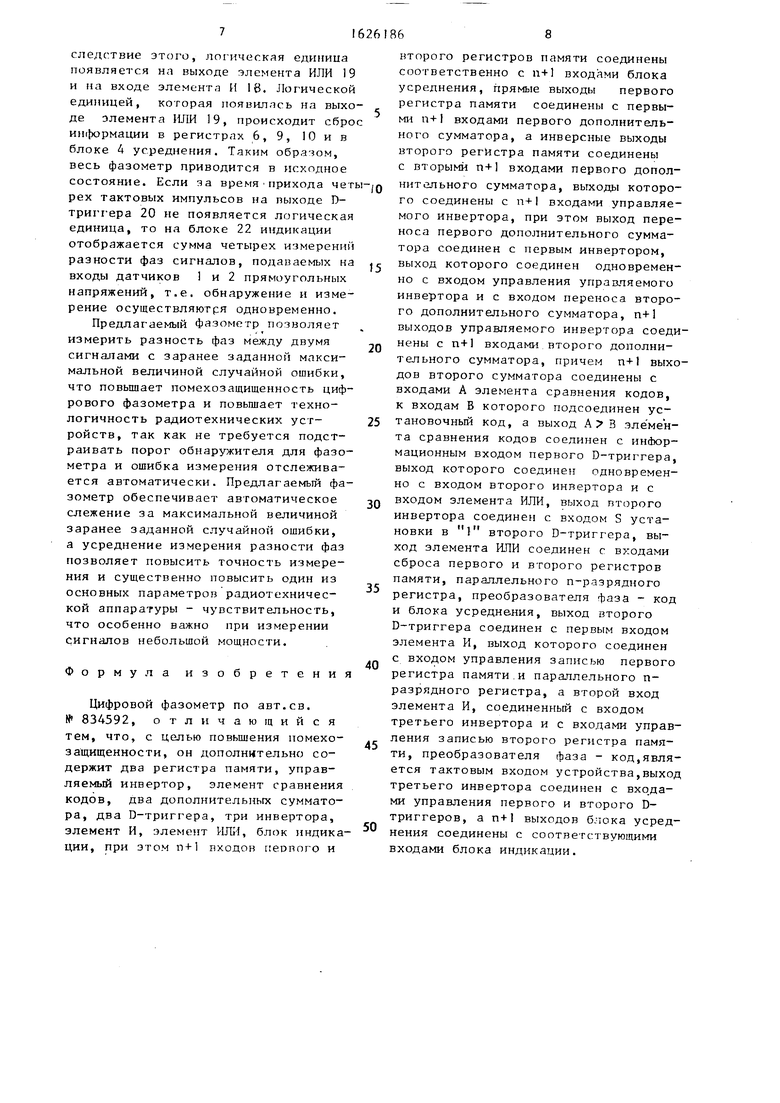

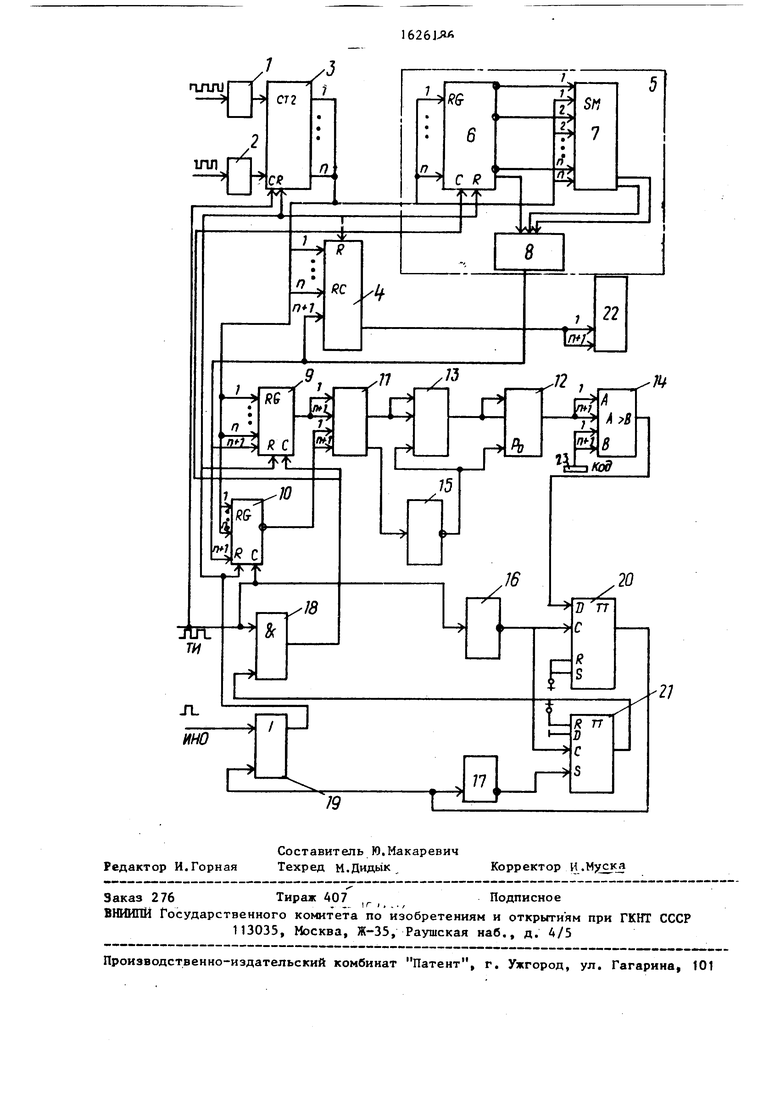

На чертеже представлена функциональная схема цифрового фазометра.

Фазометр состоит из датчиков 1 и 2 прямоугольных напряжений, преобра- зочагеля 3 фаза - код, блока 4 усреднения, блока 5 вычисления целой части разности фаз, состоящего и параллельного n-ррзрядчого регистра 6 памяти, параллельного п-разрядного сумматора 7 и одноразрядного сумматора 8. Выходы датчиков 1 и 2 прямоугольных напряжений соединены с входами преобразователя 3 фаза - код,выходы которого с соответствующими п входами блока 5 вычисления

целой части разности фаз и с п вхсда- ми блока 4 усреднения, (п+1)-ч вход которого подключен к выходу блока 5 вычисления целой части разности фаз, причем первый вход одноразрядного сумматора 8 подключен к прямому выходу n-го разряда регистра 6 памяти,второй вход - к выходу n-го разряда, а третий вход - к выходу переноса п-разрядного сумматора 7. Первые из п входов n-разрядного сумматора 7 подключены к соответствующим п инверсным выходам регистра 6 памяти, вторые из п входов сумматора 7 соединены с соответствующими п входами регистра 6 памяти и являются входами блока 5 вычисления целой части разности фаз, а выход одноразрядного сумматора 8 - его выходом.

Фазометр содержит также два (п+1)- разрядных регистра 9 и 10 памяти, п входов которых соединены с выходами преобразователя 3 фаза - кед, а (п+1)-й вход соединен с выхолом одноразрядного сумматора 8, а го

ш (Л

тА ф

ю

о

00

0

14)

держит два сумматора 11 и 12 управляемый инвертор 13, элемент 14 сравнения кодов, три инвертора 15-17, элемент И 18, элемент ИЛИ 19, два D-триггера 20 и 21, блок 22 индикации и задатчик 23 кода Е. Прямые выходы регистра 9 и инверсные выходы регистра 10 соединены-с соответствующими (п+1)-ми входами сумматора 1I, причем выходы сумматора 11 соединены с соответствующими входами управляемого инвертора, а выход переноса сумматора 11 через инвертор 15 соединен с входами управляемого инвертора 13 и входом переноса сумматора 12, (п+1) выходов управляемого инвертора 13 соединены с соответствующими (п+1) входами сумматора 12, (п+1) выходов сумматора 12 соединены с соответствующими (п+1) входами А элемента 14 сравнения, а входы В элемента 14 сравнения соединены с задатчиком 23 кода В (пороговое значение кода). Выход элемента 14 сравнения соединен с входом D-триггера 20, а вход управления последнего соединен с входом управления D-триггера 21 и выходом инвертора 16, причем выход D-триггера 20 соединен с входом инвертора 17 и входом элемента ИЛИ 1е1. Выход инвертора 17 соединен с входом установки в 1 (вход S) D-триггера 21. Выход последнего соединен с одним из входов элемента И 18, выход которого соединен с входом управления регистров 9 и 6. Второй вход элемента И 18 соединен с входом управления регистра 10, с

10

15

20

25

30

35

рить. С выходов датчиков 1 и 2 прямоугольных напряжений сигналы поступают на входы преобразователя 3 cba- за - код, где разность фаз преобразуется во временной интервал. Интервал заполняется импульсами генератора квантующей частоты, а количество импульсов подсчитывается счетчиком и в виде двоичного параллельного кода имеется на выходе преобразователя 3 фаза - код. Таким образом измеряется дробная часть разности фаз.

С выхода преобразователя 3 фаза - код коды, соответствующие измеренным разностям фаз, поступают на входы блока 4 усреднения и входы блока 5 вычисления целой части разности фаз. В зависимости от значений кодов,соответствующих первому измерению или каждому последующему, с выхода блока 5 вычисления целой части разности фаз на вход (п+1)-го разряда блока 4 усреднения поступает сигнал либо логического нуля, либо единицы.Логическая единица соответствует прибавлению к измеренному значению разности фаз 360°. Это необходимо для выравнивания перескока 0-360° при усреднении значений разности фаз.Информация с блока 5 вычисления целой части обновляется при подаче тактовых импульсов (ТИ). Всего их может быть четыре (при усреднении по четырем замерам). Время прихода тактовых импульсов жестко связано с импульсом ИНО, а между собой они следуют через время, равное 4Т (где Т - период повторения частоты, поступающей на

входом инвертора 16 и входом управле-40 ВХ°ДЫ датчиков 1 и 2). Время 4Т выбния преобразователя 3 фаза - код. Вход D-триггера 21 соединен с корпусом фазометра, Вход R D-триггера 21 соединен с источником питания микросхем. Входы R и S D-триггера 20 также соединены с источником питания микросхем.

Цифровой фазометр работает следующим образом.

Через элемент ИЛИ 19 импульс начала обработки (ИНО) поступает на вхрд , сброса (вход R) регистров 6, 9 и 10 И на вход сброса преобразователя 3 фаза - код. По окончании импульса фазометр готов к обработке информации.

На датчики 1,2 прямоугольных напряжений поступают сигналы, разность фаз между которыми необходимо изме45

50

55

рано ввиду того, что полиса пропускания предыдущего радиотехнического тракта имеет полосу пропускания,обеспечивающую за время AT с Ыбую корреляционную связь.

В блоке 4 усреднения последовательно складываются четыре значения разности фаз.

В блоке 5 вычисления целой части разности фаз двоичный n-разрядный параллельный код, соответствующий первой измеренной преобразователем 3 фаза - код разности фаз, поступает на соответствующие п входов параллельного регистра 6 памяти, запоминается в нем и одновременно поступает на одни из п входов п-раэрядно- го параллельного сумматора 7, Про- инвентированный код с п инверсных

5

0

5

0

5

рить. С выходов датчиков 1 и 2 прямоугольных напряжений сигналы поступают на входы преобразователя 3 cba- за - код, где разность фаз преобразуется во временной интервал. Интервал заполняется импульсами генератора квантующей частоты, а количество импульсов подсчитывается счетчиком и в виде двоичного параллельного кода имеется на выходе преобразователя 3 фаза - код. Таким образом измеряется дробная часть разности фаз.

С выхода преобразователя 3 фаза - код коды, соответствующие измеренным разностям фаз, поступают на входы блока 4 усреднения и входы блока 5 вычисления целой части разности фаз. В зависимости от значений кодов,соответствующих первому измерению или каждому последующему, с выхода блока 5 вычисления целой части разности фаз на вход (п+1)-го разряда блока 4 усреднения поступает сигнал либо логического нуля, либо единицы.Логическая единица соответствует прибавлению к измеренному значению разности фаз 360°. Это необходимо для выравнивания перескока 0-360° при усреднении значений разности фаз.Информация с блока 5 вычисления целой части обновляется при подаче тактовых импульсов (ТИ). Всего их может быть четыре (при усреднении по четырем замерам). Время прихода тактовых импульсов жестко связано с импульсом ИНО, а между собой они следуют через время, равное 4Т (где Т - период повторения частоты, поступающей на

5

0

5

рано ввиду того, что полиса пропускания предыдущего радиотехнического тракта имеет полосу пропускания,обеспечивающую за время AT с Ыбую корреляционную связь.

В блоке 4 усреднения последовательно складываются четыре значения разности фаз.

В блоке 5 вычисления целой части разности фаз двоичный n-разрядный параллельный код, соответствующий первой измеренной преобразователем 3 фаза - код разности фаз, поступает на соответствующие п входов параллельного регистра 6 памяти, запоминается в нем и одновременно поступает на одни из п входов п-раэрядно- го параллельного сумматора 7, Про- инвентированный код с п инверсных

выходов регистра ь памяти поступает соответственно на другие входы параллельного сумматора 7. При сложении прямого и инверсного кодов на выходе n-го разряда сумматора 7 появляется сигнал., соотьетствующий логической единице, а на выходе переноса - сигнал, соответствующий логическому нулю. Эти значения кодов поступают на два входч одноразрядного сумматора 8, на третий его вход поступает сигнал с прямого выхода n-го разряда регистра 6 памяти. В сумматоре 8 происходит сложение по модулю два. С его выхода после первого измерения разности Лаз поступает сигнап, соответствующий инвертированному значению n-го разряда регистра 6 па- мя ти.

Следовательно, если измеренная разность Фаз 1 30°, 1,

П-Н

Г. Это

° если ,

если 180° /У| :3600

если ЗбО АЧМвО0, тооС соответствует тому, что в блок 4 ус реднения поступает код, соответствующий разности (Ьаз

UCf+360

ДЛЬ

После измерения следующих значений разности фаз соответствующие коды поступают на один из входов сумматора 7, на другие входы поступает инверсный код первого измерения с регистра 6 памяти. Таким образом определяется разность между значениями разностей фаз первого и последующих измерений. Если разность не превышает 180°, то с выхода одноразрядного сумматора 8 снимается сигнал.соответствующий инверсному значению п-го разряда кода, соответствующего первому измерению разности фаз, записанному в регистр 6 памяти.0

Если разность превышает 180 , то

снимается сигнал, соответствующий значению n-го разряда регистра 6 памяти. Таким образом, блок 5 вычисления целой части разности фаз производит при необходимости добавление к измеренному значению разности фаз 360 и тем самым исключается перескок О -360.

Двоичный арифметический п-разряд- ный код с выхода преобразователя 3 фаза - код и (п+1)-й разряд с выхода одноразрядного сумматора 8 поступают на соответствующие n-Н входов паралШ. г ррг-.п 1 р

ПСГгВО 41 ГГ С ННО

5

лельных регистров 9 и 9 записывается только кода, измеренчое прообрачов тел м 3 фаза код по приходу на ихсъ: управления первого тактового ичпульга.тнм же тактовым импульсом прэнтврднгся запись значения этого же код в регистр 10. Прямой код с регистра 9 и

инверсный код с регистра 10 подаются на соответствующие входы сумматора 11. На последнем, таким образом,находится разность между двумя апи- сачнь мн числами в регистре 9 к в регистре 10. С выходов сумматора 11 число (выраженное двоичным параллельным кодсм) подается на управляемый инвертор. В зависимости от того,какое число больше: число в регистре 9 ILIH число в регистре 10, на выходе перекоса сумматора появляется лти- ческая единица или логический нуль. Этот сигнал через инвертор 15 подает ч на вход управления управляемо5 го инвертора 13 и на вход переноса сумматора 12. На выходе последнего появляется код, равный модулю разности кодов, записанных в регистрах 9 и 10. Это значение модуля разнпс0 ти подается на входы А элемент т 14 сравнения и сравнивается с ходим, подаваемым на входы В от чадатчика 23. Если код числа, подаваемый на вход А, меньше числа, определяемо5 го кодом В, то на выходе А В элемента 14 сравнения есть сигнал ло.- ческого нуля, который подается на вход D D-триггера 20. Этот логический нуль появляется на выходе D-триг0 гера 20 по окончании сигнала управления (так как он подается на вход управления D-триггера 20 через инвертор 16). Сигнал с выхода D-триггера 20 через инвертор 7 поступает на

5 вход D-триггера 21, т.е. на вход S подается логическая единица. Следовательно, на выходе D-триггера появляется логический нуль. Этот логический нуль подается на вход элемента

0 И 18. Значит следующие тактовые импульсы на проходят на вход управления регистров 9 и 6. После этого перезапись кодов измеренной разности фаз по приходу тактовых импульсов произ5 водится только в регистр 10. Если модуль разности измеренных разностей фаз больше кода В в элементе 14 сравнения, то на выходе последнего появляется логическая единица. И, как

следствие этого, логическая единица появляется на выходе элемента ИЛИ 19 и на входе элемента И 18. Логической единицей, которая появилась на выходе элемента ИЛИ 19, происходит сбро информации в регистрах 6, 9, 10 и в блоке А усреднения. Таким образом, весь фазометр приводится в исходное состояние. Если за времяприхода чет рех тактовых импульсов на выходе D- триггера 20 не появляется логическая единица, то на блоке 22 индикации отображается сумма четырех измерений разности фаз сигналов, подаваемых на входы датчиков 1 и 2 прямоугольных напряжений, т.е. обнаружение и измерение осуществляютря одновременно. Предлагаемый фазометр позволяет измерить разность фаз между двумя сигналами с заранее заданной максимальной величиной случайной ошибки, что повышает помехозащищенность цифрового фазометра и повышает технологичность радиотехнических уст- ройств, так как не требуется подстраивать порог обнаружителя для фазометра и ошибка измерения отслеживается автоматически. Предлагаемый фазометр обеспечивает автоматическое слежение за максимальной величиной заранее заданной случайной ошибки, а усреднение измерения разности фаз позволяет повысить точность измерения и существенно повысить один из основных параметров радиотехнической аппаратуры - чувствительность, что особенно важно при измерении сигналов небольшой мощности.

Формула изобретения

Цифровой фазометр по авт.св. № 834592, отличающийся тем, что, с целью повышения номехо- защищенности, он дополнительно содержит два регистра памяти, управляемый инвертор, элемент сравнения кодов, два дополнительных сумматора, два D-триггера, три инвертора, элемент И, элемент ИЛ, блок индикации, при этом п+1 входов первого и

а-

-jQ jc -д250

35

40

. 50

второго регистров памяти соединены соответственно с п+1 входами блока усреднения, прямые выходы первого регистра памяти соединены с первыми п+1 входами первого дополнительного сумматора, а инверсные выходы второго регистра памяти соединены с вторыми п+1 входами первого дополнительного сумматора, выходы которого соединены с п+1 входами управляемого инвертора, при этом выход переноса первого дополнительного сумматора соединен с первым инвертором, выход которого соединен одновременно с входом управления управляемого инвертора и с входом переноса второго дополнительного сумматора, п+1 выходов управляемого инвертора соединены с п+1 входами второго дополнительного сумматора, причем п+1 выходов второго сумматора соединены с входами А элемента сравнения кодов, к входам В которого подсоединен установочный код, а выход А 3 элемента сравнения кодов соединен с информационным входом первого D-триггера, выход которого соединен одновременно с входом второго инвертора и с входом элемента ИЛИ, выход второго инвертора соединен с входом S установки в 1 второго D-триггера, выход элемента ИЛИ соединен г входами сброса первого и второго регистров памяти, параллельного п-разрядного регистра, преобразователя фаза - код и блока усреднения, выход второго D-триггера соединен с первым входом элемента И, выход которого соединен с входом управления записью первого регистра памяти и параллельного п- разрядного регистра, а второй вход элемента И, соединенный с входом третьего инвертора и с входами управления записью второго регистра памяти, преобразователя фаза - код,является тактовым входом устройства,выход третьего инвертора соединен с входами управления первого и второго D- триггеров, а п+1 выходов блока усреднения соединены с соответствующими входами блока индикации.

/Zii.

3

ЩЦ

Ц±эКод

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1979 |

|

SU834592A1 |

| Цифровой фазометр | 1980 |

|

SU932423A1 |

| Устройство для измерения угла фазового сдвига гармонических сигналов | 1990 |

|

SU1765781A1 |

| Цифровой фазометр мгновенных значений | 1986 |

|

SU1348745A2 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Фазометр | 1980 |

|

SU892344A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Цифровой фазометр | 1982 |

|

SU1027638A2 |

Изобретение позволяет измерить фазовый сдв1Т между двумя периодическими с фиксированной частотой и пиьь-пенными помехами, Указанная цель достигается тем, чю в цифровой фазометр дополнительно введена схема слежения та ьелп-j ной максимальной ошибки,что обеспечивает сравнение каждого измерения с первым и сравнение разнины между ними с заданной величш он.Канал, измеряющий разность фаз,одновременно ВОЗМОАНО использовать в качестве обнаружителя. 1 ил.

RG

TL ТИ

&

Л.

ИНО

.16

.20

Б Г7

Г7 5

| Катодная лампа | 1924 |

|

SU834A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| I | |||

Авторы

Даты

1991-02-07—Публикация

1988-11-22—Подача