(54) ДИНАМИЧЕСКИЙ ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1979 |

|

SU830579A1 |

| Многовыходной вентиль и-не | 1979 |

|

SU813790A1 |

| Логическое устройство | 1984 |

|

SU1213521A1 |

| Полупроводниковое постоянное запоминающее устройство | 1978 |

|

SU763968A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| НИЗКОВОЛЬТНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ БИПОЛЯРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ СТРУКТУРАХ | 1999 |

|

RU2173915C2 |

| Логический элемент | 1978 |

|

SU729847A1 |

| Интегральная логическая схема | 1977 |

|

SU633395A1 |

| Запоминающий элемент | 1974 |

|

SU491155A1 |

| Формирователь импульсов выборки информации из памяти | 1982 |

|

SU1148046A1 |

Изобретение относится к области автбматики и вычислительной техники. Известны различные варианты пинамических запоминающих элементов, цинами- ческий режим хранения информации в которых обеспечивает малые мощности, потребляемые в режиме хранения информации, что, в частности, достигается использованием цополняющих биполярных транзисторо h-р-и и р и-р-типа. Известны динамические запоминающие элементы ЙЩ, которые в прухмерную матрицу накопителя запоминающего устройства включаются овумя ВХОЦР.МИ. Наличие только овух вхоцов у таких матричных пинамических элементов (МДЭ) приводит к низкому быстро цействию и низкой помехоустойчивости, а также резко усложняет схемы обрамления, так как по указанным двум входам должны осуществляться питание МДЭ (и регенерация накопленного на его емкостях заряда наличие или отсутствие которого ставят в соответствие записанной в элемент информации - логической 1 или логическому О) перезапись информации и ее считывание. Известны также МДЭ . Наиболее близким по технической сущности к изобретению является МДЭ sl на двух дополндйщих биполярных транзисторах, содержащий первый и второй вьшоды питания и управляющий вход, эмиттер П -р-и-транзистора соединен с первым входом элемента, эмиттер р-п-р-тран зистора - со вторым входом, база р - и-Р транзистора соединена с коллектором п-р-п-транзистора, коллектор р-и-ртранзистора - с базой .н-р-и-транзистора. Недостатками известного МДЭ являются низкие функциональные возможности и относительно невысокое быстродействие. Целью изобретения является расширение ф нкциональных возможностей и повышение быстродействия МДЭ. Поставленная цель достигается , что р-п-р-транзнстор содержшт дополнительные коллекторы, соединенные с выходами, элемента, а его основной коллектор

соеоинен с управляющим входом элемента, и тем, ч,то в него введен диоц Шоттки, анод которого х единев с базой п-р Итранзистора, а катод - с базой р-п-ртранзистора.

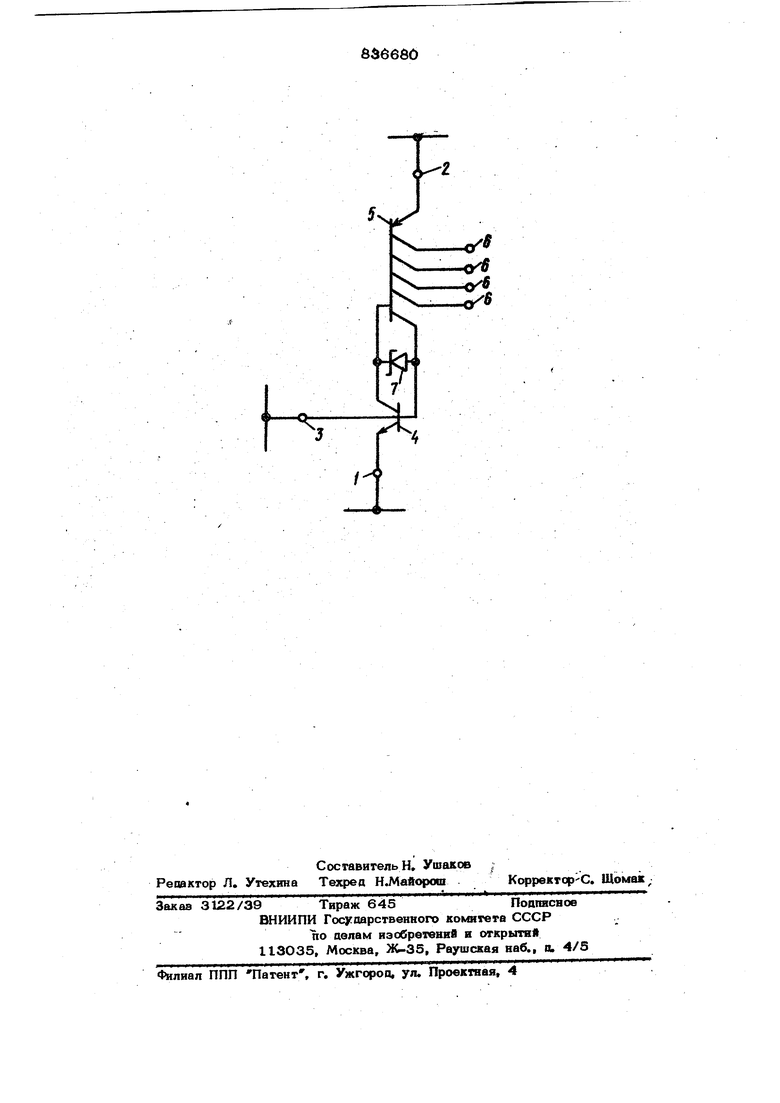

На чертеже прецставлена электрическая схема МДЭ,

Предлагаемый МДЭ содержит первый и второй вьшоаы питания 1и 2 соотве ственно и угфавляющий вход 3.

Эмиттер м-р-и-транзистора 4 соедине с первым вьшодом I, база - с угфавляющим входом 3, Эмиттер р-И-Р-транзистора 5.соединен со вторым вьтодом 2. База р-И-р-транзистора 5 соединена с . коллектором и-р-«-транзистора 4, коплектор р-П-р-транзистора 5 соединен с базой м-р-h-транзистора 4. Допога1итепь- ные коллекторы р-п-р транзистора 5 соединены с выходами 6 элемента, число которых, например, при двухмерной организшши матрицы и минимальном числе связей между МДЭ, равно четырем (фиг.1).

Наличие положительной обратной связи по току между дополняющими транзисторами приводит к регенерации сигнала в каждом МДЭ вследствие большого усиления тока, ограничиваемого лишь режимом питания. В зависимости от режима питания (например, двух- или многофазного) предлагаемый элемент наряПу с хранением информации одновременно выполняет как неинвертирующие (например, ИЛИ), так и инвертирующие (например, Запрет) функции.

Эти свойства предлагаемого элемента и разделение его информационных входа , и выходов существенно расширяют его функциональные возможности и область применения, например, в многофункциональных ассоциативных ЗУ либо матрицах с двумерным-, переносом информации.

Отметим также, что предлагаемый МДЭ при его технологической реализации очень хорошо сверхинтегрируется в вице компактной интегральной схемы.

Повышение быстродействия в предлагаемом МДЭ связано с тем, что нет необходимости импульсной подпитки (регенерации) хранящейся в нем информации, и с тем, что вследствие имеющего место в МДЭ регенеративного процесса увеличения тока при включении р-и-р транзистор приводит к еще более быстрому его включению, а уменьшение тока при включении

р-и-р-транзистора приводит к еще более быстрому его включению. Взаимосвязи межцу элементами предлагаемого МДЭ и иной принцип его действия позволяют эффективно использовать в нем для дальнейшего повышения быстродействия (за счет ограничения насыщения дополняющих транзисторов при их включении) диод Шоттки 7. В прототипе его использование исключено.

Изобретение может быть использовано при проектировании и в произЕЮдстве многофункциональных элементов, используемых при создании сложных логических устройств с распределенной памятью.

Формула изобретения

Динамический запоминающий элемент, содержащий два биполярных дополняющих транзистора tt-p-h и р-и-р-тинов, эмиттер П-р-и «транзистора соединен с первым выводом питания, базы - с основным коллектором р -и- р транзнстора, а коллектор - с базой р-и-р-транзистора, эмиттер которого соединен со вторым выводом питания, и управляющий вход и вькоды, отличающийся тем, 4TOj с целью повышения быстродействия элемента, р-И-р-транзистор содержит дополнительные коллекторы, соединенные с выходами элемента, а его основной коллектор соединен с управляющим входом элемента.

Источники информации, принятые во при экспертизе

с, 41, рис, 12а.

TectiH. Papers, 1976, p. 182 (прототип/.

Авторы

Даты

1981-06-07—Публикация

1979-07-04—Подача