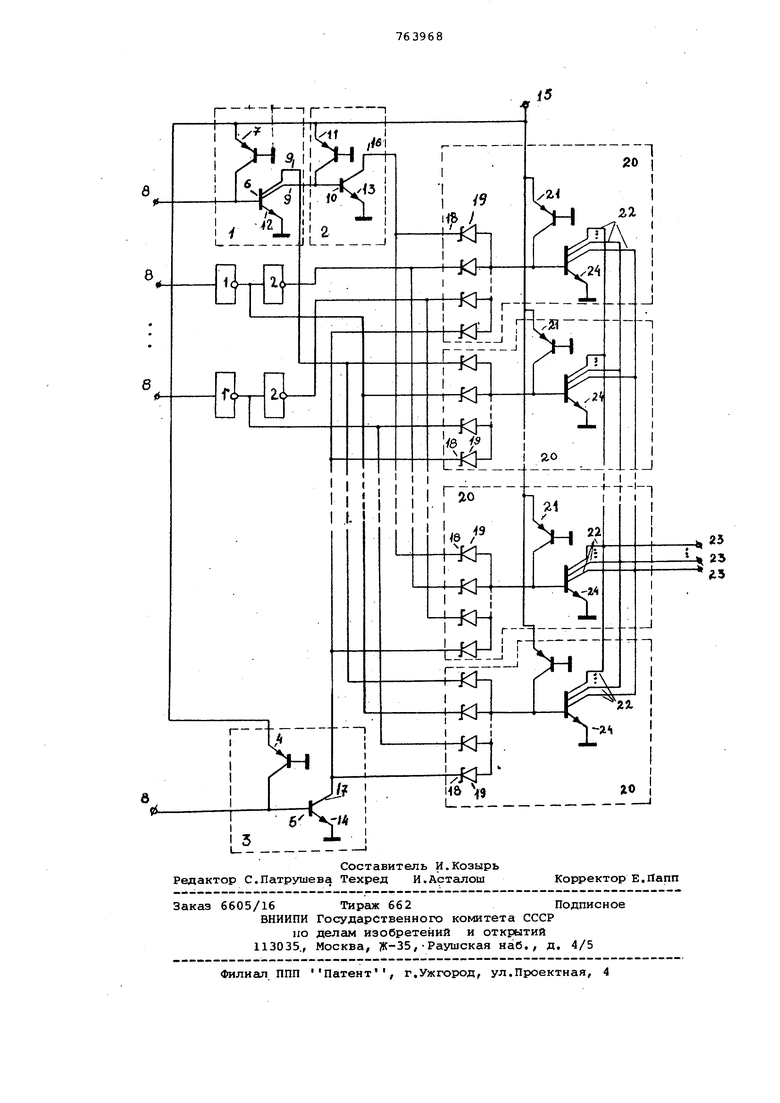

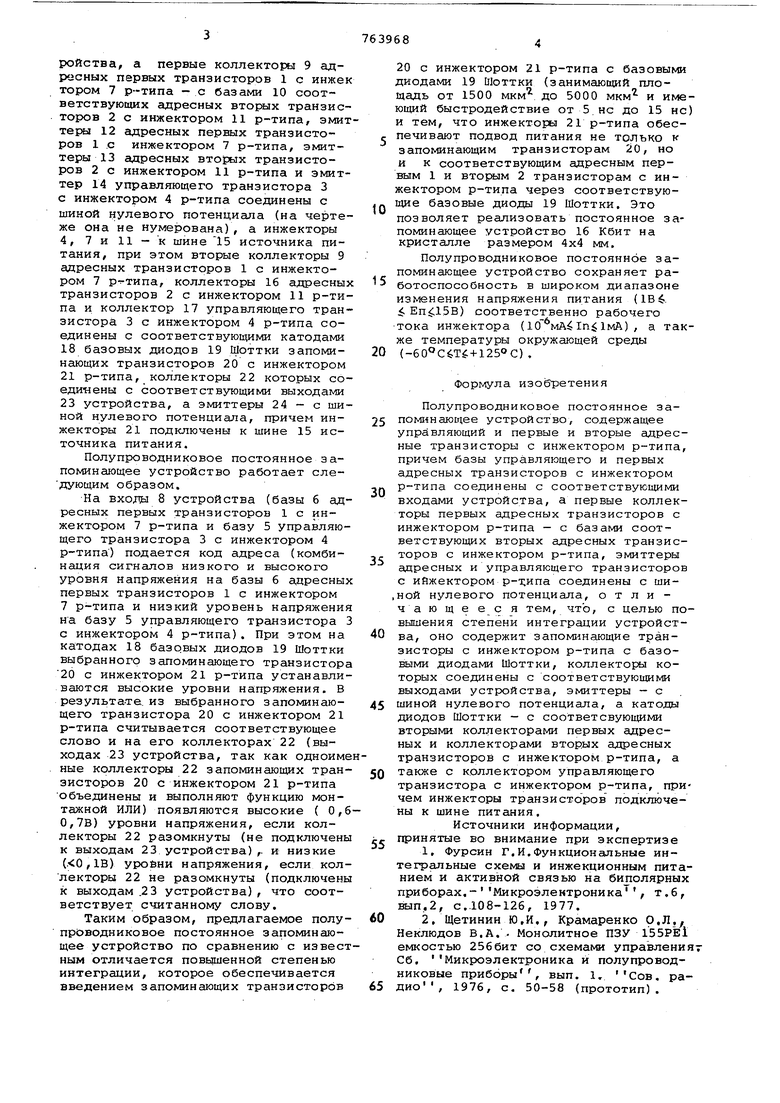

Изобретение относится к вычисли тельной технике и автоматике и может быть использовано в устройствах обработки цифровой информещии в качестве табличных данных, программ, подпрогрги м, преобразователей кодов и др. Известно полупроводниковое запоминающее устройство, содержсвдее запоминающие транзисторы с инжектором р-типа с базовыми диодами Шоттки Наиболее близким техническим решением к изобретению является полупроводниковое постоянное запоминающее устройство, содержащее адресные формирователи, инвертор разрииения выборки, элементы дешифратора, тран зисторы матрицы и усилители счйтывания 2 . Недостатками этих полупроводнико вых постоянных запоминающих устройс является низкая степень интегргщии, что ограничивает информационную емкость устройства. Цель изобретения - повышение сте пени интеграции полупроводникового постоянного запоминающего устройства. Поставленная цель достигается тем, что полупроводниковое постоянное запоминающее устройство содержит запоминающие транзисторы с инжектором р-типа с базовыми диодами Шоттки, коллекторы которых соединены с соответствующими выходами устройства, эмиттеры - с шиной нулевого потенциала, а катоды диодов Шоттки с соответствующими вторыми коллекторами первых адресных и коллекторами вторых адресных транзисторов с инжектором р-типа, а также с коллектором управляющего транзистора с инжектором р-типа, причем инжекторы транзисторов подключены к шине питания. На чертеже представлена электрическая схема полупроводникового постоянного запоминающего устройства. Полупроводниковое постоянное затпоминающее устройство содержит адресные первые 1 и вторые 2 транзистоЕял с инжектором р-типа, а также управляющий транзистор 3 с инжектором 4 р-типа, база 5 которого и ба-зы 6 адресных первых транзисторов с инжектором 7 р-типа соединены с соответствующими входами 8 устройства, а первые коллекторы 9 адресных первых транзисторов 1 с инжек тором 7 р-типа - с базами 10 соответствующих адресных вторалх транзисторов 2 с инжектором 11 р-типа, эмиттеры 12 адресных первых транзисторов 1 .с инжектором 7 р-типа, эмиттеры 13 адресных вторых транзисторов 2 с инжектором 11 р-типа и эмиттер 14 управляющего транзистора 3 с инжектором 4 р-типа соединены с шиной нулевого потенциала (на чертеже она не нумерована), а инжекторы 4, 7 и 11 - к шине 15 источника питания, при этом вторые коллекторы 9 адресных транзисторов 1 с инжектором 7 р-типа, коллекторы 16 адресных транзисторов 2 с инжектором 11 р-типа и коллектор 17 управляющего транзистора 3 с инжектором 4 р-типа соединены с соответствующими катодами 18 базовых диодов 19 Шоттки запоминающих транзисторов 20 с инжектором 21 р-типа, коллекторы 22 которых соедииены с соответствующими выходами 23 устройства, а эмиттеры 24 - с шиной нулевого потенциала, пpичe 1 инжекторы 21 подключены к шине 15 источника питания.

Полупроводниковое постоянное запоминающее устройство работает следующим образом.

На входы 8 устройства (базы 6 адресных первых транзисторов 1 с инжектором 7 р-типа и базу 5 управляющего транзистора 3 с инжектором 4 р-типа) подается код адреса (комбинация сигналов низкого и высокого уровня напряжения на базы 6 адресных первых транзисторов 1 с инжектором 7 р-типа и низкий уровень напряжения на базу 5 управляющего транзистора 3 с инжектором 4 р-типа). При этом на катодах 18 базовых диодов 19 Шоттки выбранного Запоминающего транзистора 20 с инжектором 21 р-типа устанавливаются высокие уровни напряжения. В результате, из выбранного запоминающего транзистора 20 с инжектором 21 р-типа считывается соответствующее слово и на его коллекторах 22 (выходах 23 устройства, так как одноименые коллекторы 22 запоминающих транзисторов 20 с инжектором 21 р-типа Объединены и выполняют функцию монтажной ИЛИ) появляются высокие ( 0,6 0,7В) уровни напряжения, если коллекторы 22 разомкнуты (не подключены к выходам 23 устройства) ,. и низкие (.0, 1В) уробни напряжения, если коллекторы 22 не разомкнуты (подключены к выходам .23 устройства) , что соответствует считанному слову.

Таким образом, предлагаемое полупроводниковое постоянное запоминающее устройство по сравнению с известным отличается повышенной степенью интеграции, которое обеспечивается введением запоминающих транзисторов

20 с инжектором 21 р-типа с базовыми диодами 19 Шоттки (занимающий площадь от 1500 мкм до 5000 мкм и имеющий быстродействие от 5.не до 15 не) и тем, что инжекторы 21 р-типа обесс печивают подвод питания не тсэлъко к запоминающим транзисторам 20, но и к соответствующим адресным первым 1 и вторым 2 транзисторам с инжектором р-типа через соответствуюQ щие базовые диоды 19 Шоттки. Это

позволяет реализовать постоянное запоминающее устройство 16 Кбит на кристалле размером 4x4 мм.

Полупроводниковое постоянное запоминающее устройство сохраняет ра ботоспособность в широком диапазоне изменения напряжения питания (18$. . ) соответственно рабочего тока инжектора ( 1п 1мА) , а также температуры окружающей среды

0 (-60°C T.f + 1250C) .

Формула изобретения

Полупроводниковое постоянное за5 поминающее устройство, содержащее

управляющий и первые и вторые адресные транзисторы с инжектором р-типа, причем базы управляющего и первых адресных транзисторов с инжектором р-типа соединены с соответствую щими входами устройства, а первые коллекторы первых адресных транзисторов с инжектором р-типа - с базами соответствующих вторых адресных транзисторов с инжектором р-типа, эмиттеры адресных и управляющего транзисторов с ийжектором р-1;ипа соединены с ши,ной нулевого потенциала, отличающееся тем, что, с целью повышения степени интеграции устройст0 ва, оно содержит запоминающие транзисторы с инжектором р-типа с базовыми диодами Шоттки, коллекторы которых соединены с соответствующими выходами устройства, эмиттеры - с

5 шиной нулевого потенциала, а катоды диодов Шоттки - с соответсвующими вторыми коллекторами первых адресных и коллекторами вторых адресных транзисторов с инжектором р-типа, а

Q также с коллектором управляющего

транзистора с инжектором р-типа, причем инжекторы транзисторов подключены к шине питания.

Источники информации,

f принятые во внимание при экспертизе 1. Фурсин г.и.функциональные интегральные схемы и инжекционным питанием и активной связью на биполярных приборах,-Микроэлентроника, т,6, вып.2, с..108-126, 1977.

02. Щетинин Ю,И., Крамаренко О.Л,,

Неклюдов В.А.. Монолитное ПЗУ 155РЁ1 емкостью 256бит со схема1 от управления Сб. Микроэлектроника и полупроводниковые приборы , вып. 1, Сов. ра5 дио, 1976, с. 50-58 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Устройство для управления диодными дешифраторами адреса | 1989 |

|

SU1705869A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Логический элемент | 1984 |

|

SU1173551A1 |

| Накопитель для полупроводникового запоминающего устройства | 1980 |

|

SU955202A1 |

| Устройство согласования | 1986 |

|

SU1383483A1 |

| Устройство согласования | 1984 |

|

SU1173552A1 |

| Элемент памяти | 1981 |

|

SU978328A1 |

| Динамический логический элемент | 1979 |

|

SU822370A1 |

| Синхронный логический элемент | 1976 |

|

SU573881A1 |

Авторы

Даты

1980-09-15—Публикация

1978-02-20—Подача