I

Изобретение относится к вычислительной технике и автоматике и может быть использовано в аппаратуре обработки цифровой информации.

Известен делитель частоты, содержащий управляемый счетчик, состоя11щй из четырех последовательно включенных О-триггеров, счетные входы первых трех О-триггеров объединены и являются входом делителя частоты, цепи обратной связи, образованной из трех последовательно включенных логических схем, первая из которых имеет вход управления коэффициентом деления OlНедостатком данного устройства является ограниченное быстродействи обусловленное наличием дополнительных задержек прохождения сигнала через цепи обратной связи, которые создаются за счет включения в обратную связь различных логических элементов, например И и ИЛИ.

Наиболее близким по технической сущности к изобретению является делитель частоты с коэффициентами деления 9 или 10, содержащий кольцевой счетчик, выполненный на пяти последовательно включенных счетных триггерах, на объединенные счетные входы которых подан входной сигнал, причем выход пятого счетного триггера подключен через инвертор к ииформационому входу первой пересчетной схемы, а для изменения коэффициента деления с 10 на 9 информационный вход пятого счетного триггера за счет коммутирующего устройsства, управляемого внешним сигналом, переключается с вькода четBeiJToro счетного триггера на выход элемента И, первый и второй входы которого подключены соответственно к выходам третьего и четвертого счетных триггеров

Недостатком данного делителя частоты является также ограниченное

быстродействие, обуслоЕлениое наличием дополнительных задержек прохождения сигнала через элемент И и коммутирующее устройство.

Цель изобретения - повышение , быстродействия.

-Поставленная цель достигается тем, что в делитель частоты следования импульсов с коэффициентами деения N и N + 1, содержащий тригге- ю ры, счетные входы первого и второго из которых соединены с входной шиной, прямой выход первого триггера соединен с первым входом второго триггера, и блок совпадения, введен 15 елитель частоты на N/2, выход которого соединен с первым входом блока совпадения, второй вход которого соединен с прямым выходом второго триггера и входом делителя частоты 20 на N/2, третий вход - с шиной управления, а выход - с первым входом третьего триггера, счетньй вход которого соединен с инверсным выходом первого триггера, а выход - с 25 первым входом первого триггера,второй вход которого соединен с инверсным выходом второго триггера.

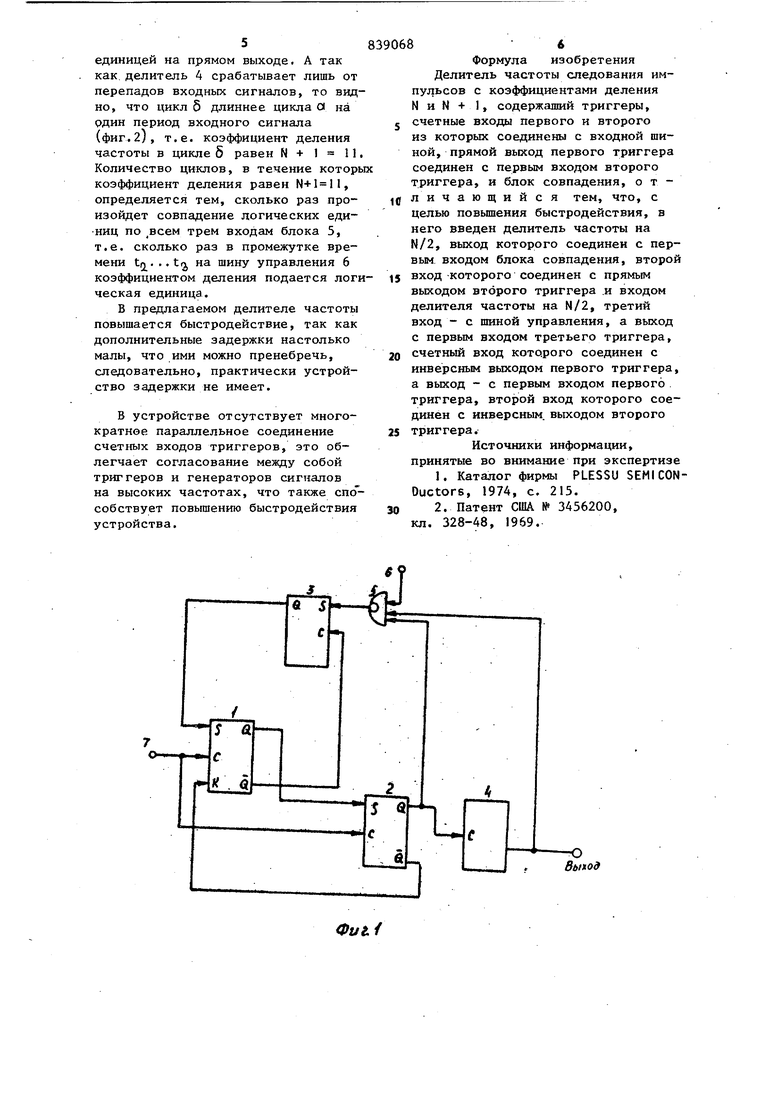

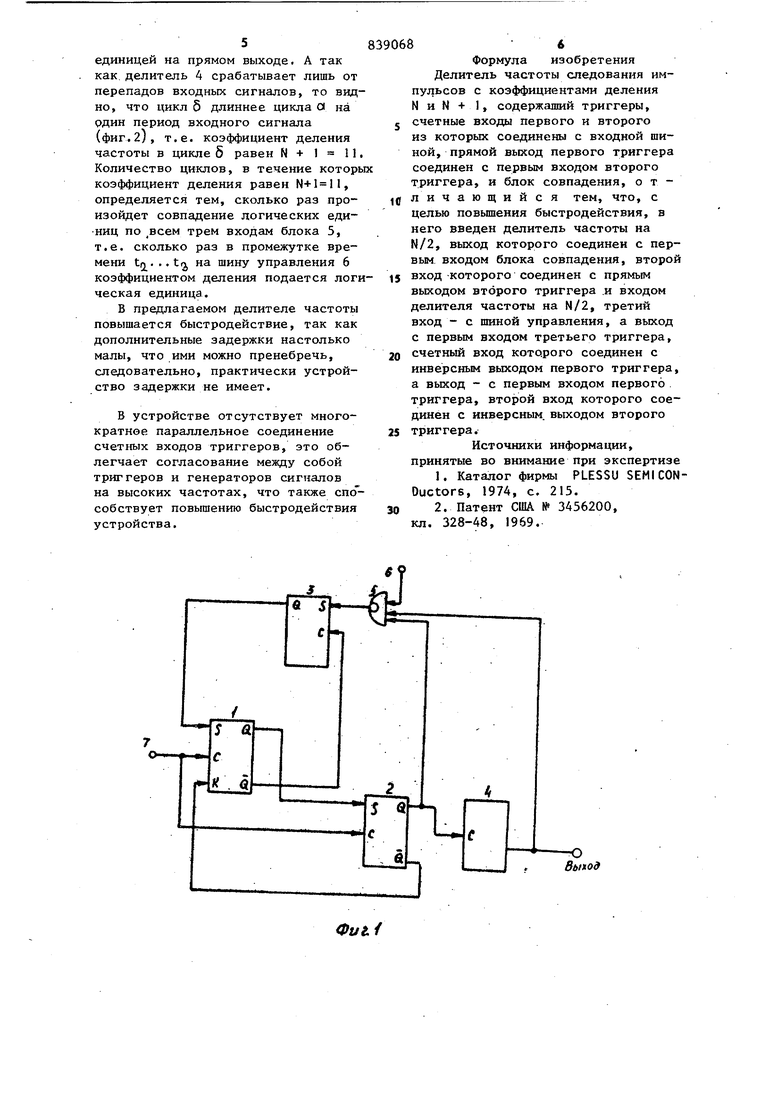

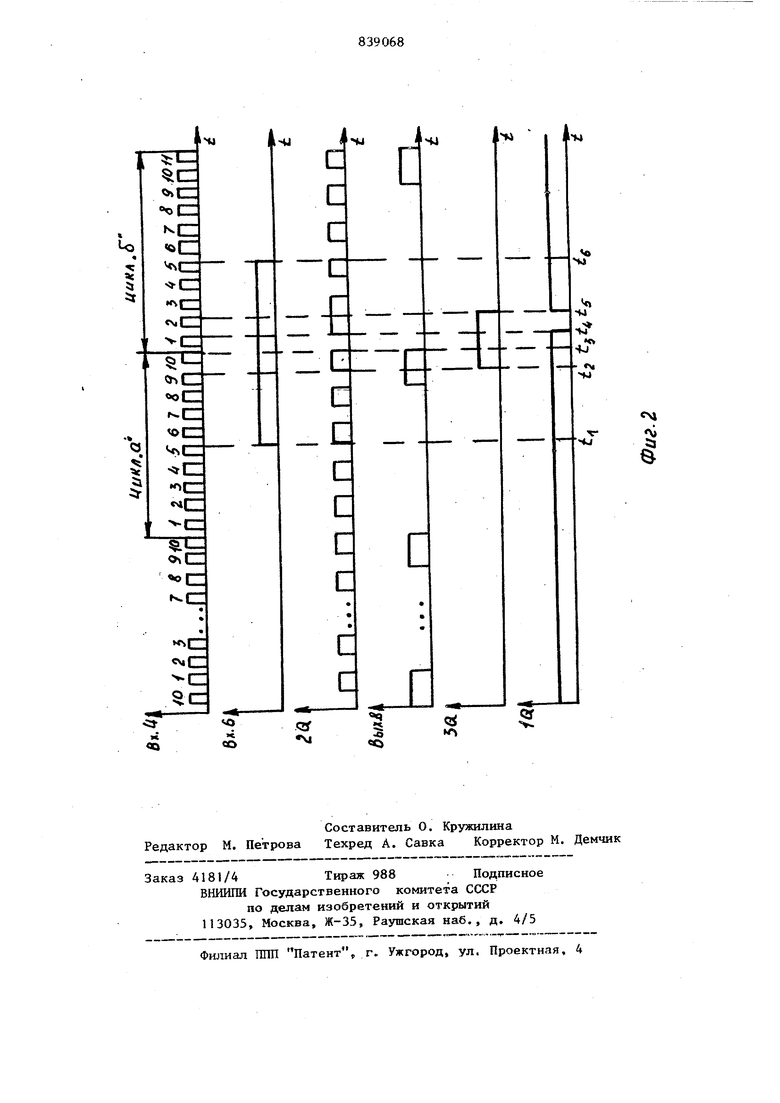

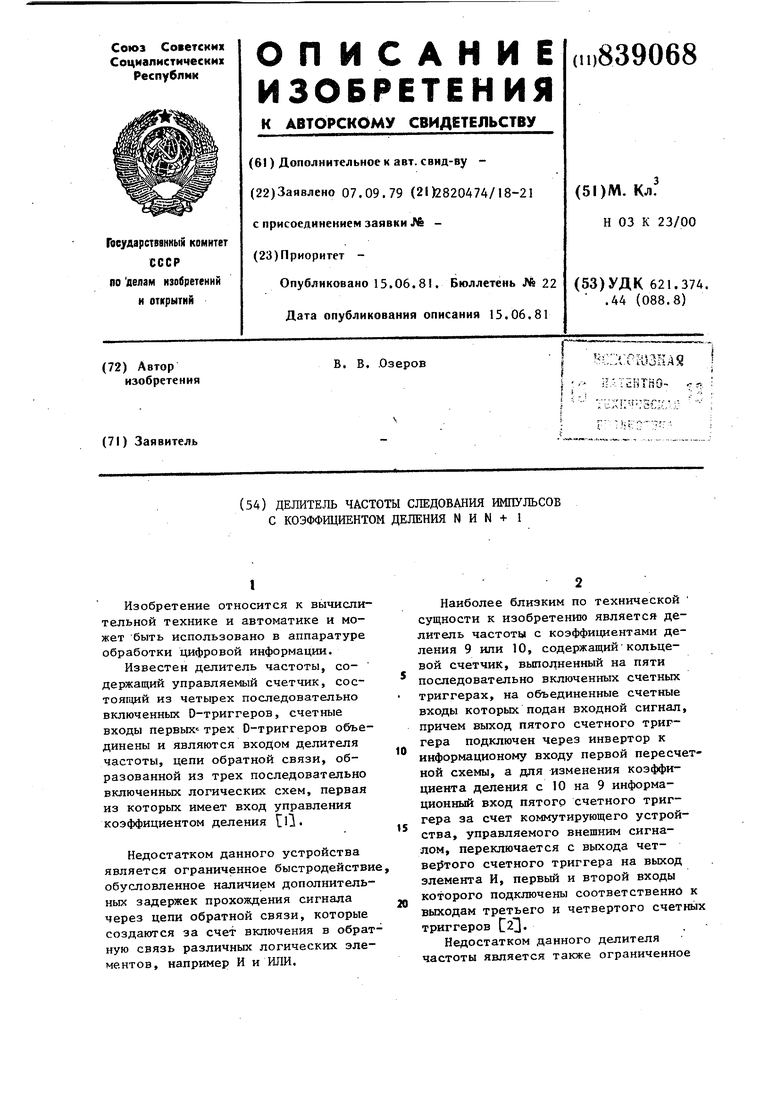

На фиг.1 представлена структурная схема устройства; на фиг.2 - . зо временные диаграммы, поясняющее работу устройства.

Устройство содержит IК-триггеры 1-3, делитель 4 частоты на Ы/2,блок

5совпадения, вьшолненньй в виде 35 элемента И-НЕ, шину 6 управления коэффициентом деления и входную шину 7.

Рассмотрим работу устройства при коэффициентах деления N 10 и 40 N + .

Для получения коэффициента деления N 10 на шину управления

6подается уровень логического нуля.

В промежутке времени t, t О на 45 выходе блока 5 - логическая единица, которая поступает на первый вход триггера 3, триггер 1 заблокирован по первому входу логическим нулем, поступающим с выхода триггера 3 50 (фиг.2,30,). Триггер 3-находится в устойчивом состоянии за счет отсутствия импульсного сигнала на его счетном входе. На прямом выходе триггера 1 поддерживается уровень 55 логической единицы (фиг.1,0), который поступает на первьй вход триггера 2. Последний работает в режиме депения частоты сигнала на два. Сигнал .поделенной частоты поступает на вход делителя 4 на пять.

Общий коэффициент деления устройства равен

N 2«5 10,

Дпя перехода на коэффициент деления необходимо на шину управления 6 коэффициентом деления подать сигнал, соответствующий уровню логической единицы (фиг.2, промежуток времени t t t ).

Для рассматриваемого случая в промежутке времени t. t происходит совпадение логических единиц по всем трем входам блока 5. В момент совпадения на выходе блока 5 появляется логический нуль, который на выходе триггера 3 устанавливает уровен логической единицы, который поступает на первый вход триггера 1. С этого момента времени триггер 1 подготовлен к работе по первому входу в счетном режиме, но еще заблокирован по второму входу.Поэтому в цикле а (фиг.2) коэффициент деления сохраняется равным N 0. В начале нового цикла счета (фиг.2, цикл б) триггер 2 переходит в состояние с логической единицей на инверсном выходе,что дает возможность перейти триггеру 1 в счетный режим.

В момент времени t , т.е. по первому счетному импульсу в цикле 5 , триггер 1 переходит в состояние с логическим нулем на прямом вькоде, а триггер 2 - в состояние с логической единицей на прямом выходе. Но после прихода второго счетного импульса в цикле 5 (фиг.2, t tg)триггер 1 вновь переключается в состояние с логической единицей на прямом выходе и логическим нулем на инверсном выходе. В результате этого происходит переключение триггера 3 в состояние с логическим нулем на выходе, который блокирует триггер 1 по первому входу, поддерживая на его прямом выходе уровень логической единицы. С момента времени t5 в работу включается триггер 2. Начиная с этого момента времени в работе участвуют лишь триггер 2 и делитель 4.

Из работы устройства видно, что в цикле 5 триггер 2 находится подряд в течение двух периодов входного сигнала в состоянии с логической единицей на прямом выходе, А так как. делитель 4 срабатывает лишь от перепадов входных сигналов, то видно, что цикл 5 длиннее цикла О на один период входного сигнала (фиг.2), т.е. коэффициент деления частоты в цикле 5 равен Количество циклов, в течение которы коэффициент деления равен N+1-11, определяется тем, сколько раз произойдет совпадение логических единиц по всем трем входам блока 5, т.е. сколько раз в промежутке времени to-.-trj на шину управления 6 коэффициентом деления подается лог ческая единица. В предлагаемом делителе частоты повышается быстродействие, так как дополнительные задержки настолько малы, что ими можно пренебречь, следовательно, практически устройство задержки не имеет. В устройстве отсутствует многократнее параллельное соединение счетных входов триггеров, это облегчает согласование между собой триггеров и генераторов сигналов на высоких частотах, что также сп собствует повышению быстродействи устройства.

Вьпод

Фиг. Формула изобретения Делитель частоты следования имульсов с коэффициентами деления и N +1, содержащий триггеры, счетные входы первого и второго из которых соединены с входной шиной, прямой выход первого триггера соединен с первым входом второго триггера, и блок совпадения, отличающийся тем, что, с целью повьшеиия быстродействия, в него введен делитель частоты на N/2, выход которого соединен с первым входом блока совпадения, второй вход которого соединен с прямым выходом второго триггера .и входом делителя частоты на N/2, третий вход - с шиной управления, а выход с первым входом третьего триггера, счетный вход которого соединен с инверсным выходом первого триггера, а выход - с первым входом первого триггера, второй вход которого соединен с инверсным, выходом второго триггера. Источники информации, принятые во внимание при экспертизе К каталог фирмь, PLESSU SEMICONDuctors, 1974, с. 215. 2. Патент США № 3456200, кл. 328-48, 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с регулируемым коэффициентом деления | 1982 |

|

SU1051732A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| Делитель частоты следования импульсов с дробным коэффициентом деления | 1983 |

|

SU1162041A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1070694A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1160560A1 |

| Переключаемый делитель частоты | 1984 |

|

SU1197072A1 |

Авторы

Даты

1981-06-15—Публикация

1979-09-07—Подача