(54) СПОСОБ КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПОИСКА ДЕФЕКТОВ В ЦИФРОВЫХ БЛОКАХ | 2003 |

|

RU2255369C1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Способ контроля аналоговых схем | 1979 |

|

SU993176A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для проверки функционирования логических схем | 1980 |

|

SU955072A1 |

| ЛАЗЕРНЫЙ ИМПУЛЬСНЫЙ ДАЛЬНОМЕР | 2014 |

|

RU2551700C1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

Изобретение относится к контрольноизмерительной технике и может быть использовано для обнаружения и указания места потенциально неисправного (потенциально ненадежного, дефектного) та в гт - элементных логических схемах последовательного действия на элемента памяти черескаскадным методом (т.е. имеется доступ только к входу и выходу проверяемой схемы или логической цепи). Известен способ , предназначенный для контроля трехвходовых схем совпадения, который предусматривает подачу на первый вход контролируемой схемы парны импульсов длительностью сГ и сдвигом i If , на второй вход - импульса, задержанного относительно первого из указанной пары на и имеющего длительность - t -ц-L, и на третий вход - импульса длительностью Тj , при котором -Ь+ц. Исправность схемы определяют сравнением длительности выхо ных импульсов с длительностью импупьсов, подаваемых на первый вход схемы D J. Известен также способ обнаружения неисправности в логических схемах, основа1Ь ный на входном воздействии и анализе выходных сигналов, согласно которому контролируемую схему разбивают на участ ки функционирования элементарных логян ческих операторов, а правильность работы элементов, реализующих эти операторы, проверяют подачей на входные полю- сы элемента первого набора (слова) из заданного подмножества и проверкой и 7ГИЧИЯ единичного выходного сигнала, поодачей второго набора (слова) из заданного подмножества и проверкой натпня нулевого выходного сигнала. Таким Об разом, создают логические условия правильности работы контролируемой схемы и анализируют рабочие сигналы, дейст вуюшие в контролируемых цепях. При этом осуществляется допусковая оценка рабочих сигналов, представляющих двоичные зна1чен01 О и TSjf. 3S Однако известные способы, основанные на входном воздействии и анализе выходных сигнапов, не позволяют обнаружить и указать место дефектного элемента в логических схемах последовательного дейст вия на элементах памяти, так как при номинале питающего напряжения д0|)ектны элемент не отличается, в функциональной области от заведомо исправного. Цель изобретения - обнаружение и ука зание места потенциально неисправного элекгента в логических схемах, последовательного действия на элементах памяти. Для достижения поставленной цели согласно способу контроля логических схем, основанному на входном воздействии и анализе выходных сигнал(ж, амплитуду питающего напряжения изменяют от номинального значения до заданного порога функционирования на определенном ин-тервале входного воздействия, причем на вход схемы подают последовательность логических единиц, последовательность импульсов питающего напряжения образую из 2 - 1 импульсов с амплитудой, равной номиналу питающего напряжения, и импульса с амплитудой, равной заданному порогу функционирования, который занимает в последовательности место , где п - количество элементов конт ролируемой схемы , а номер V дефектного элемента определяют по формуле номер такта питающего напряжения, при котором на выходе крнт ролируемой схемы появляется пе вая логическая единица, В результате указанного изменения пи тающего напряжения создаются в определенной послед (Ж ательности логические условия правильности функционирования всех элементов схемы (при номинале Чп и режим, при котором дефектный элемент не срабатывает, а исправный срабатывает (при пороге функционирования Чп ). Это обеспечивает однозначную задержку выходного сигнала в зависимост 6т ноимера дефектного элемента, если в проверяемой цепи дефектным является то лько один элемент. Согласно предлагаемому способу порог функционирования Ип использует ся как обобщенный и доступный для набтодения параметр, который имеет неизвестную или достаточно сложную корреля ционную связь с другими параметрами 0 элемента, труднодоступными для наблюдеЗначение (J. зависящее от запаса надежности дефектного элемента по облаете функционирования, т.е. области, в которой элемент выполняет свою основную функцию, или зоны его работоспособности, задают предварительно. Значеюте L/n определяют экспериментальным путем. Сущность предлагаемого способа за ключается в следующем. Контролируемую п - элементную логическую схему последовательного действия на элементах памяти записывают (например, с помощью программируемого источника питания) последовательностью 2 импульсов напряжения, в которой один импульс имеет амплитуду (( и занимает в последовательности,место с номером 2, а остальные имеют амплитуду Ц (например, при п 4 111И1.1 011111111 и т.д.). Вид поспедовательности может отличаться от принятой, однако во всех вариантах она должна обеспечивать однозначную задержку выходного сигнала в зависимости от номера дефектного элемента, если на вход контролируемой схемы поступает последовательность логических единиц, синхронизированная с.последсюатепьностъю импульсов питающего напряжения. На вход контролируемой схемы подают последовательность логическихедини ц, синхронизирсжанную с последовательностью импульсов питающего напряжения (указанную последовательность может ге нерировать генератор единичных нормали- зованных сигналов, которые используются также в качестве синхронизирующих для программируемого источника питания). Индицируют появление первой логической единицы на выходе контролируемой схемы и устанавливают номер Н соответствующего такта питающего напряже-ния или входного единичного сигнала (например, с помощью счетчика импульсов), затем определяют номер j дефектного элемента по формуле (1). Бели схема контролируется при , то для обнаружения и указания номера j дефектного элемента (1,2 или 3-его) на нее с источника питания подают послед еж а тельное ть импульсов питающего напряжения 11101111, а на вход - последовательность единичных .сигналов с

58407706

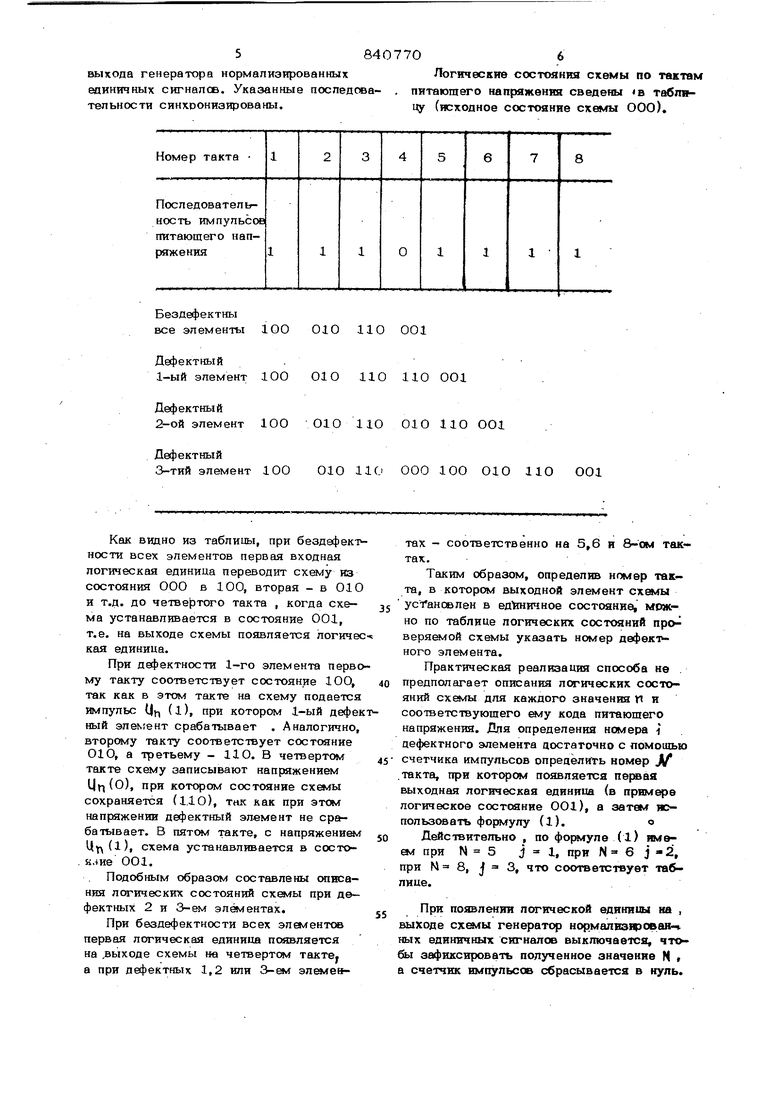

выхода генератора нормализированныхЛогические состояния схемы по тактам

единичных сигналсв. Указанные поспедсжа- , питающего напряжения сведены «в табпительности синхронизированы.цу (исходное состояние схемы ООО).

1ОО 010 110 001

.

100 О1О 110 110 ОО1

100 ОЮНО 01О НО ОО1

100 О1О НО ООО 100 010 110 СО Как видно из таблицы, при бездефект ности всех элементов первая входная логическая единица переводит схему из состояния ООО в 100, вторая - в 010 и т.д. до четве(этого такта , когда схема устанавливается в состояние 001, т.е. на выходе схемы появляется логичэ кая единица. При дефектности 1-го элемента перво му такту соответствует состояние 10О, так как в этом такте на схему подается импульс Un (1), при котором 1-ый дефе ный элемент срабатывает . Аналогично, вторсму такту соответствует состояние О1О, а третьему - НО. В четвертом такте схему записывают напряжением IJj(O), при котором состояние схемы сохраняется (1.10), так как при этом напряжении дефектный элемент не срабатывает. В пятом такте, с напряженик UY(I)« схема устанавливается в состо. клие ОО1. Подобным образом составлены описания логических состояний схемы при дефектных 2 и 3-ем элементах. При бездефектности всех элементе первая логическая единица появляется на .выходе схемы на четвертом такте а при дефектных 1,2 или 3-ем эп&леа тах - соответственно на 5,6 и 8-ом тактах. Таким образом, определив номер такта, в котором выходной элемент схемы усГановлен в едУшичное состояние, можно по таблице логических состояний проверяемой схемы указать номер дефект него элемента. Практическая реализация способа не предполагает описания логических состояний схемы для каждого значения П и соответствующего ему кода питающего напряжения. Для определения номера ) дефектного элемента достаточно с помощью счетчика импульсов опредёли -ь номер Л/ такта, при котором появляется перюая выходная логическая единииа (в примере логическое состояние OOl), а затем использовать формулу (1).о Действительно , по фо|лигуле (l) име ем при N 5 j 1, при N 6 j 2, при N 8, j 3, что соответствует твблиие. При появлении логической единицы на , выходе генератор нормалвзирован-г ных единичных сигналов выключается, что бы зафиксировать полученное значение N , а счетчик импульсов сбрасывается в нуль. 784 Предпагаемый способ поэволявт с выс кой достоверностью обнаружить и покапи зовать дефектный элемент черескаскадным методом. Он может быть испопьэован также дпя аналогичной прсюврки погических цепей последовательного действия на элементах памяти в сложных логических схемах при предварительном их выделении. Кроме того, способ может найти пр менение при прогнозировании отказов « кпасси1)икации однотипнь1х логических схе по порогу функционирования. Формула изобретения 1. Способ контроля логических схем, основанный на входном воздействии и анализе . /выходных сигналов, о т пичаюши йся тем, что, с цепью обнаружения и указания места потенциально неисправного sriavfeHTa в логических схемах последовательного действия на элементах памяти, амплитуду питаюше го напряжения изменяют от номинального значения до заданного порога функционирования на определенном интервале входного воздействия. О 2. Способ йо п. 1, о т л и ч а ю щ и и с я тем,что на вход схемы подаю.т. поспедсюатепьность логических единиц, последовательность импульсов питающего напряжения образуют из 2 - 1 импуп сов с амплитудой, равной номиналу пи тающего напряжения, и импульса с амплитудой, равной заданному порогу функционирования, который занимает в последовательности место ,, где м - количество элементе контролируемой схемы, а номер j дефектного элемента определяют по формуле j-e( N - ) I где N - номер такта питающего напряжения, при котором на выходе контролируемой схемы появляет ся первая логическая единица. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 198409, кл. QOlR 31/28, 1966. 2.Корытная Л. А. Автоматическое обнаружение неисправностей в эпект ронных шфровых машинах. Кибернетическая техника. Киев, Наукова цумка, 1965, -с. 98-99 (прототип).

Авторы

Даты

1981-06-23—Публикация

1978-12-20—Подача