Изобретение относится к области вычислительной техники и может быть использовано в качестве множительноделительного устройства в гибридных вычислительных мгииинах. По основному авт. св. №.674042 известно множительно-делительное устройство содержсцдее реверсивный счетчик, прямой и реверсивный входы которого связаны с соответствующими выходами переключателя, вход которого подключен к выходу элемента И, пе вый, вход которого соединен с выходом тактового генератора, а второй с соответствующим выходом генератора синхроимпульсов, управляющий вход переключателя подключен к выходу ком паратора, выходы разрядов реверсивного счетчика соединены с соответствукяцими входами цифроаналогового пре образователя, аналоговый вход которо го через первый и второй ключи связан соответственно с входами первого сомножителя и делителя, выход цифроаналогового преобразователя свя зан с первым входом компаратора и че рез третий ключ - с входом первого элемента памяти, через четвертый ключ выход первого элемента памяти соединен о аналоговым входом цифроаналогового преобразователя, второй вход компаратора соединен через пятый ключ с входом второго сомножителя,а через шестой ключ - с выходом первого элемента памяти, выход цифроаналогового преобразователя через седьмой ключ связан с входом второго элемента памяти, входы начальной установки реверсивного счетчика являются выми входами устройства, выходы элементов памяти являются ангшоговымн выходами, а выходы реверсивного счетчика являются цифровым выходом устройства, управляющие входы ключей и реверсивного счетчика подключены к соответствующим выходам генератора синхроимпульсов 1. Это устройство позволяет вьшолнить не более двух множительно-делительных операций за 1 цикл, т.е. вычисляХ ХОA-fТ,ТМ V ют функции вида Цель - изобретения - расширение функциональных возможностей устройства за счет обеспечения вычислений функций вида x -xii-- n Y -YI--VW Поставленная цель достигается тем, что в множительно-делительное устройство введены два дополнительные ключа, вправляющие входы которых подсоединены к соответствующим выходам генератора синхроимпульсов, информационные входы объединены и подключены к выходу второго элемента памяти, выход первого дополнительного ключа подключен к аналоговому входу цифроаналогового преобразователя, а выход второго дополнительного ключа подключен ко второму входу компаратора.

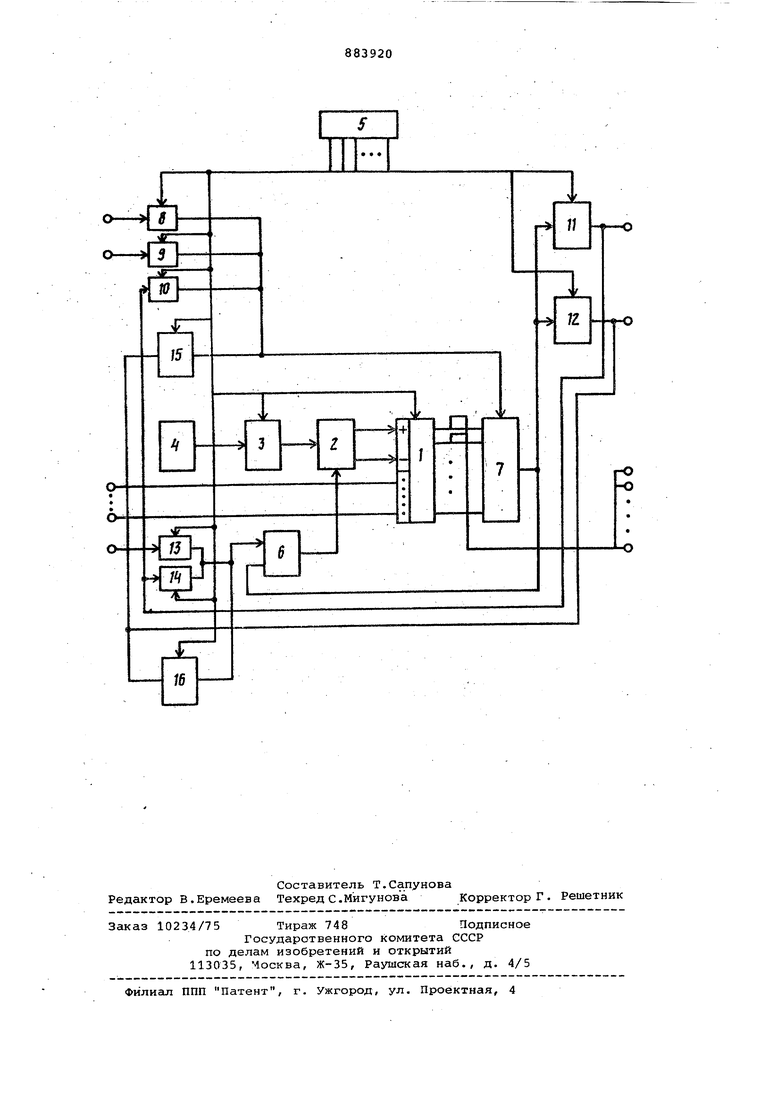

На чертеже представлена блок-схема множительно-делительного устройства

Множительно-делительное устройств содержит реверсивный счетчик 1, прямой и реверсивный входы которого связаны с соответствующими выходами переключателя 2, вход которого подключен к выходу элемента И 3, первый вход которого соединен с выходом тактового генератора 4, а второй вход с соответствующим выходом генератора синхроимпульсов 5, управляющий вход переключателя 2 подключен к выходу компаратора 6, выходы разрядов реверсивного счетчика 1 соединены с соответствующими входами цифроаналогового преобразователя 7 аналоговый вход которого через первый ключ 8 и второй ключ 9 связан соответственно с входом первого сомножителя (делителя) с опорным напряжением, а через первый дополнительный ключ 10 с выходом первого элемента памяти 11 выход цйфроаналогового преобразователя 7 связан с первым входом компаратора бис входс1ми первого и второго элементов памяти 11 и 12. Второй вход компаратора 6 соединен через третий ключ 13 с входом второго сомножителя и через второй дополнительный ключ 14 с выходом первого элемента памяти 11. Входа начальной установки реверсивного счетчика 1 являются цифровыми входами устройства, выходы элементов памяти 11 и 12 являются аналоговыми выходами, а выходы реверсивного счетчика 1 являются цифровым выходом устройства.Сигнальные входа четвертого и пятого ключей 15 и 16 объединены и подсоединены к выходу второго элемента памяти 12, выход четвертого ключа 15 соедниеи с аналоговым входом цифроаналогового преобразователя 7, выход пятого ключа 16 соединен со вторым входом компаратора 6, управляющие входы всех ключей элемейтов памяти и рэверсивного счетчика 1 подключены к соответствующим выходам генератора синхроимпульсов 5.

Множительно-делительное устройство работает следующим образом.

Генератор синхроимпульсов 5 через ключи 8, 9 и 10 и ключ 15 подклочает к аналоговому входу преобразователя 7 в соответствующем порядке Ед входные сигналы сомножителей делимого Xj (делителя У) или промежуточный результат преобразования, хранящийся в одном из элементов в памяти 11 и 12. Через ключи 13, 14 и 16 ко входу компаратора 6 генератор 5 подключает в соответствующем порядке входные сигналы сомножителей делимого X(делителя У) или-промежуточный результат преобразования, хранящийся в одном из элементов памяти 11 и 12.

Рассмотрим работу устройства для случая, когда необходимо получить произведение величины

viii-xV via-Wa-i 2--- r.-xln-xi n, (i

где X-i;,X2j.X3{ - сигнал сомножителей ио первому, второму, третьему входам устройства соответственно.

На вход компаратора 6 подается сигнал первого ссжножителя Х1 на аналоговый вход преобразователя 7 подается Е. На тактовый вход счетчика 1 поступают импульсы и производится цикл преобразований аналогового сигнала Х1 и выходной двоичный код счетчика IN,

Затем подключается сигнал второго сомножителя аналоговому входу преобразователя 7. Результат преобразования

2 MyXVXi,-Xa (2)

заполняется элементом памяти 11.Следующий сомножитель X в цифровом коде заносится через входы начальной установки в реверсивный счетчик l.Ha аналоиовый вход преобразователя 7 подается результат преобразования по формуле (2) с элемента памяти 11. Результат преобразования по формуле

.XVXl. (3)

заносится в элемент памяти 12.

Затем подается следующий сомножитель Х1 на вход компаратора 6, к аналоговому входу преобразователя 7 подключается Е Off. Производится цикл преобразований аналогового сигнала xt/j в выходной двоичный код счетчика 1, пос;ле чего на аналоговый вход преобразователя 7 подключается результат преобразования по формуле (3), хранядейся в элементе памяти 12. Результат преобразования по формуле

z Zj-Xf/i xi -xa -xVf-a (4)

запоминается элементом памяти 11.Затем подается следующий сомножитель т.д. до получения результата lio формуле (1).

Рассмотрим работу устройства для случая, когда необходимо произвести вычисления по формуле

,-Y%--Vlh n (5) Промежуточный результат вычисле НИИ Z хранится в элементе памяти 11. Сомножитель делителя У.2 подается на аналоговый вход преобразователя 7, делимое Z из элемента памяти 11 через ключ 14 подается на вход компаратора б. Резельтаты преобразования по формуле V-% (6) на выходе счетчика 1 преобразуется затем в ангшоговую форму, для чего на аналоговый вход, преобразователя 7 подается Ё через ключ 9. После цикла преобразований кода N в анал говую величину получена на. ёыходе преобразователя 7 результат по форм лё 25 1Еоп который запоминается элементом памяти 12. Затем сигнал второго сомножителя делителя УЗ в цифровом коде через входы начальной установки заносится в реверсивный счетчик 1.Подается на аналоговый вход преобра- зователя 7 Ерпг цифровой код УЗ пре образуется в аналоговую величину и запоминается в элементе памяти 12. Затем делимое Zg из элемента памяти 12 через ключ 16 подается на вход компаратора б, а делитель УЪ из элемента памяти 11 через ключ 10 подается на ангшоговый вход преобразователя 7. Результат деления 4 V «.. преобразуется зачтем в аналоговую форм для чего на аналоговый вход преобра зователя 7 подключается Ер и аналоговый результат запоминается в элементе памяти 11. Спедукций сомножитель делителя У поступает через ключ 8 на ангшо говый вход преобразователя 7, .проме жуточный результат предцдуп его преобразования по формуле (8) через ключ 13 поступает на вход компаратора б , после преобразования по формулеN -Ш 2i (3) цифровой код Н счетчика 1 преобразуется в аналоговую величину и ..запоминается элементом памяти 12. Затем подаемся следующий сомножитель делителя мЭ и т.д. до получения конечного р гзультата по формуле (5). Таким образом, множмтельно-деЛительное устройство позволяет выполнять умножение и деление без ограничения количества сомножителей и делителей. формула изобретения Множительно-делительное устррйство по авт.св. W 674042 о т л и чающееся тем, что, с целью расширения фушсциональных воз14ожностей за счет обеспечения вычислений j ..XiXiXn функций вида уЛо--Хп. в него введены два дополнительные ключа, управлякнцие входы которых подключены к с Х тветствуп14Им выходам 1 еиератора синхроимпульсов, информационные входы объединены и подк1вочены к выходу второго элемента пгмяти, выход первого дополнительного ктвоча подключен к аналоговому входу цифроаналогового преобразователя, выход второго дополнительного ключа подключен ко второму входу ксмшаратора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 674042, кл. Q 06Q 7/16, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Множительно-делительное устройство | 1976 |

|

SU674042A1 |

| АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2121712C1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

| Множительно-делительное устройство | 1981 |

|

SU993278A2 |

| Множительное устройство | 1980 |

|

SU900293A1 |

| Вычислительное устройство | 1986 |

|

SU1320819A1 |

| Множительно-делительное устройство | 1979 |

|

SU1023344A1 |

| Множительно-делительное устройство | 1977 |

|

SU788128A1 |

Авторы

Даты

1981-11-23—Публикация

1980-02-25—Подача