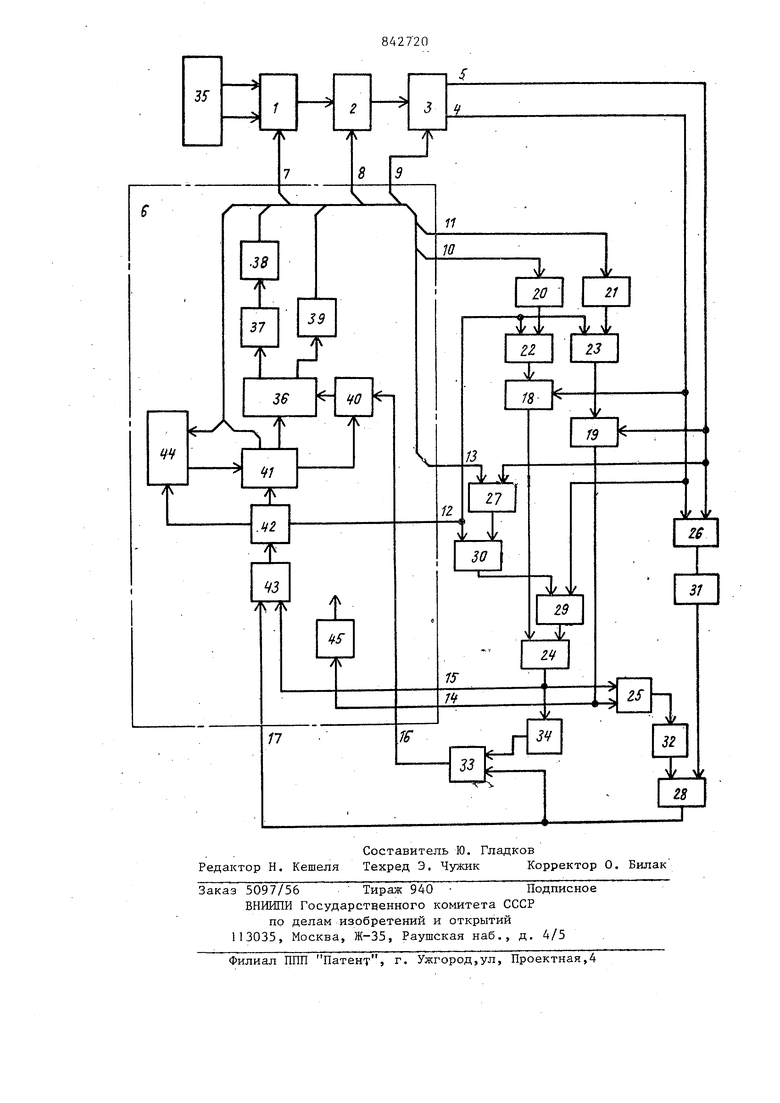

(54) УСТРОЙСТВО для КОНТРОЛЯ ПАРАМЕТРОВ если при ti циклах контроля он признан тактовым не менее m раз. Тол ко после этого происходит переход к контролю следующего параметра (Д|. Однако в случае неисправности для признания объекта по данному параметру : Неисправен необходимо выполнить все И| циклов контроля. Получаема информация избыточна для классификации состояния объекта и требует неоправданных затрат времени и расхода ресурсов. Цель изобретения - повьшение достоверности контроля объектов и увеличение быстродействия устройства. Ч- . Поставленная цель достигается тем что устройство содержит первый и вто рой блоки ключей,, первый и второй ре гистры, третий счетчик блок памяти, первьш, второй, третий и четвертый э ментЫ ИЛИ, первый и второй элемен ы И триггер, элемент НЕ и элемент задержк второй выход блока управления через последовательно соединенные первый ре гистр и первый блок ключей подключен ко второму входу первого счётчика,а третий выход через последовательно со диненные второй регистр и второй блок ключей - ко второму входу второго сче чика, выход которого непосредственно,а выход первого счетчика через первый элемент ИЛИ соединен, с первым входо блока управления и вторым входом бл ка управления, входом третьего счетчика, вторым входом второго элемента ИЛИ соответственно, выход второго элемента ИЛИ через элемент НЕ подключен к первому ВХОДУ первого элемента И, выход которого соединен через блок памяти с третьим и непосред ственно с четвертым входами блока управления, второй вход блока памяти подключен -к выходу третьего счетчика первый и второй выходы вычислителя соединены с .соответствующими входами третьего элемента ИЛИ, а также непосредственно и через последовательно соединенные четвертый элемент ИЛИ и триггер с соответствующими входами второго элемента И, выход которого подключен ко второ му входу первого элемента ИЛИ, второй вход триггера соединен с четвертым выходом блока- управления и вторыми входами первого и 1второго блоков ключей, пятый выход блока управления подключен ко второму входу четверт ого элемента ИЛИ, БЫХОД- треть 0 I го элемента ИЛИ через элемент задержсоедйнен со вторым входом первого ки элемента И. На чертеже представлена блок-схема устройства. Устройство содержит коммутатор 1, блок 2 преобразователей, вычислитель 3 с первым выходом 4 сигнала Исправно и вторым выходом 5 сигнала Неисправно, блок управления 6 с первыми 7,8 и 9, а также вторым 10, третьим П, четвертым 12, пятым 13 выходами команд управления и с . первым 14, вторым 15, третьим 16 и. четвертым 17 входами соответственно команд Неисправен и Исправен, адреса повторяемой проверки команды Повторение первый 18 и второй 19 счетчики, выполненные в виде счетчика-регистра, первый 20 и второй 2J регистры, первый 22 и второй 23 блоки ключей, первый 24, второй 25, третий 26 и четвертый 27 элементы ИЛИ, первый 28 и второй 29 элементы И, триггер 30, элемент 31 задержки, элемент НЕ 32, блок 33 памяти, третий счетчик 34, выполненный в виде счетчика-регистра, и объект 35 контроля. В состав блока 6 управления входят узел 36 команд, выполненный в виде постоянной памяти, регистр 37 адреса, дешифратор 38 .адреса,.регистр 39 числа, счетчик 40 команд, выполненный в виде счетчика-регистра, зел 41 управления, формирователь 42,. последовательности импульсов, элемент ИЛИ 43, узел 44 задержек времени, формирователь 45 сброса. Устройство работает следующим образом. Программа контроля заложена в . узел 36 блока 6 и выполняется по- следовательно отдельными проверками в автоматическом режиме. Команды программы контроля считываются с узла 36 в соответствии с содержимым счетчика 40. Считывание очередной команды, формирование сигналов сопровождения (с.инхронизации) и увеличение содержимого счетчика 40 на единицу (с целью подготовки чтения . очередной команды из узла 3 осуществляется узлом 41. Работа этого узла активизируется сигналом с формирователя 42 и останавливается сигналом с выхода узла 44, с помощью которого организуются необходимые временные задержки между командами. Причем запуск в работу узла 41 выполняется с другого выхода узла 44 через элемент ИЛИ 43, Формирователь 42 вначале формирует сигнал обнуления узла 44 и сигнал на выходе 12 блока 6, а затем активизирует, работу узла 41. Временный сдвиг между сигналами на выходах формирователя 42 обеспечивает нормальную работу устройства. Считываемая команда состоит из адресной части, поступающей на регистр 39, Информация с выходов 7-13 блока . 6 передается в блоки устройства совместно с сигналами сопровождения в соответствии .с адресом, сфор мированным дешифратором 38. Выходы объекта 35 подключаются через коммутатор 1 к блоку 2. Резуль тат преобразования поступает на вход вычислителя 3,куда предварительно заносятся с блока 6 по выходу 9 необ ходимые исходные данные и значения допусков контролируемых параметров. .основании.логической оценки появляет ся сигнал Исправно на выходе 4 блока 3, -если контролируемый парам ет находится н пределах допуска, или сигнал Неисправно на выходе 5 блок 3, если параметр оказывается за пределами допуска. Сигнал с выхода 4 пос пает на счетный вход счетчика 18, первый вход элемента ИЛИ 26 и первый вход элемента И 29, а сигнал с выхода 5 - на второй вход элемента ИЛИ 2 и первый вход четвертого элемента ИЛИ 27, Перед началом контроля группы параметров или одного параметра с вы ходов 10 и 11 блока 6 заносятся соот ветственно в регистры 20 и 21 коды, соответствующие числу повторения цик лов контроля по результатам Исправн и Неисправно Прежде чем начать очередную проверку с регистров 20 и 21 информация переписывается сигналом С выхода 12 .блока 6 через блоки 22 и 23 в счетчики 18 и 19,, а триггер 30 устайавливается в исходное/состояние,Тог да, если первый, цикл .контроля дае.т результат Исправно, сигнал с выход 4 блока 3 через элементы И 29 и ИЛИ 24 формирует команду Исправен, которая поступает на вход 15 блока 6, свидетельствуя о исправном состоянии объекта по данному параметру. Одновременно сигнал с элемента ИЛИ 1А / поступает на счетный вход счетчика . 34, увеличивая номер проверки на единицу. Команда Исправен с входа 15 через элемент ИЛИ 43 поступает на формирователь 42 начинается очередной цикл работы блока. 6. При получении первого результата Исправно сигнал с выхода 5 блока 3 увеличивает содержимое счетчика 19 на единицу, через элемент ИЛИ 27 переключает триггер 30, запрещая прохождение сигнала Исправно через элемент И 29, -и через элементы ИЛИ 26, задержки 31 и И 28 формирует команду Повторение, если на входе эпемента НЕ 32 отсутствует сигнал с эле мента ИЛИ 25. Элемент 31 обеспечивает развязку во времени моментов формирования команды Пвоторение и сигнала на выходе элемента ИЖ 25 сигнала запрещения повторения. Команда Повторение поступает на вход блока 33 памяти и считывает в соотвествии с содержимым счетчика 34 начальный адрес.проверки через вход 16 блока 6 в счетчик 44. Одновременно команда Повторение поступает на вход 17 блока 6 и через элемент ИЛИ 43 на формирователь 42 и начинается повторный цикл контроля параметра. Сигнал на выходе элемента ИЛИ 25 формируется в том случае,когда в результате повторения циклов контроля параметра на его входах появляются либо сигнал с выхода переполнения счетчика 18 через элемент ИЛИ 24 (команда Исправен, либо сигнал с выхода переполнения счетчика 19 (команда Неисправен , т-е. когда выполнено заданное число повторений и счетчики переполняются. Команда Неисправен поступает также на вход . 14 блока 6 и затем на вход формйрователя 45., и процесс контроля прекращается, элементы ус тройства устанавливаются в исходное состояние, в счет чике 34 фиксируется номер проверки, в которой получен результат о,не- исправности объекта. Если в проверке заключение о исправном состоянии объекта должйо быть сделано только по совпадающим результатам Исправлено, то сигналом с выхода 13 блока 6 через второй вход; элемента ИЛИ 27 переключается триггер 30 в положение, запрещающее прохождение через элемент И 29 сигнала Исправно с выхода 4 блока 3. Оче;редной сигнал Исправно увеличивает содержимое счетчика 18 на единицу и, поступая на вход элемента ИЛИ 26, формирует команду Повторение. Сигнал переполнения счетчик 18 свидетельствует об окончании циклов контроля объекта по данному параметру с результатом Исправен. В общем случае репение о состоянии объекта по данному параметру принимается по выходу того счетчика, который раньше вырабатывает сигнал пе реполнения . В предлагаемом устройстве обеспечивается повышение достоверности контроля объектов и универсальность за счет возможности исполнения раличных условий многократного .контро ля параметра при наименьших затратах среднего времени контроля. Формула изобретения Устройство для контроля параметро содержащее последовательно соединенные коммутатор, блок преобразователе и вычислитель, а также блок управления, первые выходы которого соответственно подключены к первому вход коммутатора и ко вторьм входам блока преобразователей и вычис 1ителя, первый выход которого соединен с первым входом первого, счетчика, а второй с первьт входом второго счетчика, о личающееся тем, чтЪ, с цел повьшения достоверности контроля, устройство содержит первый и второй блоки ключей, первый и второй регист ры, третий счетчик, блок памяти, пер вый, второй, третий и четвертый элементы ИЛИ, первый и второй элементы И, триггер, элемент НЕ и элемент задержки, второй выход блока управления через последовательно соединенны перйый регистр и первый блок ключей подключен ко второму входу первого счетчика, а третий вход через, гтосле08довательпо -соединенные второй регистр и второй блок ключей - ко второму входу второго счетчика, выход кото- рого непосредственно, а выход первого счетчика через первый элемент ИЛИ соединены с первым входом второго элемента ИЛИ, первым входом блока управления и вторым входом блока управления, входом третьего счетчика, вторым входом второго элемента ИЛИ соответственно, выход второго элемента ИЛИ через элемент НЕ подключен к первому входу первого элемента И, выход которого соединен через блок памяти с третьим и посредственно с четвертым входами блока управления, второй вход блока памяти подключен к выходу третьего счетчика, первый и второй выходы вычислителя соединены с соответствующими входами третьего элемента ИЛИ, а также непосредственно и через последовательно с&едйненные четвертый элемент ИЛИ и триггер с соответствующими входами второго элемента И, выход которого подключен ко второму входу первого элемента ИЛИ, второй вход триггера соединен с четвертым выходом блока . управления и вторыми входами первого и второго блоков ключей, пятый выход блока управления подключен ко второму входу четвертого элемента ИЛИ, выход третьего элемента ИЛИ через элемент задержки соединен со вторым входом первого элемента И. Источники информации, принятые во внимание при экспертизе 1 . Артеменко Е. А., Мирзабеков. А.А. Обеспечение высокой эффективности работы дискретных АСК посредством алгоритмических мероприятий. Сб. Техническая диагностика, М., Наука, 1972. 2.Патент Франции № 2232255, кл. Я 01 Д 31/28, опублик. 1975. 3.Патент CIUA № 3681578, кл. 235-153, опублик. 1972. 4.Авторское свидетелгчггво № 418833, кл. С 05 В 23/02, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля | 1984 |

|

SU1200250A1 |

| Устройство для контроля блокапАМяТи | 1979 |

|

SU796916A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ С ОБЪЕКТОМ | 2003 |

|

RU2250491C2 |

| Устройство для связи объектов контроля с системой контроля | 1980 |

|

SU896597A1 |

| Многоканальное устройство для включения резервных радиостанций | 1991 |

|

SU1823139A1 |

| Ограничитель вибраций газотурбинного двигателя | 1987 |

|

SU1537856A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для контроля электрических цепей | 1985 |

|

SU1357883A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1406640A1 |

| Устройство для контроля дискретного канала связи | 1983 |

|

SU1133677A1 |

Авторы

Даты

1981-06-30—Публикация

1979-02-12—Подача