1

Изобретение относится к запоминающим устройствам.

Известно yctpc cTBO для контроля блока памяти, которое содержит счетчик, схему индикации, схемы свяаи по количеству адресных формирователей запоминающего блсжа, регистр сдвига lj.

Указанное устройство не формирует сигнал неисправности в случаях, если возбуждается один, ко не выбранный адресный формирователь, или возбужцаются пять, девять и т.д. адресных формир фателей.

Наиболее близким к предлагаемому является устройство, содержащее два счетчика, триггер, коммутатор, регистр сдвига и схему сравнения, подключенные к блоку управления {2.

Недостаток этого устройства - нввкая достоверность контроля вследствие того, что не формируется сигнал неисправности в случаях, если возбуждается оаив, ио не выбранный адресный формирователь, или возбуждается пять, девять и т.д. адресных формирователей. Кроме того, уст ройство не позволяет провести лсясализадию неисправностей.

Цель изобретения - повышение достоверности контроля и быстродействия уст рсЛства и обеспечение диагностики неисправностей.

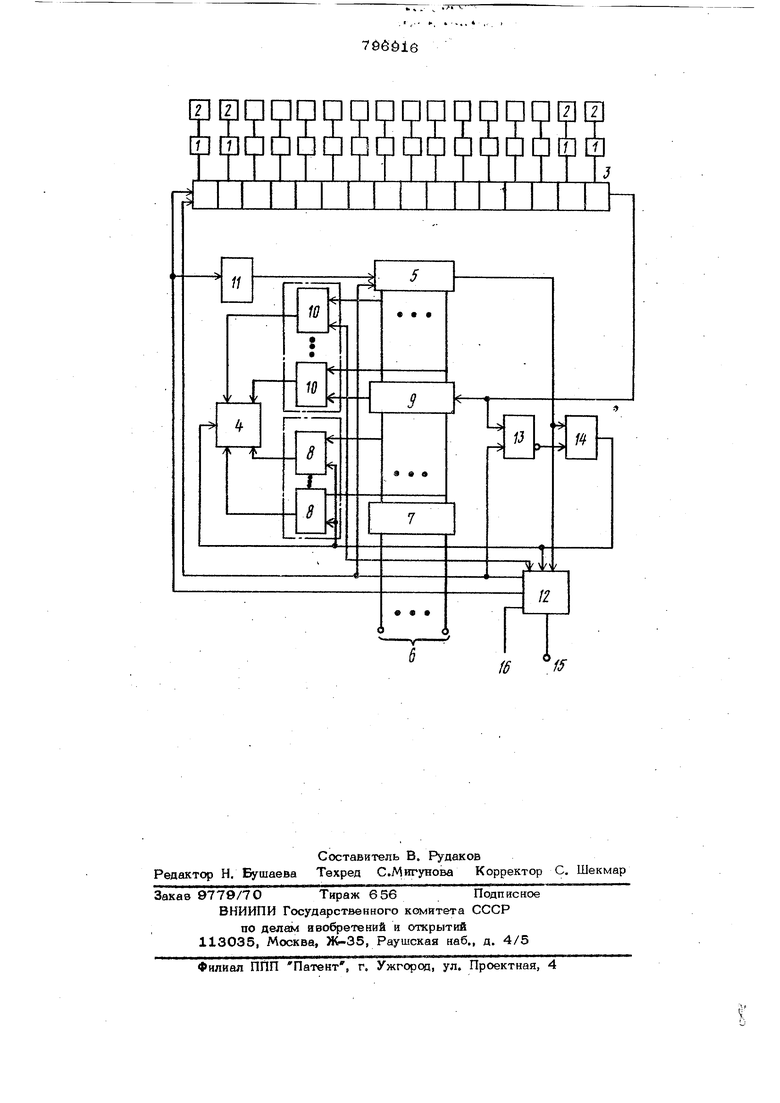

Поставленная цель достигается тем, что в устройство для контроля блока памяти, содержащее блок управления, счед чик, триггер, регистр сдвига и схему сравнения, причем одни из входов регистра сдвига являются информационными вхоцами устройства, другие входы подключены соответственно к первому и выходам блока управления, выход регистра сдвига соединен с одним на входов схемы сравнения, один из выходов и первый вход счетчика подключены соответст венко к первому входу и второму выходу блока управления, введены регистр, элемент И, блок индикации, элемент задержки и две группы элементов И, причем другие входы схемы сравнения подключены соответственно к выходам регистра, другим выходам счетчика и первым входам элементов И групп, выходы элемента И и схемы сравнения соединены соответственно со вторыми входами элементов И первой и второй групп, входы триггера подключены соответственно к выходу регисгра сдвига и второму выходу блока управления, входы элемента И соединены с одним из выходов счетчика и выходом триггера, выход схемы сравнения подключен ко второму входу блока управления, третий вход которого соединен с выходом элемента И, вход элемента задержки под ключен к первому выходу блока управления, а выход - ко второму входу счетчика, выходы элементов И соединены со входами блока индикации, а входы регистра являются адресными входами устройства. На чертеже представлена структурная схема устройства для контроля блока памяти. Устройство через элементы 1 связи подключается к соответствующим адресным формирователям 2 контролируемого блока памяти. Устройство содержит регистр 3 сдвига, блок 4 индикации, сче-рчйк 5, предназначенный для определения двоичного адреса включенного адресного формирователя 2 и формирования сигнала оковчання цикла проверки, адресные шины 6, являющиеся адресными входами устройства, регистр 7, первую группу влементов И 8, схему .9 сравнения, вторую группу элементов И 10, элемент 11 эедержкя,бл(ж 12 управления, триггер 13, который предназначен для образовавнйя сигнала невключения адресных формирователей 2, элемент И 14, шину 15 сянхроннаацив, шнну 16 результата проверки. Счетчик 5 должен иметь К OSfa разрядов, где п - число ячеек контролируемой памяти. Один вз входов регистра 3 являются информационными входами устройства, другие вхспы подключены соответственно к первому и второму выходам блока 12. Выход регистра 3 соединен с одним ив входов схемы 9 сравнения. из выхо дов и первый вход счетчика 5 подключены соответственно к первому входу н вто рому выходу блока 12. Другие входы схемы 9 сравнения подключены соответ ственно к выходам регистра 7, другим выходам счетчика 5, первым входам оле; ментов И 8 н 10. Выходы элемента И 1 ,л схемы 9 сравнения соединены соответственно со вторыми входами элемен- 7 64 OE И 8 И 10. Входы триггера 13 подлючены соответственно к выходу регистра и второму выходу блока 12. Входы лемента И 14 соединены с одним из выодов счетчика 5 и выходом триггера 13. Выход схемы 9 сравнения подключён ко второму выходу блсжа 12, третий вход KOTOporo соединен с выходом элемента И 14. Вход элемента 11 задержки подлючен к первому выходу блсжа 12, а выход - ко второму входу счетчика 5. Выходы элементов И 8, 10 и 14 соединены со входами блока 4 индикации, а входы регистра 7 - с шинами 6. Устройство работает следующим образом. В момент обращения к блоку памяти (на чертеже не приведен) по некоторому адресу с каждого адресного формирователя 2 через элемент 1 связи снимается сигнал, указывающий состояние формирователя - включен он или .рыключен. Эти сигналы одновременно подаются на входы регистра 3 сдвига При этом принимается, что включенный формирователь 2 записывает в регистр 3 сдвига, а невключенный - О. В зависимости от технического состояния блока памяти (исправен он или неисправен) в регистре 3 сдвига могут быть записаны одна единица, положение которой определяется двоичным адресом регистра 7, одна единица, положение которой не соответствует двоичному адресу регистра 7, более одной единицы или все нули. Первое состояние соответствует исправной работе блсжа памяти, остальные состояния - неисправной работе. Для определения действительного состояния блока памяти в регистр 7 по щинам 6 записывается . .двоичный код адреса и на шину 15 си.нхронйзации блока 12 упра&ления поступает сигнал разрешения прсьверки. Блсж 12 управления устанавливает в начальное состояние триггер 13, . счетчик 5, регистр 3 сдвига. Затем с блока 12 управления поступает тактовая частота на регистр 3 сдвига и через элемент 11 задержки на счетчик 5. Информация из регистра 3 с тактовой частотой поступает на вход схемы 9 сравнения. При поступлении единичного сигнала из регистра 3 сдвига на тактовый вход.схемы 9 сравнения происходит сравнение двоичного кода адреса, подаваемого из регистра 7, и двоичного кода включенного адресного формирователя 2 из счетчику 5. При несовпадении кодов схема 9 сравнения вырабатывает единичный

сигнал неисправности, который поступает на блсж 12 управления и элементы И 10 Двоичный адрес включенного адресного формирователя 2 поступает через элементы И 10 на блок 4 индикации и тем самым осуществляется локализация неправильно включенных адресных формиро вателей 2.

Если в регистре 3 сдвига записаны только нули, то триггер 13 останется в нулевом состоянии, и после сжончания цикла проверки счетчик 5 вырабатывает импульс переполнения, который поступает на блсж 12 управления и элемент И 14. Сигнал отсутствия включенного

адресного формирователя 2 поступает через элемент И 14 на элементы И 8 и на блсж 4 индикации. Двоичный код из регистра 7 через элементы И 8 поступает на блок 4 индика-ции и тем самым проводится локализация невключенного адресного формирователя 2.

Наличие блока 12 управления позвс ляет вести проверку с тактовой частотой определяемой лишь элементной базой

устройства контроля, и тем самым позволяет сократить время цикла проварки. Кроме того, блок 12 управления при наличии сигнала неисправности вырабатывает сигнал повторения цикла проверки, тем-самым исключая сигнал неисправности, обусловленный сбоем устройства контроля или блока памяти. После окончания второго цикла проверки блок 12 управледия вырабатывает на шине 16

сигнал fpaзpeшeния записи следующего адреса в регистр 7 (при исправной работе) или вырабатывает сигнал прерывания проверки (при повторном обнаружении неисправности).

Таким , описанное устройство для контроля блока памяти обнаруживает и локализует одиночные и кратные неисправности схем управления блока памяти, что позволяет повысить достоверность контроля и сократить время поиска неисправного элемента.

Формула изобретения

Устройство для KOHipcmH блска памят содержащее блок управления, счетчик, триггер, регистр сдвига и схему сравнения, причем одни из входов регистра сдвига являются информационными входами устройства, другие входы подключсены соответственно к первсяиу и второму выходам блока управления, выход регистра сдвига соединен с одним из входов схемы сравнения, один из выходов и первый вход счетчика подключены соответственно к первому входу и второму выходу блока управления, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля и быстродействия устройства оно содержит регистр, элемент И, блсж ивдикации, элемент задержки и две группы элементов И, причем другие входы схемы сравнения подключены соответственно к выходам регистра, другим выходам счетчика и первым входам элементов И групп:. выходы элемента И и схемы сравнения соединены соответственно со вторыми входами элементов И первой и , вторсАгрупп, входы триггера подключены сосу ветственно к выхсау регистра сдвига и второму выходу блсжа управления, входы элемента И соединены с одним иа выходов счетчика и выходом триггера, выход схемы сравнения праключен ко вторсыу входу блока управления третий вход которого соединен с выходом элемента И, вход элемента задержки подключен к перовому выходу блока управления, а выход ко вторсму входу счетчика, выходы элементов И соединены со входами блока индикации. Входы регистра являются адреными входами устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 419984, кл. Q 11 С 29/00, 1972.

2.Авторское свидетельство СССР по заявке № 2722147/18-24,

кл. q 11 С 29/00,26.01.79 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1985 |

|

SU1283769A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Устройство для контроля систем управления | 1979 |

|

SU789977A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1348912A1 |

Авторы

Даты

1981-01-15—Публикация

1979-02-15—Подача