0 05

д;

о

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств с тестовым самоконтролем.

Це. п, изобретения - упрощение уст- jiofic гн;1.

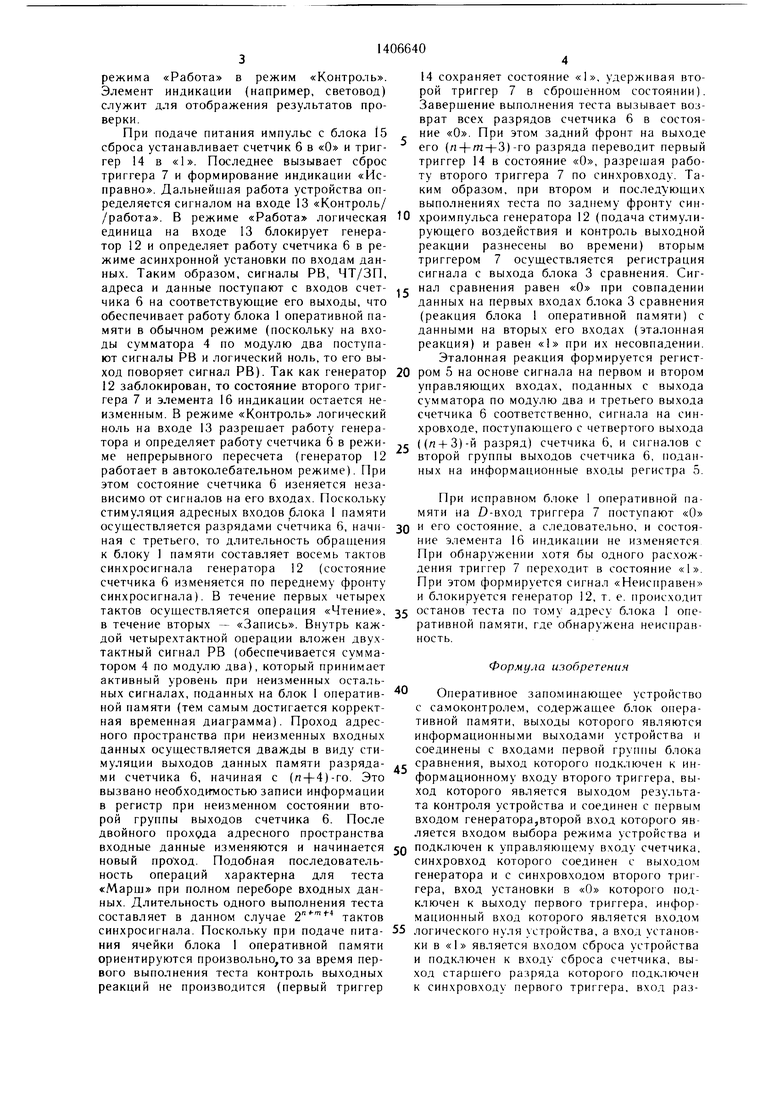

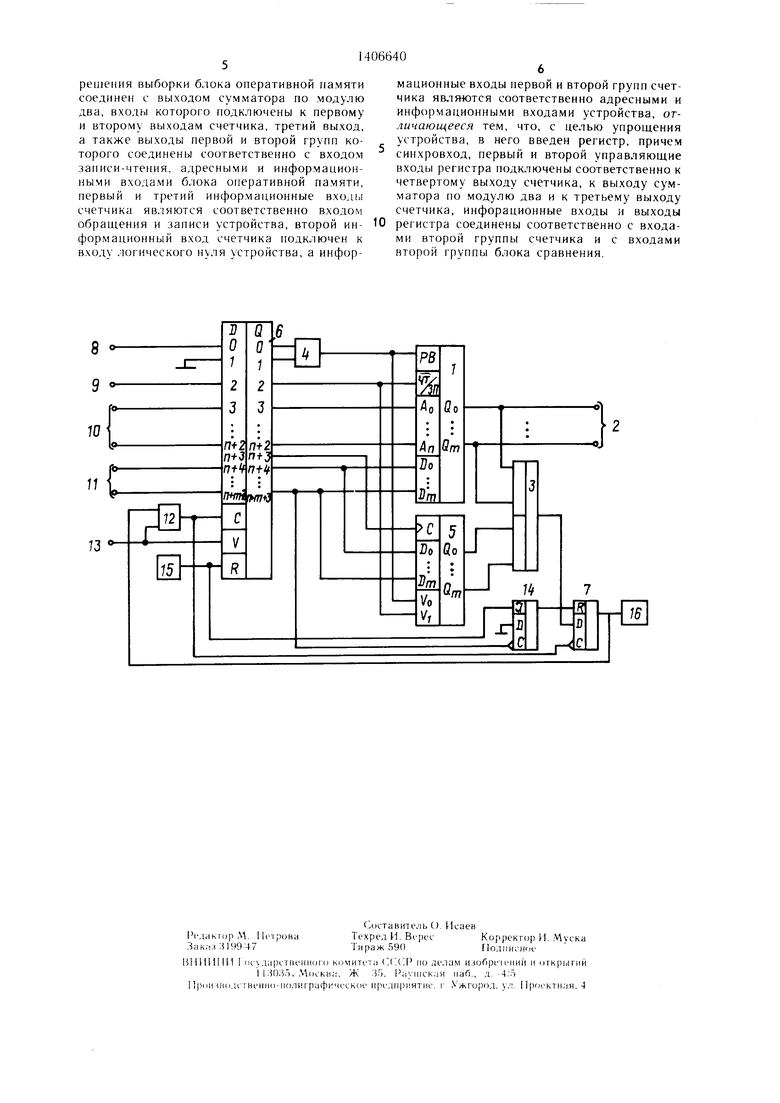

На чертеже представлена схема оперативного запоминающего устройства с самоконтролем.

Устройство содержит блок 1 оперативной памяти е.мкостью Л слов по М разрядов с информационными выходами 2, блок 3 сравнения, сумматор 4 по модулю два, регистр 5, счетчик 6, второй триггер 7, вход 8 обращения устройства, вход 9 записи устройства, адресные входы 10 устройства, входы 11 данных устройства, генератор 12, вход 13 выбора режима, первый триггер 14. Устройство содержит также блок 15 сброса и элемент 16 индикации.

Устройство работает следующи.м образом.

Известно, что алгоритм теста «Mapni д;1я оперативного запоминаюн1его устройства (ОЗУ) с организацией /V X 1 заключается в двух проходах адресного пространства ОЗУ. При это.м в перво.м проходе по каждому адресу выполняется операция «Чтение 1, «Запись О, а при втором проходе «Чтение О, «Запись 1.

При многоразрядном слове данных (.) и стиму.чяции входов данных при проверке последовательными разряда.ми счетчика тест состоит из 2-2 проходов адресов, причем картина здесь аналогична, за исключением того, что для разрядов D...D имеет место избыточность, заключающаяся в до- по.чнительных операциях «Чтение О, «Запись О и «Чтение 1, «Запись 1 но всех не первых проходах адресов после смены входных данных на разряде.

Информация во время разретиений операции «Чтение на любом выходе данных исправного ОЗУ в текуще.м проходе адресов очевидно соответствует информации, записанной в ОЗУ во время выполнения предыду- niero прохода, т. е. во время операции «Чтение должно соблюдаться следующее соотношение: DBNV (/))вч (/ - 1), где в качестве кванта времени взят один проход адресов, /-разряд данных ((0.../М - I ). Таким образом, для формирования эталонной считываемой информации из ОЗУ в данном проходе адресов достаточно зафиксировать информацию, содержавшуюся на информационных входах оперативной намяти в предыдущем проходе. 1рактически стандартной в настояп1ее время является реализация ОЗУ (БИС ОЗУ) такой таблицы истинности, когда информация, хранимая в ОЗУ, передается на выход лишь во время разрещен- Hoii операции «Чтение (при наличии активного уровня сигнала РВ), все остальное время выходы ОЗУ находятся в третьем (Z) состоянии.

0

Следовательно, состояние выходов исправного ОЗУ при контроле по описанному алгоритму теста «Марш в любой момент времени отражает однозначная функция Овых(/)/(Овх (/-1), РВ, ЧТ/ЗП) ( -М - I). В запоминающем устройстве она реализуется с помощью регистра с входами управления (Vo, Vi), обеспечивающими выдачу информации, хранимой в регистре, на его выходы только при подаче на них оп0 ределенных активных уровней, а также перевод выходов регистра в третье (Z) состояние при наличии хотя бы на одном из данных управляющих входов неактивного уровня.

Примером регистра с описанными функ циями может служить регистр К155ЙР15. Для согласования активных уровней на его управляющих входах могут быть дополнительно использованы инверторы. Для записи информации в регистр 5 при неизменном состоянии второй группы выходов счетчика 6 введен дополнительный (л-|-3)-й разряд счетчика между первой и второй его группами. Это ведет к увеличению продолжительности теста в два раза. При этом и для млад- inero разряда данных имеются дополнитель5 ные проходы, т. е. выполняются следующие операции: «Чтение 1, «Запись О, «Чтение О, «Запись О, «Чтение О, «Запись 1, «Чтение 1, «Запись 1.

Счетчик 6 используется в двух режимах.

0 В режиме асинхронной установки по входам данных (режим «Работа) счетчик 6 -- буфер магистральных сигналов системы. Если блок 1 оперативной памяти построен на БИС ОЗУ с малыми входными токами, то счетчик 6 заменяет буфе()ные усилители. При

5 необходимости сигналы со счетчика 6 подаются на блок I памяти через усилители. В режиме «Счет (режи.м «Контроль) счетчика 6 - генератор тестовых воздействий для блока 1 памяти. Второй триггер 7 служит для регистрации результата сравнения от блока 3 сравнения в каждом такте синхронизации генератора 12. Вход сброса R второго триггера 7 соединен с выходом первого триггера 14. Генератор 12 обеспечивает синхроимпульсы для сетчика 6 и триггера 7 в

5 режиме «Контроль. Первый триггер 14 служит для блокировки работы второго триггера 7 при первом выполнении теста. Это связано с тем, что при подаче питания опе- )ативная память ориентируется произвольно и независимо от начальной установки сти0 мулирующего счетчика может иметь на выходе «неверную реакцию, а после первого выполнения теста все ячейки памяти устанавливаются однозначно. Вход данных триггера 14 соединен с общей щиной устройства, а его синхровход - с выходом пос леднего разряда счетчика 6. Блок 15 сброса (например,/ 5-цепь) обеспечивает сигналы начальной установки для счетчика 6 и триггера 14 при переводе устройства из

0

режима «Работа в режим «Контроль. Элемент индикации (например, световод) служит для отображения результатов проверки.

При подаче питания импульс с блока 15 сброса устанавливает счетчик 6 в «О и триггер 14 в «1. Последнее вызывает сброс триггера 7 и формирование индикации «Исправно. Дальнейшая работа устройства определяется сигналом на входе 13 «Контроль/

14 сохраняет состояние «1, удерживая второй триггер 7 в сброшенном состоянии). Завершение выполнения теста вызьз1вает возврат всех разрядов счетчика 6 в состояние «О. При этом задний фронт на выходе его (п-{-т- -3)-го разряда переводит первый триггер 14 в состояние «О, разрешая работу второго триггера 7 по синхровходу. Таким образом, при втором и последуюших выполнениях теста по заднему фронту син/работа. В режиме «Работа логическая Ю хроимпульса генератора 12 (подача стимулиединица на входе 13 блокирует генератор 12 и определяет работу счетчика 6 в режиме асинхронной установки по входам данных. Таким образом, сигналы РВ, ЧТ/ЗП, адреса и данные поступают с входов счетчика 6 на соответствующие его выходы, что обеспечивает работу блока 1 оперативной памяти в обычном режиме (поскольку на входы сумматора 4 по модулю два поступают сигналы РВ и логический ноль, то его вы15

рующего воздействия и контроль выходной реакции разнесены во времени) вторым триггером 7 осуществляется регистрация сигнала с выхода блока 3 сравнения. Сигнал сравнения равен «О при совпадении данных на первых входах блока 3 сравнения (реакция блока 1 оперативной памяти) с данными на вторых его входах (эталонная реакция) и равен «1 при их несовпадении. Эталонная реакция формируется регистход поверяет сигнал РВ). Так как генератор 20 ром 5 на основе сигнала на первом и втором

25

12 заблокирован, то состояние второго триггера 7 и элемента 16 индикации остается неизменным. В режиме «Контроль логический ноль на входе 13 разрешает работу генератора и определяет работу счетчика 6 в режиме непрерывного пересчета (генератор 12 работает в автоколебательном режиме). При этом состояние счетчика 6 изеняется независимо от сигналов на его входах. Поскольку стимуляция адресных входов блока 1 памяти осуществляется разрядами сч етчика 6, начи- ЗО ная с третьего, то длительность обращения к блоку 1 памяти составляет восемь тактов синхросигнала генератора 12 (состояние счетчика 6 изменяется по переднему фронту синхросигнала). В течение первых четырех

управляющих входах, поданных с выхода сумматора по модулю два и третьего выхода счетчика 6 соответственно, сигнала на син- хровходе, поступающего с четвертого выхода ((л-|-3)-й разряд) счетчика 6, и сигналов с второй группы выходов счетчика 6, поданных на информационные входы регистра 5.

ность.

При исправном блоке 1 оперативной памяти на D-вход триггера 7 поступают «О и его состояние, а следовательно, и состояние элемента 16 индикации не изменяется При обнаружении хотя бы одного расхождения триггер 7 переходит в состояние «1. При этом формируется сигнал «Неисправен и блокируется генератор 12, т. е. происходит тактов осуществляется операция «Чтение, 35 останов теста по тому адресу блока 1 опе- в течение вторых - «Запись. Внутрь каж- ративной памяти, где обнаружена неисправ- дой четырехтактной операции вложен двухтактный сигнал РВ (обеспечивается сумматором 4 по модулю два), который принимает активный уровень при неизменных остальных сигналах, поданных на блок 1 оператив- ной памяти (тем самым достигается корректная временная диаграмма). Проход адресного пространства при неизменных входных данных осуществляется дважды в виду стимуляции выходов данных памяти разряда- .с сравнения, выход которого подключен к ин- - , - : л -- - формационному входу второго триггера, выход которого является выходом результата контроля устройства и соединен с первым входом генератора,второй вход которого является входом выбора режима устройства и 50 подключен к управляющему входу счетчика, синхровход которого соединен с выходом генератора и с синхровходом второго триггера, вход установки в «О которого подключен к выходу первого триггера, информационный вход которого является входом

Формула изобретения

Оперативное запоминающее устройство с самоконтролем, содержащее блок оперативной памяти, выходы которого являются информационными выходами устройства и соединены с входами первой группы блока

ми счетчика 6, начиная с (п + 4)-го. Это вызвано необходимостью записи информации в регистр при неизменном состоянии второй группы выходов счетчика 6. После двойного прохрда адресного пространства входные данные изменяются и начинается новый проход. Подобная последовательность операций характерна для теста «Марщ при полном переборе входных данных. Длительность одного выполнения теста составляет в данном случае тактов синхросигнала. Поскольку при подаче питания ячейки блока 1 оперативной памяти ориентируются произвольно то за время первого выполнения теста контроль выходных реакций не производится (первый триггер

55

логического нуля устройства, а вход установки в «1 является входо.м сброса устройства и подключен к входу сброса счетчика, выход старшего разряда которого подключен к синхровходу первого триггера, вход раз14 сохраняет состояние «1, удерживая второй триггер 7 в сброшенном состоянии). Завершение выполнения теста вызьз1вает возврат всех разрядов счетчика 6 в состояние «О. При этом задний фронт на выходе его (п-{-т- -3)-го разряда переводит первый триггер 14 в состояние «О, разрешая работу второго триггера 7 по синхровходу. Таким образом, при втором и последуюших выполнениях теста по заднему фронту син хроимпульса генератора 12 (подача стимули

рующего воздействия и контроль выходной реакции разнесены во времени) вторым триггером 7 осуществляется регистрация сигнала с выхода блока 3 сравнения. Сигнал сравнения равен «О при совпадении данных на первых входах блока 3 сравнения (реакция блока 1 оперативной памяти) с данными на вторых его входах (эталонная реакция) и равен «1 при их несовпадении. Эталонная реакция формируется регист25

ЗО

управляющих входах, поданных с выхода сумматора по модулю два и третьего выхода счетчика 6 соответственно, сигнала на син- хровходе, поступающего с четвертого выхода ((л-|-3)-й разряд) счетчика 6, и сигналов с второй группы выходов счетчика 6, поданных на информационные входы регистра 5.

ность.

Пр мяти н и его ние эл При о дения При эт и блок остано ративн сравне формац ход ко та конт входом ляется подклю синхро генерат гера, в ключен мацион

При исправном блоке 1 оперативной памяти на D-вход триггера 7 поступают «О и его состояние, а следовательно, и состояние элемента 16 индикации не изменяется При обнаружении хотя бы одного расхождения триггер 7 переходит в состояние «1. При этом формируется сигнал «Неисправен и блокируется генератор 12, т. е. происходит останов теста по тому адресу блока 1 опе- ративной памяти, где обнаружена неисправ- сравнения, выход которого подключен к ин- формационному входу второго триггера, выход которого является выходом результата контроля устройства и соединен с первым входом генератора,второй вход которого является входом выбора режима устройства и подключен к управляющему входу счетчика, синхровход которого соединен с выходом генератора и с синхровходом второго триггера, вход установки в «О которого подключен к выходу первого триггера, информационный вход которого является входом

Формула изобретения

Оперативное запоминающее устройство с самоконтролем, содержащее блок оперативной памяти, выходы которого являются информационными выходами устройства и соединены с входами первой группы блока

При исправном блоке 1 оперативной памяти на D-вход триггера 7 поступают «О и его состояние, а следовательно, и состояние элемента 16 индикации не изменяется При обнаружении хотя бы одного расхождения триггер 7 переходит в состояние «1. При этом формируется сигнал «Неисправен и блокируется генератор 12, т. е. происходит останов теста по тому адресу блока 1 опе- ративной памяти, где обнаружена неисправ- сравнения, выход которого подключен к ин- формационному входу второго триггера, выход которого является выходом результата контроля устройства и соединен с первым входом генератора,второй вход которого является входом выбора режима устройства и подключен к управляющему входу счетчика, синхровход которого соединен с выходом генератора и с синхровходом второго триггера, вход установки в «О которого подключен к выходу первого триггера, информационный вход которого является входом

логического нуля устройства, а вход установки в «1 является входо.м сброса устройства и подключен к входу сброса счетчика, выход старшего разряда которого подключен к синхровходу первого триггера, вход разрешения выборки блока оперативной памяти соединен с выходом сумматора по модулю л1ва, входы которого подключены к первому и второму выходам счетчика, третий выход, а также выходы первой и второй групп которого соединены соответственно с входом записи-чтения, адресными и информационными входами блока оперативной памяти, первый и третий информационные входы счетчика являются соответственно входом

мационные входы первой и второй групп счетчика являются соответственно адресными и информационными входами устройства, отличающееся тем, что, с целью упрощения устройства, в него введен регистр, причем синхровход, первый и второй управляющие входы регистра подключены соответственно к четвертому выходу счетчика, к выходу сумматора по модулю два и к третьему выходу счетчика, инфорационные входы и выходы

, . ...... r.iji, ,,.. v jiij i jLi iiiiv u., rjn J LJ d U, n 11 Dl С D AUll Ы rl D Ы A U I CM

обращения и записи устройства, второй ин-Ю регистра соединены соответственно с входаформационный вход счетчика подключен кми второй группы счетчика и с входами

входу логического нуля устройства, а инфор-второй группы блока сравнения.

мационные входы первой и второй групп счетчика являются соответственно адресными и информационными входами устройства, отличающееся тем, что, с целью упрощения устройства, в него введен регистр, причем синхровход, первый и второй управляющие входы регистра подключены соответственно к четвертому выходу счетчика, к выходу сумматора по модулю два и к третьему выходу счетчика, инфорационные входы и выходы

, rjn J LJ d U, n 11 Dl С D AUll Ы rl D Ы A U I CM

регистра соединены соответственно с входа

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1325571A1 |

| Оперативное запоминающее устройство с самоконтролем | 1984 |

|

SU1229826A1 |

| Устройство для контроля оперативной памяти тестом Марш с двоично-нарастающим адресным шагом | 1986 |

|

SU1532978A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1413676A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1647655A1 |

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1053165A1 |

| Устройство для контроля оперативной конвейерной памяти | 1989 |

|

SU1633463A1 |

Изобретение относится к вычислительной те.хнике и может быть исиользовано при построении запоминающих устройств с тестовым самоконтролем. Пелью изобретения является упрощение устройства. Устройство содержит блок оперативной памяти, генератор, счетчик, сумматор но модулю два, блок сравнения, регистр и два триггера. В устройстве осуществляется встроенный тестовый контроль многоразрядного блока оиеративной памяти модифицированным тестом с формироваиием эталонных данных на регистре. I ил.

| вып | |||

| ЮЗ) | |||

| Сер | |||

| Регистрационный ящик | 1918 |

|

SU983A1 |

| электроника рис | |||

| I | |||

| Оперативное запоминающее устройство с самоконтролем | 1984 |

|

SU1229826A1 |

| Солесос | 1922 |

|

SU29A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Счетная таблица | 1919 |

|

SU104A1 |

Авторы

Даты

1988-06-30—Публикация

1986-07-04—Подача