54) АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1978 |

|

SU805306A1 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Устройство для решения системы алгебраических уравнений | 1981 |

|

SU966702A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| РЕКОНФИГУРИРУЕМЫЙ ВЫЧИСЛИТЕЛЬНЫЙ КОНВЕЙЕР | 2011 |

|

RU2461867C1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2047896C1 |

| Матричный процессор | 1985 |

|

SU1354204A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБЪЕКТОВ ПО ИХ КОНТУРАМ | 1990 |

|

RU2090927C1 |

1

Изобретение относится к вычислительной технике и. может быть использовано при контроле ЦВМ по. модулю, а также в ЦВМ, работающей в системе счисления с основанием р у 2.

Известно арифметико-логическое устройство, содержащее отдельные узлы арифметической и логической обработки двоичной информации. В -зависимости от управляющим сигналов это устройство выполняет логические операции И, ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ, а также арифметическую операцию сложение. При выполнении логических операций используется только логический узел, а при выполнении арифметической операции сложение используется только арифметический узел С Известно арифметико-логическое устройство, выполняющее логические операции И, ИЛИ и. ИСКЛЮЧАЮЩЕЕ ИЛИ, а также операцию сложение над числами, заданными в двоичном коле, содержащее два узла десятичных корректоров, узлы логический, .сумматоров, перекоса кода, сдвига, переноса. Выполнение арифметических и логических операций осуществляется при помощи одних и тех же узлов арифметико-логического устройства ГЗД.

при таких схемных решениях арифметико-логические устройства не могут выполнять арифметические и логические операции над числами, представленными в системе счисления с основанием р 7 2.

Наиболее близким к предлагаемому по технической сущности является арифметико-логическое устройство,

0 содержащее три матрицы логических элементов И и две группы элементов ИЛИ, вертикальные и горизонтальные входные шины первой матрицы элементов И подсоединены соответственно 5 к выходным шинам третьей и второй матриц элементов И СЗ Недостаток известного устройстваневозможность выполнения логических операций И и ИЛИ.

0

Цель изобретения - расширение функциональных возможностей арифметико-логического устройства, заключающегося в возможности выполнения логических операций И и ИЛИ.

5

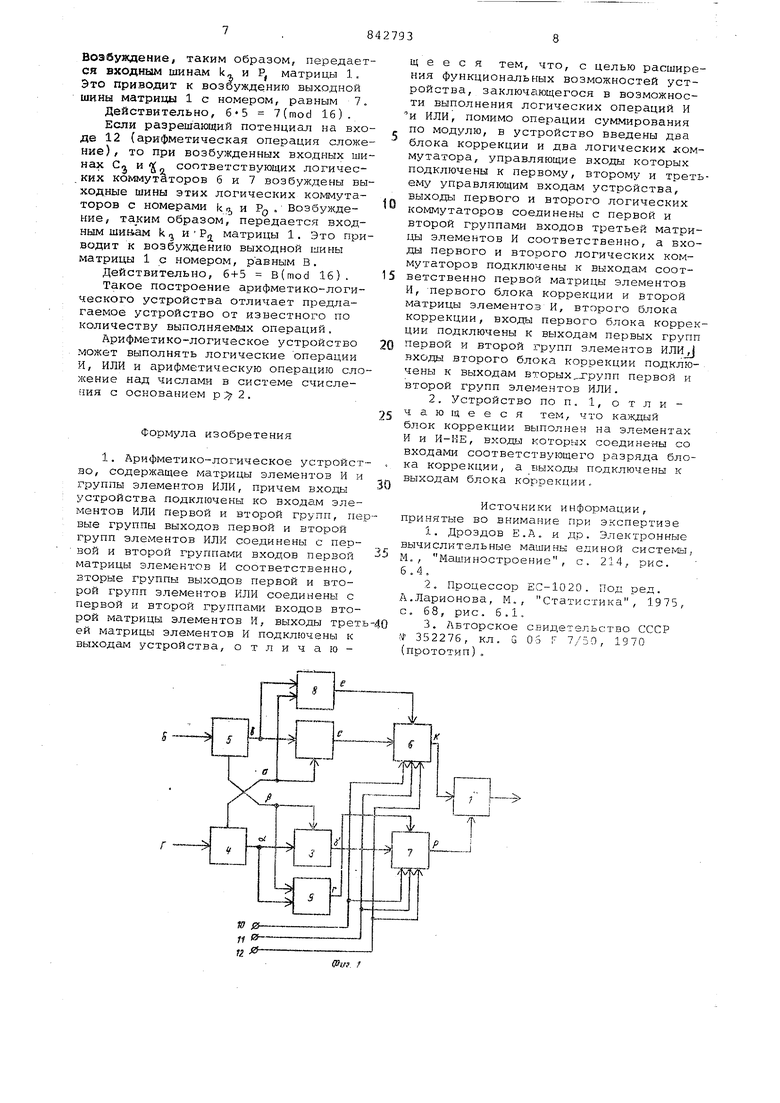

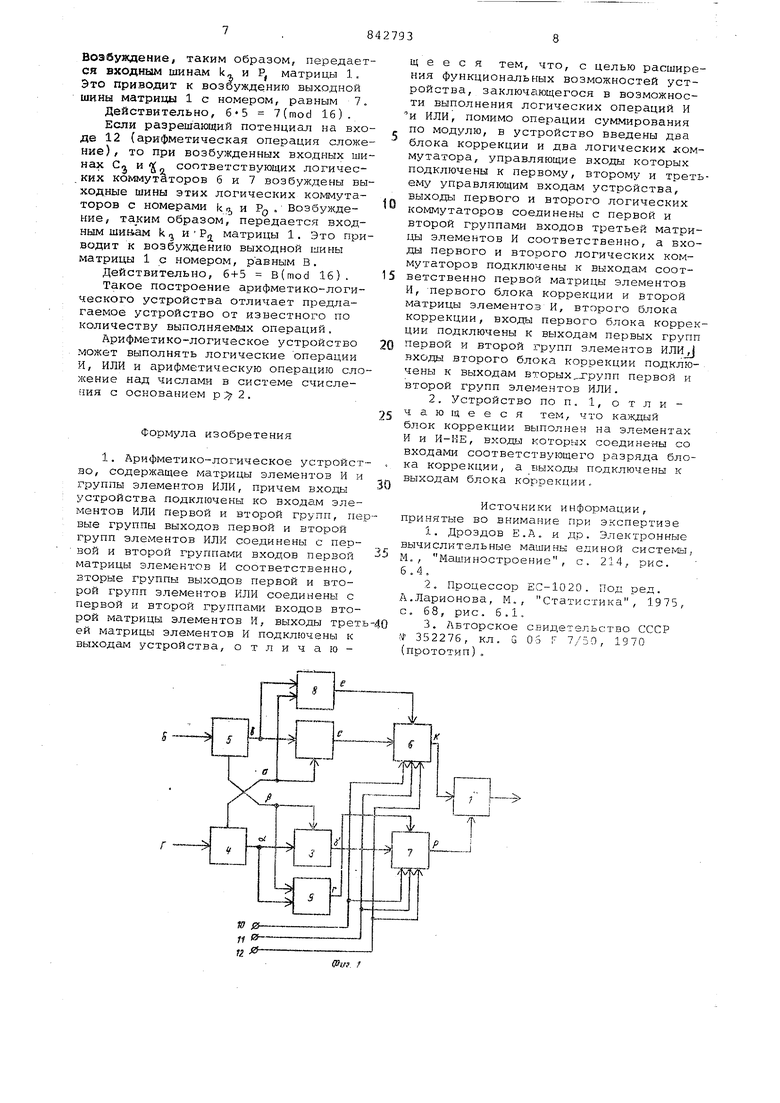

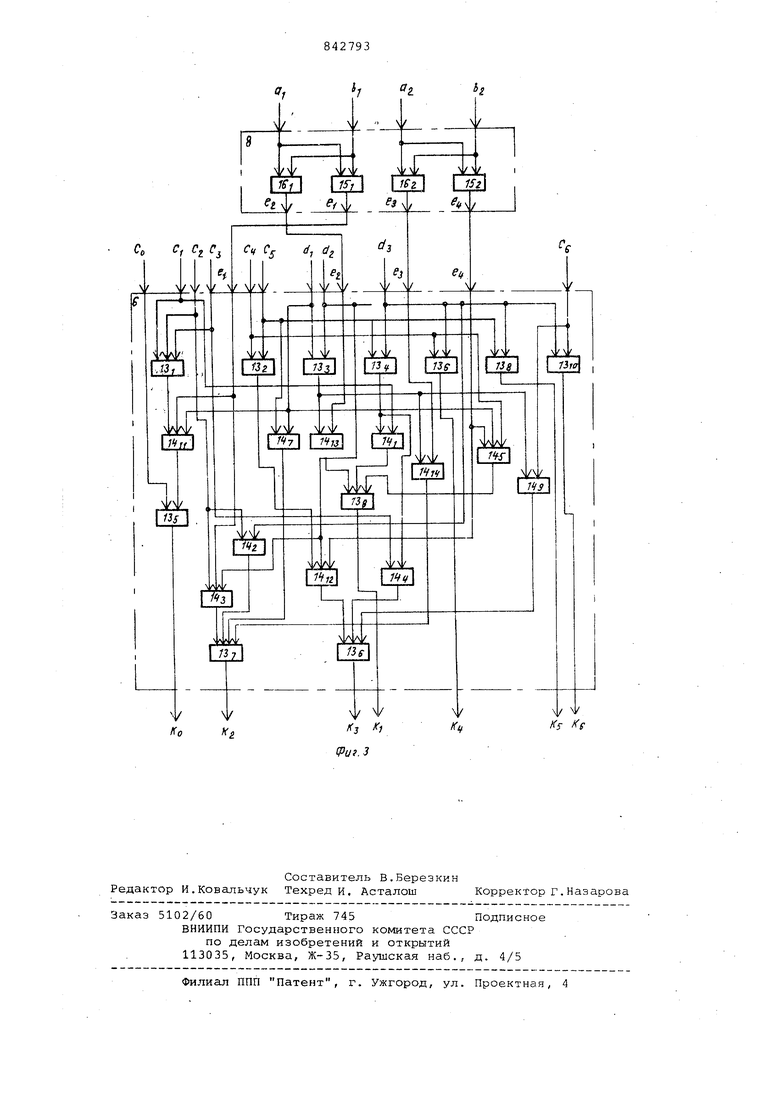

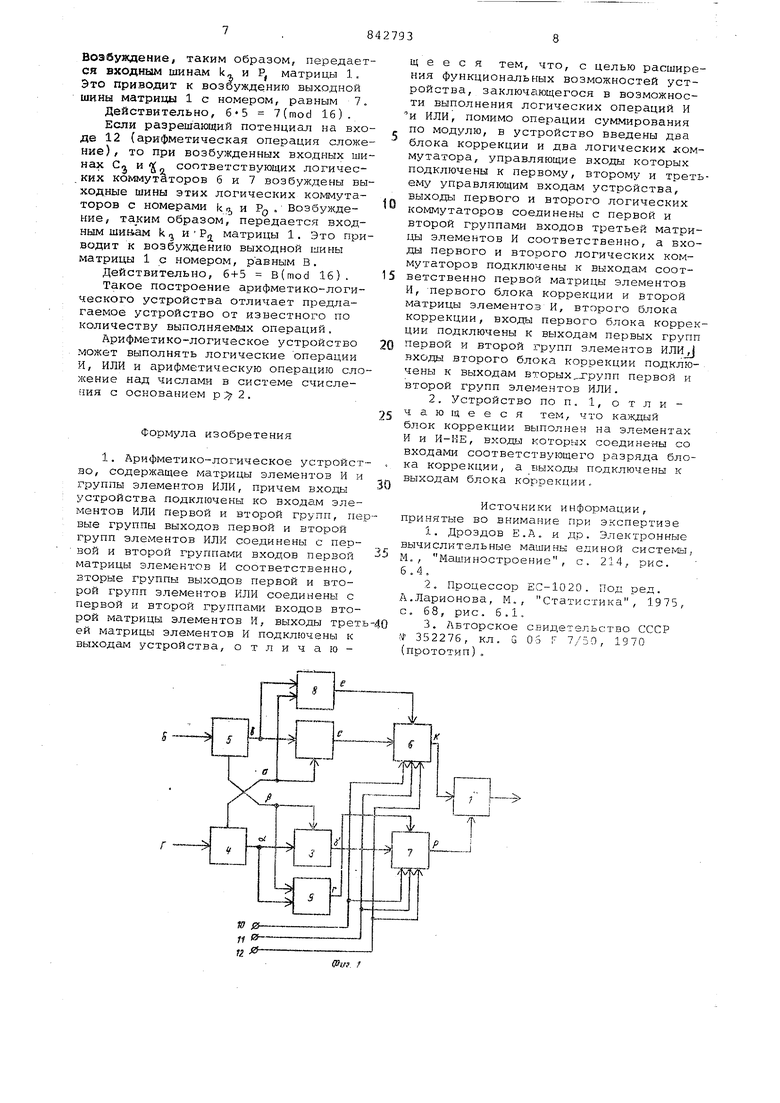

Поставленная цель достигается тем, что в арифметико-логическом устройстве, содержащем матрицы логических элементов И и группы элементов ИЛИ, причем входы устройства 0 подключены ко входам элементов ИЛИ первой и второй групп, первые группы выходов первой и второй групп элементов ИЛИ соединены с первой и второй группами входов первой матрицы элементов И соответственно, вторые группы выходов первой и второй групп элементов ИЛИ соединены с первой и вто рой группами входов второй матрицы элементов И, выходы третьей матрицы элементов И подключены к выходам устройства, введены два блока коррекции и два лйгических коммутатора, управляющие входы которых подключены к пер вому, второму и третьему управляющим входам устройства, выходы первого и второго логических коммутаторов соеди нены с первой и второй группами входов третьей матрицы элементов И соответственно, а входы первого и второго логических коммутаторов подключены к выходам соответственно первой матрицы элементов И, первого блока коррекции и второй матрицы элементов И, второго блока коррекции, входы первого блока коррекции подключены к выходам первых групп первой и второй групп элементов ИЛИ, входы второго блока коррекции подключены к выходам вторых групп первой и второй групп элементов ИЛИ, каждый блок коррекции выполнен на элементах И и И-НЕ, входы которых соединены со входами соот ветствующего разряда блока коррекции а выходы подключены к выходам блока коррекции. На фиг. 1 представлена блок-схема арифметико-логического устройства; на фиг. 2 и фиг. 3 - функциональные схемы отдельных узлов (блоков 1,4,5 и 6,8) арифметико-логического устрой ства по mod 16. Устройство содержит первую 1, вто рую 2 и третью 3 матрицы элементов И первую 4 и вторую 5 группы элементов ИЛИ, первый б и второй 7 логические коммутаторы, первый 8 и второй 9 бло ки коррекции, управляющие входы логи ческих операций И 10, ИЛИ 11 и арифметической операции 12 сложения. Горизонтальные входы k матрицы 1 подключены к выходным шинам логического коммутатора б, а вертикальные входы р матрицы 1 подключены к выходным ши нам логического коммутатора 7. Вертикальные а и горизонтальные в входные шины матрицы 2 подсоединены через элементы ИЛИ групп 4 и 5 к вход ным шинам устройства. Горизонтальные rt и вертикальные Ь входные шины матрицы 3 через элементы ИЛИ групп 4 и 5 подсоединены также к входным шинам устройства. Выходные шины матрицы 2 подключены к входным шинам логического коммутатора б, выходные шины матрицы 3 подключены к входным шинам логического коммутатора 7. Рассмотрим исходное состояние и связи на примере арифметико-логического устройства по mod 16. Входные шины Б (первое число) и Г (второе число) пронумерованы так, что при поступлении первого и второго чисел возбуждаются те шины первой второй групп элементов ИЛИ, HOMepj:. которых совпадают с конкретными значениями этих чисел (фиг. 2). Числа по mod 16 принимают значения О, 1, 2, ...,8,9, А, В, С, О, Е, F, Среди этих чисел числа О, 4, 8, С сравнимы с нулем по mod 4. Поэтому в группах элементов ИЛИ 4 и 5 входные шины устройства с номера ии 0,4,8, С объединены в выходные шины а и в„ этих групп соответственно. Числа 1, 5, 9, О сравнимы с единицей по mod 4. Поэтому в группах 4 и 5 входные шины устройства с номерами 1, 5, 9, D объединены в выходные шины а и в этих групп соответственно. Аналогично входные шины устройства с номерами 2, б, А, Е объединены в выходные шины а и в,, групп 4 и 5, и входные шины устройства с номерами 3, 7, В, F - в выходные шины а и в групп 4 и 5. Среди чисел по mod 16 частное от деления чисел 0,1,2,3 на 4, округленное до ближайшего целого в меньшую сторону, равно нулю. Поэтому в .группах 4 и 5 входные шины устройства с номерами 0,1,2,3 объединены в выходные шины otQ и (Ьр этих групп соответственно. Частное от деления чисел 4, 5, б, 7 на 4, округленное до ближайшего целого в меньшую сторону, равно единице. Поэтому в группах 4 и 5 входные шины устройства с номерами 4, 5, б, 7 объединены в выходные шины о: и |Ь этих групп соответственно. Аналогично входные шины устройства с номерами 8, 9, А, В объединены в выходные шины и fbq групп 4 и 5, и входные шины С, О, Е, F устройства объединены в выходные шины и fbn групп 4 и 5. Вертикальные шины а,,, а , а„, а„ группы 4 и шины Вр , в , Вп , в группы 5 подсоединены к вертикальным а, а , а,2, а, и горизонтальным в, в , .Вд,, в входным шинам матрицы 2. Выходные шины ао 0 / . , Сб группы 4 и р r,fb., , (bri , fbn, группы 5 подсоединены к горизонтальным о,, ct ,а Ctj, и вертикальным /Ьд , )Ь |Ьд / fcj . входным шинам матрицы 3. матрицы 2 и.З состоят из шестнадцати элементов И, расположенных по четыре в каждой строке и в каждом столбце. Входы элементов И, расположенных в нулевых строках матриц 2 и 3 подсоединены к Ьо и oL соответственно, в первыхстроках матриц 2 и 3 к шинам в и ct / во вторых строках к шинам в и oi, в третьих строках :к шинам в„ и о,. Аналогично входы . элементов И, расположенных в нулевых столбцах матриц 2 и 3, подсоединены к шинам а и fj , соответственно, в первых столбцах - к шинам а и , во вторых столбцах - к шинам а,, и в третьих столбцах - к шинам а и |iq Все элементы И матрицы 2, стоящие ,на диагонали матрицы, формируют одну и ту же функцию (например 2 + О ), поэтому они объеди нены в одну выходную шину матрицы. Число таких диагоналей равно семи, поэтому число выходных шин матрицы 2, также равно семи, и они прону- мерованы через Сд-С и подсоединены к соответствующим входным шинам логи ческого коммутатора б. Аналогично выходные шины матрицы 3 пронумерованы через jSo Sf. подсоединены к соответствующим входам логического коммутатора 7. Логический коммутатор 6 (фиг. 3) на логических элементах ИЛИ 13 - 1 И 14 - 1 описывается следующими логическими уравнениями l.0 CoY( CnVC ) е. d ; (d,iVd,j)Vej ( dj )vC e d d5Vd,.C,i.e,v().e, xd., ; ,i . ( d ) V (r V Cg ) . dj. t (() ; K C.d,,; K5 C5- K Ce, d , где. ko , k , . . . , k - функции на соответствующих выходных одноименных шинах kp , k , . . . , k логического коммутатора б; C(j, С , . . ., С, - переменные на соответствующих входных одноименных шинах Сд,С ,...,C логического комму татора 6; d , dj, dn - переменные на входах 10-12, характеризующие логические операции И, ИЛИ, арифметическую oneрацию сложение, соответственно; е, , е. , e,j, е - функции на соответственных выходных одноименных шинах е-, , &rii Si), &l блока 8 коррекции (на логических элементах И 16 ,. 16, И - НЕ 15 , IS), которые при переме ных а , Sif, в , Bf на соответствующих входных одноименных шинах а , aj В;, , BQ блока 8 коррекции равны Г ®2- Г -1 е. - BQ- aj; е , Блок 9 коррекции и логический ком мутатор 7 описываются аналогичными соответствующими логическими выражениями. Поэтому выходные шины блока 9 коррекции пронумерованы через f - р. и подключены к соответствующим входным шинам логического коммутатора 7, выходы которого пронумерованы через Рд - Pg и подключены к- соответствующим входным вертикальным шинам матри цы 1. Выходные шины k k логического коммутатора б подключены к соответст вующим входным горизонтальным шинам мaтpицы 1. Входы элементов И, расположенных в нулевой строке и в нулевом столбце матрицы. 1, подсоединены к входным шинам k и Рд матрицы 1, соответственно, в четвертой строке и во втором столбце - к шинам k и Р , в пятой строке и в третьем столбце - к шинам k и Pg, в седьмой строке и в четвертом столбце - к шинам k и Р , во второй строке и в пятом столбце - к шинам k, и.Р2, в третьей строке и в шестом столбце t, к шинам k,, и Р , в шестой строке и в седьмом столбце к шинам k И Р, (несоответствие между номерами строки матрицы 1 и ее входной горизонтальной шины сделано для наглядности и простоты чертежа). Выходы элементов И матрицы 1, соответствующие одной и той же сумме по mod 16, объединены в одну выходную шину. При поступлении первого Б и второго Г чисел возбуждается пара входных шин групп 4 и 5 элементов ИЛИ, соответственно, что Приводит к возбуждению пары входных шин матриц 2 и 3. В зависимости от разрешающих потенциалов на шинах 10-12 управления и пары возбужденных входных шин матриц 2 и 3 возбуждается пара входных шин матрицы 1, вследствие чего на выходе устройства формируется результат . Например, в арифметико-логическом устройстве по mod 16 возбуждены входные шины первого числа Б, равного 5, и второго числа Г, равного б. При возбуждении входной шины б группы 4 элементов ИЛИ возбуждаются выходные шины а и Сб, этой группы. При возбуж,цении входной шины 5 группы 5 элементов ИЛИ возбуждаются выходные .шяны а и (Ь группы 5. Возбуждение этих шин приводит к возбуждению входных шин и в матрицы 2, а, следовательно, выходной шины С- этой матрицы. Кроме того, возбуждаются входные шины Об и «1 матрицы 3, что приводит к возбуждению еевыходной шины с номером g ij. Если разрешающий потенциал на шине И 10 управления., то при возбужденных входных шинах С.,, и Т, соответствующих логических комм:.-таторов б и 7 возбуждены выходные этих бло(ов с номерами kg и Р . .: ждение, таким обравом, передается входным шинам k о, и Р матрицы 1. Это ггриводит к возбуждению выходной шикь- матрицы 1 с номером, равным 4. Дейст-Ештельно, 6. 5 4(mod 16) . Если разрешающи потенциал на шине логической операции И;и 11, то при возбужденных входных к;инах С., и соответствующих логическ-х коммутатоов б и 7 будут возбужд: ны выходные шны этих блоков с номерами kj и Ру , Возбуждение, таким образом, передает PJ матрицы 1. ся входным ШИНёШ ka и Это приводит к возбуждению выходной шины матрии;ы 1 с номером, равным 7. Действительно, 6:5 7(mod 16). Если разрешающий потенциал на вхо де 12 (арифметическая операция сложе ние), то при возбужденных входных ши нах С« и jj, соответствующих логичес.них коммутаторов 6 и 7 возбуждены вы ходные шины этих логических коммутаторов с номерами k,j, и Р . Возбуждение, таккм образом, передается входным kq иPI матрицы 1. Это при водит к возбуждению выходной иины матрицы 1 с номером, равным в. Действительно, 6+5 В(mod 16). Такое построение арифметико-логического устройства отличает предлагаемое устройство от известного по количеству,выполняемых операций. Арифметико-логическое устройство может выполнять логические операции И, ИЛИ и арифметическую операцию сло жение над числами в системе счисления с основанием . Формула изобретения 1, Арифметико-логическое устройст во, содержащее матрицы элементов И и группы элементов ИЛИ, причем входы устройства подключены ко входам элементов ИЛИ первой и второй групп, пе вые группы выходов первой и второй групп элементов ИЛИ соединены с первой и второй группагли входов первой матрицы элементов И соответственно, вторые группы выходов первой и второй групп элементов ИЛИ соединены с первой и второй группами входов второй матрицы элементов И, выходы трет ей матрицы элементов И подключены к выходам устройства, отличаюл f щ е е с я тем, что, с целью расширения функциональных возможностей устройства,, заключающегося в возможности выполнения логических операций И и ИЛИ, помимо операции суммирования по модулю, в устройство введены два блока коррекции и два логических JCOMмутатора, управляющие входы которых подключены к первому, второму и третьему управляющим входам устройства, выходы первого и второго логических коммутаторов соединены с первой и второй группами входов третьей матрицы элементов И соответственно, а входы первого и второго логических коммутаторов подключены к выходам соответственно первой матрицы элементов И, первого блока коррекции и второй матрицы элементов И, второго блока коррекции, входы первого блока коррекции подключены к выходам первых групп первой и второй групп элементов ИЛИ, входы второго блока коррекции подклю-. чены к выходам вторых групп первой и второй групп элементов ИЛИ. 2. Устройство по П. 1, отличающееся тем, что каждый блок коррекции выполнен на элементах И и И-НЕ, входы которых соединены со входами соответствующего разряда блока коррекции, а выходы подключены к выходам блока коррекции. Источники информации, принятые во внимание при экспертизе 1.Дроздов Е,А. и др. Электронные вычислительные машины единой системы, М,, Машиностроение, с. 214, рис. 6.4. 2.Процессор ЕС-1020. Под ред. А.Ларионова, М., Статистика, 1975, с. 68, рис. 6.1. 3.Авторское свидетельство СССР № 352276, кл. G 06 F 7/50, 1970 (прототип).

ОЧбС 159Д 2Ш S7BF tfSff

(Put. i.

Авторы

Даты

1981-06-30—Публикация

1978-06-14—Подача