(54).МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1979 |

|

SU809174A1 |

| Матричное вычислительное устройство | 1979 |

|

SU824195A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1509881A1 |

| Вычислительное устройство | 1981 |

|

SU1032454A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1108440A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Асинхронный матричный вычислитель обратных тригонометрических функций | 1982 |

|

SU1132286A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1520512A1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих процессорах и специализированных устройствах.

Известны матричные множительные устройства, в которых операция возведения зо вторую степень обычно осуществляется как операция умножения 1 и 2.

Однако известные матричные множительные устройства требуют для своей реализации больших аппаратурных затрат и не имеют предельного быстродействия.

Наиболее близким по технической сущности к предлагаемому изобретению является матричное устройство, предназначенное для умножения двух п-разрядных чисел, состоящее из (п-1) строк сумматоров, п строк элемейтов И, причем каждая строка содержит п столбцов 3.

Недостаток устройства - большие аппаратурные затраты при реализаци а именно; п (п-1)-сумматоров и п элементов И и ограниченное быстродействие, составляющее (2nt +nCr ) , где tg - время получения сигнала

переноса Е после того, как на его входы поступил последний из входных сигналов, С - время получения сигнала суммы В.

Цель изобретения - увеличение быстродействия и сокращение аппаратурных затрат при реализации устройства.

Поставленная цель достигается тем, что в матричном устройстве, содержащем матрицу ячеек из п/2 строк и (п-1) столбцов, причем каждая ячейка содержит сумматор и элемент И,

первый вход сумматора 1-ой строки

j-ro столбца (,...,n/2;J 1,...,п-1, где п разрядность операнда) соединен с первым выходом сумматора i-ой строки (j+l)-ro столбца, первые входы

сумматоров (п-1)-го столбца соединены с нулевыми входами устройства, входы элементов И первой строки соединены соответственно со входами старших разрядов операнда, второй

вход сумматора 1-ой строки j-ro столбца соединен с выходом соответствующего элемента И, третий вход сумматора 1-ой строки j-го столбца соединен со BTOptJM выходом сумматора (i-1)ой строки (j-2)-ro столбца, третьи

входы сумматоров первой строки нечетных столбцов соединены со входами разрядов устройства, третьи входы сумматоров первой строки четных столбцов соединены с нулевыми входами устройства, третий вход сумматора i-ой строки второго столбца соединен с первым выходом сумматора (i-1)ой строки первого столбца, второй выход сумматора i-ой строки j-го столбца соединен с третьим входог/ сумматора (1+1)-ой строки (i+2)-ro столбца, вторые выходы {n-l)-ro и (п-2)-го сумматоров каждой строки и вторые выходы сумматоров строки соединены с выходами устройства, первые выходы сумматоров первого столбца каждой строки соединены с третьими входами соответствующих сумматоров последующей строки второго столбца, первый выход сумматора П/2-ОЙ строки первого столбца соединен с выходом устройства, два младших выхода устройства соединены соответственно с одним из нулевых Эффективность устройства заключается в уменьшении аппаратурных затрат при его реализации и увеличении быстродействия при вычисления Для реализации устройства требуется (п-1). I сумматоров и (п-1) -тг элементов И, что примерно вполовину экономит количество оборудования по сравнению с известным устройством. Время работы устройства примерно ра но 2п -tg + 4t , что означает выигрыш по быстродействию -j ,Q + 4t где tg, , - время п Ьлучения сигнала суммы сумматора, tg - время получения переноса сумматора.

входов устройства и входом младшего разряда операнда.

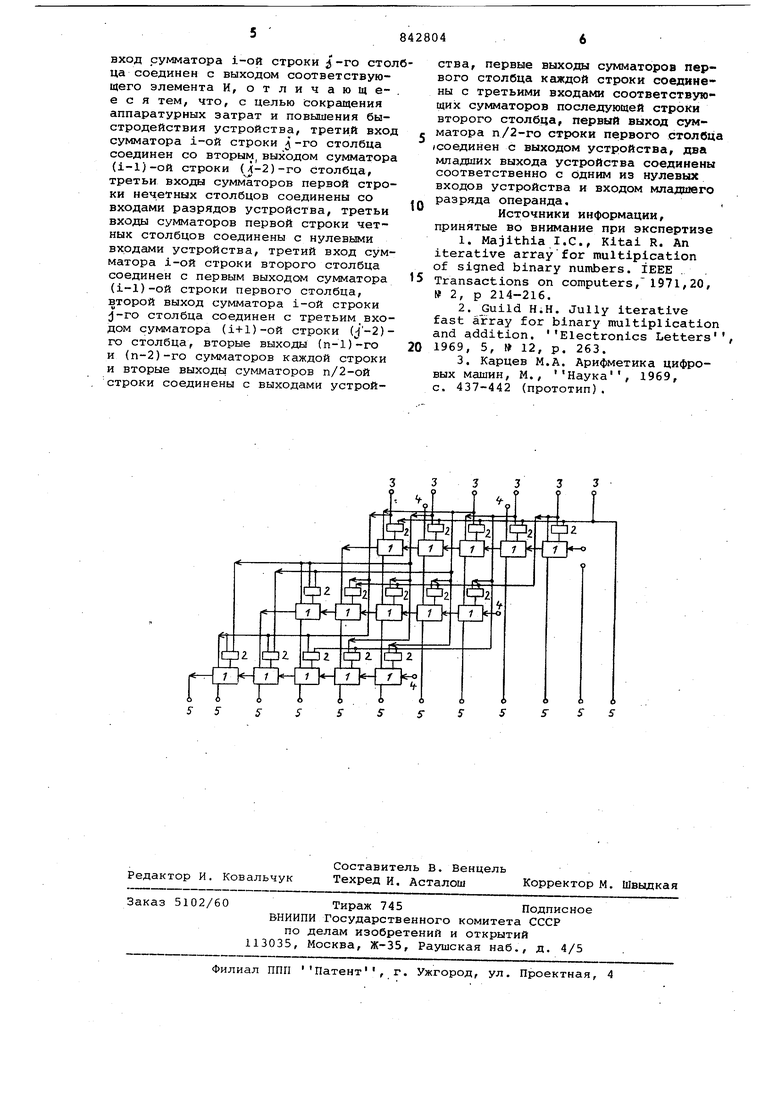

На чертеже представлена блок-схема матричного устройства возведения в квадрат.

Устройство содержит сумматоры 1, элементы И 2, входы 3 и 4 (входы 4для подачи нулевых сигналов), выходы 5.

Устройство работает следующим образом.

Каждая строка элементов И формирует определенную группу частичных произведений. Каждая строка сумматоров суммирует эти частичные произведения с другой группой частичных произведений. Улучшение характеристи алстродействия и затрат оборудования происходит в результате учета свойства склеивания некоторых членов частичных произведений.

Учет этого свойства иллюстрируетс.я на данном примере. Пусть хдвоичное 6-разрядное число. Требуется найти . Формула изобретения Матричное устройство для возведения в квадрат, содержащее матрицу ячеек из п/2 строк и (п-1) столбцов, причем каждая ячейка содержит сумматор и элемент И, первый вход сумматора i-ой строки 3-го столбца (i 1, .. . ,n/2;,j 1. . . ,n-l, где п - разрядность -операнда) соединен с первым выходом сумматора 1-ой строки (з+1)-го столбца, первые входы сумматоров (п-1)-го столбца соединены с нулевьами входами устройства, входы элементов И первой строки соединены соответственно со входами старших разрядов операнда, второй вход сумматора i-ой строки -го стол ца соединен с выходом соответствующего элемента И, отличающее с я тем, что, с целью сокращения аппаратурных затрат и повышения быстродействия устройства, третий вход сумматора i-ой строки -го столбца соединен со вторым, выходом сумматора (1-1)-ой строки (J-2)-ro столбца, третьи входа сумматоров первой строки нечетных столбцов соединены со входами разрядов устройства, третьи входы сумматоров первой строки четных столбцов соединены с нулевыми входами устройства, третий вход сумматора i-ой строки второго столбца соединен с первым выходом сумматора (i-l)-oй строки первого столбца, второй выход сумматора i-ой строки j-ro столбца соединен с третьим входом cyMviaTopa (i+l)-oй строки (j-2}го столбца, вторые выходы (n-l)-ro и (п-2)-го сумматоров каждой строки и вторые выходы сумматоров n/2-ой строки соединены с выходами устрой5 5 5 5

5- 5Г 5 ства, первые выходы сумматоров первого столбца каждой строки соединены с третьими входами соответствующих сумматоров последующей строки второго столбца, первый выход сумматора n/2-ro строки первого столбца соединен с выходом устройства, два младших выхода устройства соединены соответственно с одним из нулевых входов устройства и входом младшего разряда операнда. Источники информации, принятые во внимание при экспертизе 1.Majithia I.e., Kitai R. An iterative array for multipication of signed binary numbers. IEEE . . Transactions on computers,1971,20, 2, p 214-216. 2.Guild H.H. Jully iterative fast array for binary multiplication and addition. Electronics Letters 1969, 5, № 12, p. 263. 3.Карцев M.A. Арифметика цифровых машин, М., Наука, 1969, с. 437-442 (прототип).

Авторы

Даты

1981-06-30—Публикация

1979-06-25—Подача