(54) МАТРИЧНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Матричное вычислительное устройство | 1978 |

|

SU750485A1 |

| Матричное устройство для возведенияВ КВАдРАТ | 1979 |

|

SU842804A1 |

| Матричное вычислительное устройство | 1981 |

|

SU960803A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1134948A1 |

| Матричное устройство для умножения | 1981 |

|

SU972502A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809174A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих процессорах и специализированных вычислительных устройствах.

Известны матричные вычислительные устройства для выполнения операции деления двоичных чисел 1.

Недостатками матричных вычислительных устройств являются ограниченные функциональные возможности при данном наборе узлов и связей между ними.

Наиболееблизким к предлагаемому по технической сущности является матричное вычислительное устройство для выполнения операции Деления двоичных чисел, содержащее матрицу вычислительных ячеек, каждая из которых содержит сумматор по модулю два и одноразрядный сумматор С

Недостатком известного матричного устройства является ограниченные функционгипьные возможности, обеспечивающие выполнение лишь одной арифметической операции деления двоичных

чисел.

.Цель изобретения - расширение функциональных возможностей устройства за

за счет вычисления дополнительных функций

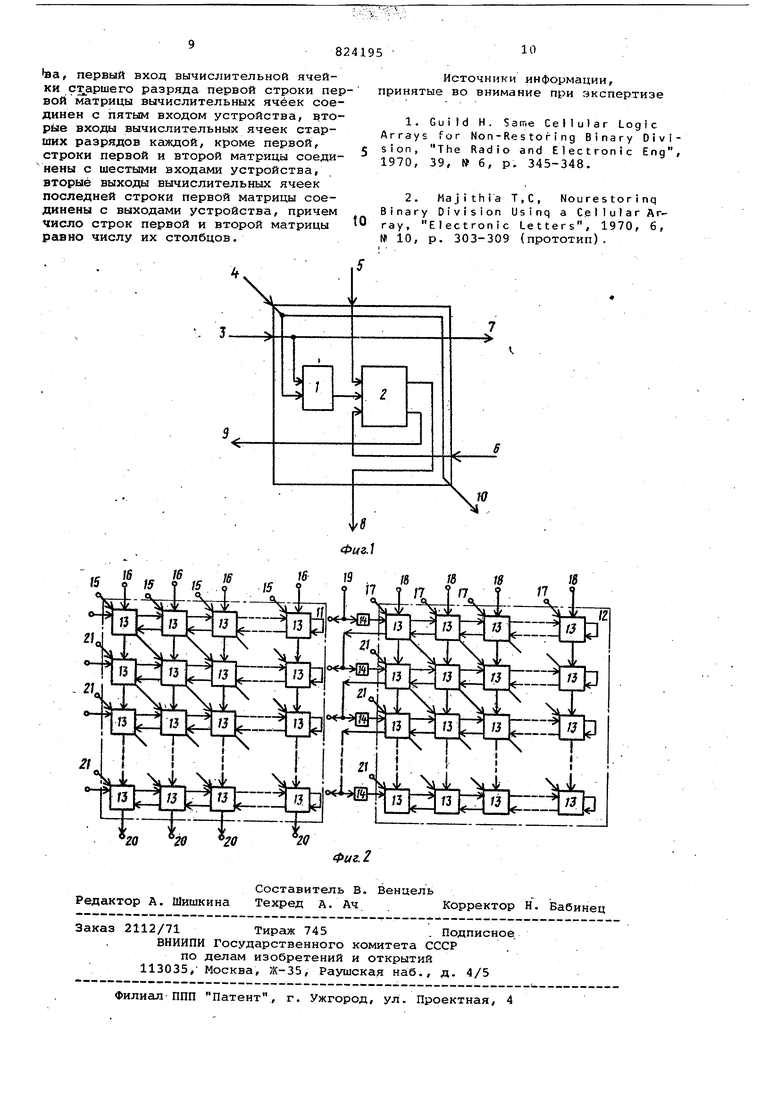

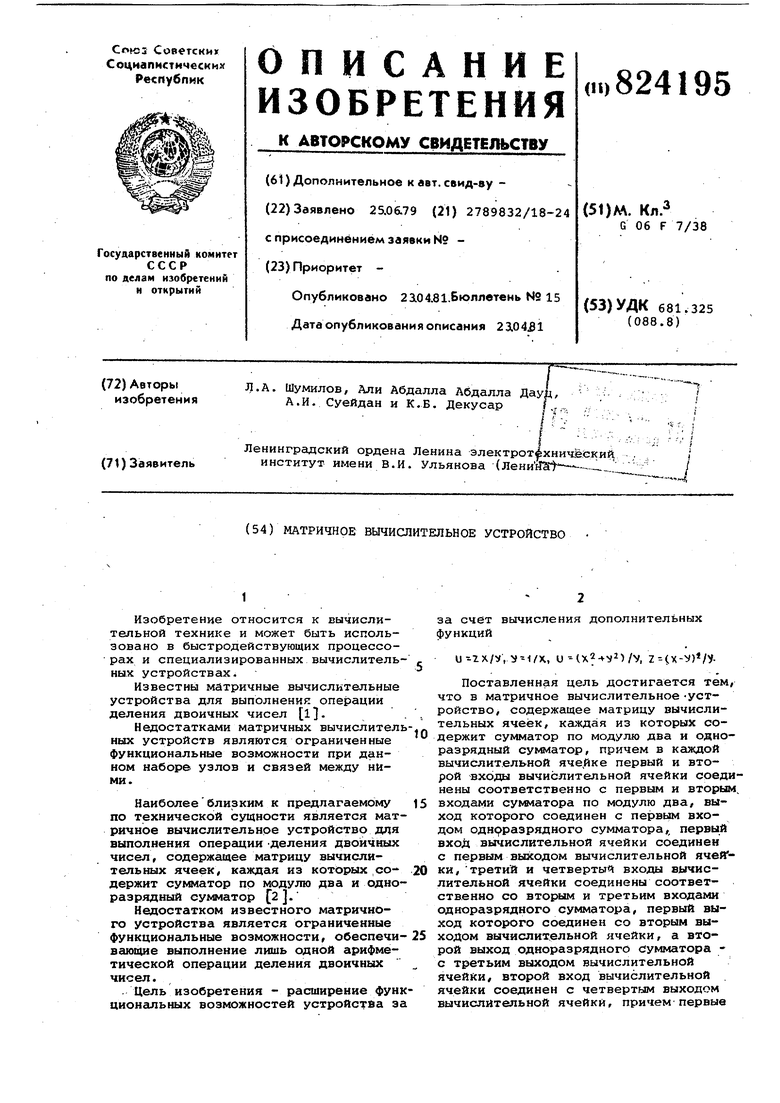

u-ix/v,v-i/x, u--()/v, z(.x-v)/yПоставленная цель достигается тем, что в матричное вычислительное -устройство, содержащее матрицу вычислительных ячеек, каждая из которых содержит сумматор по модулю два и одноразрядный сумматор, причем в каждой вычислительной ячейке первый и второй входы вычислительной ячейки соединены соответственно с первым и вторым входами сумматора по модулю два, выход которого соединен с первьам входом одноразрядного сумматора,, первый вход вычислительной ячейки соединен с первым выходом вычислительной ,третий и четвертый входы вычислительной ячейки соединены соответственно со вторым и третьим входами одноразрядного сумматора, первый выход которого соединен со вторым выходом вычислительной ячейки, а второй выход одноразрядного сумматора с третьим выходом вычислительной ячейки, второй вход вычислительной ячейки соединен с четвертым выходом вычислительной ячейки, причем первые выходы вычислительных ячеек каждого, столбца матрицы соединены соответственно с первыми входами вычислительных ячеек предыдущего столбца тех же строк матрицы, вторые выходы вычислительных ячеек каждой строки матрицы соединены соответственно с третьими входами вычислительных ячеек последующей строки тех же столбцов матрицы, третьи выходы вы числительных ячеек каждого столбца матрицы-соединены соответственно с четвертыми входами вычислительных яч ек последующего столбца, тех же строк матрицы, четвертые выходы вычислительных ячеек каждой строки матрицы соединены соответственно со вторыми входами вычислительных ячеек последующей строки предыдущих столбцов матрицы, первый выход и четвертый йход вычислительной ячейки младшего разряда .каждой строки матрицы соединены между собой, причем вторые входы вычислительных ячеек первой строки матрицы соединены с первыми входа ми устройства, третьи входы .вычислительных ячеек первой строки матрицы соединены со вторыми входами устройства, дополнительно введены h элементов НЕ и -вторая матрица вычислительных ячеек, причем первый вход вычислительной ячейки старшего разря да каждой строки первой матрицы соед нен с входом соответствующего элемен та НЕ и с третьим выходом вычислител ной ячейки старшего разряда предыдущей строки второй матрицы, выходы эл элементов НЕ соединены с первыми выходами соответствующих вычислительных ячеек старшего разряда последующей строки второй матрицы, причем вторые и третьи входы вычислительных ячеек первой строки второй матрицы соединены соответственно с третьими и четвертыми входами устройства, пер вый вход вычислительной ячейки старшего разряда первой строки первой матрицы вычислительных ячеек соединен с пятым входом устройства, вторы входы вычислительных ячеек старших разрядов каждой, кроме первой, строки первой и второй матрицы соединены с шестыми входами устройства, втор)ые выходы вычислительных ячеек последней строки первой матрицы соединены с выходами устройства, причем число строк первой и второй матрицы равно числу их столбцов. Матричное вычислительное устройство выполняет операцию деления и вы числения следующих функций U--ZX/V, М/Х, U--(., Z4X-V)/V и работают по разностно- 1терацион - ному методу. Для реализации операции подбирается для знаменателя и одного з сомножителей такой общий для них ножитель -И.1а.2- о л что он приблизит значения знаменатея к величине, равной второму сомножителю числителя, и во столько же раз изменит значение числителя. В результате имеют место следующие равенства 00 -(НО ,... 1.2 Ограничиваясь первыми членами суммы и пренебрегая погрешностью можем считать, что на )-й итерации преобразованный знаменатель . окажется равным Z. Тогда значение Ь, . найденное из (1) и подставленное в (2), даст Таким образом, следствием устремления является устремление . Итерационный процесс проводится по следующему алгоритму Ч, , -v,ecM , c,--sлgмY- -l, i o, 1останов,еслм J.-0 T., ,. начальными условиями д-х , Для реализации операции подбирается для X такой множитель VM.|c.2 ,-(.), оторый при соответствующем подборе ператоров ,+lV устремляет знаение аргумента х к величине, равной единице ... (3) Воздействовав этим же итерационным роцессом с тем же законом изменения нака оператора q. на изменение веичины функции и приняв за ее начсшьое значение , получим следующее ыражение для приближения искомой ункции. ,.2 Ограничиваясь первыми членами ряа суммы и пренебрегая погрешностью , можно считать, что на (i-v-iy-f итерации преобразованное зн чение аргумента х окажется равным единице. Тогда значение коэффициент найденное из (3) и подставленное в (4), дает . Итерационный процесс вычисления данной операции описывается следую щу1ми соотношениями 4r- i- V4V2- X,,.X,.,V.X2-( q.« sig-h z- Z bo, -, , i.,-X2-tiM) С начальными условиями x., , Для реализации операции u(Ay) подбираются к операндам х и у таки коэффициенты . л о 1 П4 - SQ -( (,., которые смогли Зы .в ходе итерационн го процесса приблизить операнд х К нулю с наперед заданной погрешность , где п - число итераций. Значения операндов с учетом выбр ных коэффициентов k и k могут быт выражены соотношениями X--X- |cv.2 - ,- -xscv.2Определяя значение суммы в (5) из у ловия X - О и подставляя результат в (6), приходим к выводу, что следств ем стремления является у.(х +У )/у. Здесь необходимо выполнени условия . Итерационный процесс вычисления данной операции описывается следующими соотношениями x,,x,,o;, ,,, .-Я,u.-si nz--l J Ji Ч (--t.&CAM ,если , с начальными условиями х x,v -V; Для реализаций операции z«(x-y) наложим на итерационный процесс изм нения операндов хну закон изменен равных множителей вида VSM- cv52- . Приближение операнда х будем ра сматривать как сумму исходного знач ния операнда х и приближений операн (6) да Y , а приближение операнда v как разность исходного значения операнда Y и приближения операнда х. . x.-x ri- i:cv-2- l (Т) -оЭ J. --V-4l-Scv Z .Требуя, чтобы , приближение операнда V стремится принять значение, равное искомой зависимости, т.е. 1 i m y:/,z Алгоритм вычисления зависимости вытекает из (7) и (8) и описывается следующими соотношениями ,с, Т-,,-хГ,-ф,, cV--eigMx- ИПеслит,, .)Ч,, останоь, если-j- -о с начальными условиями ,. у у-х, х-у На фиг. 1 изображена структурная схема вычислительной ячейки устройства, на фиг. 2, - блок-схема матричного вычислительного устройства-. Каждая вычислительная ячейка содержит сумматор 1 по модулю два, одноразрядный сумматор 2, первый, второй, третий и четвертый входы.3-6, первый, второй, третий и четвертый выходы 7-10. Матричное вычислительное i устройство содержит первую и вторую матрицы 11 и 12 вычислительных ячеек вычислительные ячейки 13, п элементов НЕ второй матрицы.14, первые и вторые входы 15 и 16 устройства, третьи и четвертые входы 17 и 18 устройства, пятый вход 19 устройства и выходы 20 устройства, шестые входы 21 устройства. Матричное вычислительное устройство работает следующим образом. Каждая из матриц выполняет вычисление по рекуррентному отношению . типа ,.,cV,xa-(- д1е X и у - операнды, поступающие на входы матрицы; q- - элемент, определяющий тип выполняемой операции (сложе-. . ние или вычитание). q. образуется на третьем выходе ычислительной ячейки старшего разряа 1-й строки второй матрицы 12 и пределяет тип выполняемой опергщин последующей строке обеих матриц. , то в последующей строке матрицы выполняется операция ычитания, а в последующей строке тороЯ матрицы - операция сложения наоборот, если , то в последущей строке второй матрицы выполняется операция сложения, а в последующей строке первой матрицы - опера ция вычитания, Сдвиг одного из операндов вправо на (i+1) разрядов (что соответствует умножению на ) осуществляется внутриматричными соединениями. При выполнении всех перечисленных зависимостей устройство работает по единому алгоритму и отличие состоит только в начальных условиях. При вьачислении зависимости ,х/у на входы 15-18 устройства подаются соот ветственно значения операндов 0, 5хо; Уо УТсГг-у На вход 19 подается потенциал, соответствующий знаку 0, т.е. если знак fo отрицателен, то подается единичный потенцигш, и если знак положительный, то подается нулевой потенци ал. На выходе 20 получаем значение результата u ZX/y. Операция деления выступает как частный случай вычисления зависимости u xz/y. Для этого нужно взять ,5, а значение Y взять как 0,5у, в результате получаем значение . Для вычисления зависимости V l/xна входа 15-18 подаются соответствен но следующие значения 0,5у(5; Уо i где у 0,5; хо. х; ,5-x На вход, 19 подается потенциал, соответствующий знаку То- На выходе 20 получаем значение результата . Для вычисления зависимости и( -(у)/у на входы 15-18 подаются соответственно значения 0,5хо, Уо 0,5х , Zfj, . На вход 19 подается сигнал, соответствующий знаку ZG- На выходе 20 получаем зна чение результата и() /у, Для вычисления зависимости z - (х-у ) /у на входы 15-18 подаются соот ветственно значения О, 5хо;Уо; О 5Уо ; i Хо х+у;уо у-х; ,5-y. На вход 19 подается потенциал, соответствующий знаку ZQ. На выходе 20 получаем зна чение результата z(x-y)/y. На входы 21 всегда подается нуле вой потенциал. Эффективность изобретения заключается в расширении функциональных возможностей матричного вычислитель ного устройства по сравнению с известным за счет выполнения вычислений дополнительных операций U-ix/V; и( 2i(X-V)/VФормула изобретения Матричное вычислительное устройство, содержащее матрицу вычислитель ных ячеек, каждая из которых содержит сумматор по модулю два и однораз рядный сумматор, причём в каждой вычислительной ячейке первый и второй входы вычислительной ячейки соединен соответственно с первьн и вторым вхо дами сумматора по модулю два, выход которого соединен с первым входом одноразрядного сумматора, первый вход вычислительной ячейки соединзн с первым выходом вычислительной ячейки, третий и четвертый входы вычислительной ячейки соединены соответственно со вторым и третьим входами одноразрядного сумматора, первый выход которого соединен со вторым выходом вычислительной ячейки, а второй выход одноразрядного сумматора - с третьим выходом вычислительной ячейки, второй вход вычислительной ячейки соединен, с четвертым выходом, вычислительной ячейки, причем первые выходы вычислительных ячеек каждого столбца матрицы соединены соответственно с первыми входами, вычислительных ячеек предыдущего столбца тех же строк матрицы, вторые выходы вычислитель.ных ячеек каждой строки матрицы соединены соответственно с третьими входами вычислительных ячеек последующей строки тех жестолбцов матрицы, третьи выходы вычислительных ячеек каждого столбца матрицы соединены соответственно с четвертыми входами вычислительных ячеек последующего столбца тех же строк матрицы, четвертые выходы вычислительных ячеек каждой строки матрицы соединены соответственно со вторыми входами, вычислительных ячеек последующей строки предыдущих столбцов матрицы, первый выход и четвертый вход вычислительной ячейки младшего разрядакаждой строки матрицы соединены.между собой, причем вторые входы вычислительных ячеек первой строки матрицы соединены с первыми входами устройства, третьи входы вычислительных ячеек первой строки матрицы соединены со вторыми входами устройства, отличающе-; е с я тем, что, с целью расширения функциональных возможностей матричного вычислительного устройства за счет вычисления дополнительных функций вида Z-X/S.V, (, U-V)/V в него дополнительно введены п элементов НЕ и вторая матрица вычислительных ячеек, причем первый вход вычислительной -ячейки старшего разряда каждой строки первой матрицы соединен со входом соответствующего эле мента НЕ и с третьим выходом вычислительной ячейки старшего разряда предыдущей строки второй матрицы, выхода элементов НЕ соединены с первыми выхода 1и соответствующих вычислительных ячеек старшего разряда последующей строки второй матрицы, при«зсем вторые и третьи входы вычислительных ячеек первой строки второй матрицы соединены соответственно с .третьим и четвертым входами устройст ва, первый вход вычислительной ячейки старшего разряда первой строки пер вой матрицы вычислительных ячеек соединен с пятЕлм входом устройства, вторые входы вычислительных ячеек старших разрядов каждой, кроме первой, строки первой и второй матрицы соедийены с шестыми входами устройства, вторые выходы вычислительных ячеек последней строки первой матрицы соединены с выходами устройства, причем число строк первой и второй матрицы равно числу их столбцов. Источники информации, принятые во внимание при экспертизе 1.Guild Н. Same Cellular Logic Arrays for Non-Resto гing Вinarу Division, The Radio and Electronic Eng, 1970, 39, 6, p. 345-348. 2.Majithia T,C, Nourestorinq Binary Division Usinq a C.etlular Array, Electronic Letters, 1970, 6, № 10, p. 303-309 (прототип).

Авторы

Даты

1981-04-23—Публикация

1979-06-25—Подача