(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Запоминающее устройство | 1973 |

|

SU447757A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU364962A1 |

| ВСЕСОЮЗНАЯ ' | 1973 |

|

SU368645A1 |

| Запоминающее устройство | 1982 |

|

SU1042083A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Запоминающее устройство | 1973 |

|

SU481067A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Известны запоминающие устройства, содержащие числовые и разрядные щины, в перекрестиях которых установлены запоминающие элементы, выполненные, например, в виде сегнетоэлектрических пьезотрансформаторов, и блоки адресных ключей.

Для данных устройств характерна больщая сложность, низкие надежность работы и экономичность.

Цель изобретения - упрощение устройства, повыщение надежности его работы, экономичности и быстродействия.

Поставленная цель достигается тем, что устройство содержит формирователь стира-. ния, а запоминающие элементы выполнены в виде щирокополосных сегнетоэлектрических пьезотрансформаторов, числовые электроды которых подключены к разрядным щйнам через диоды, а экранирующие электроды объединены по адресам в общие щины и через блок адресных ключей подключены к общей щине адресных ключей, в котору1б включен формирователь стирания, при этом управляющие входы блока адресных ключей

соединены с соответствующими числовыми щинами.

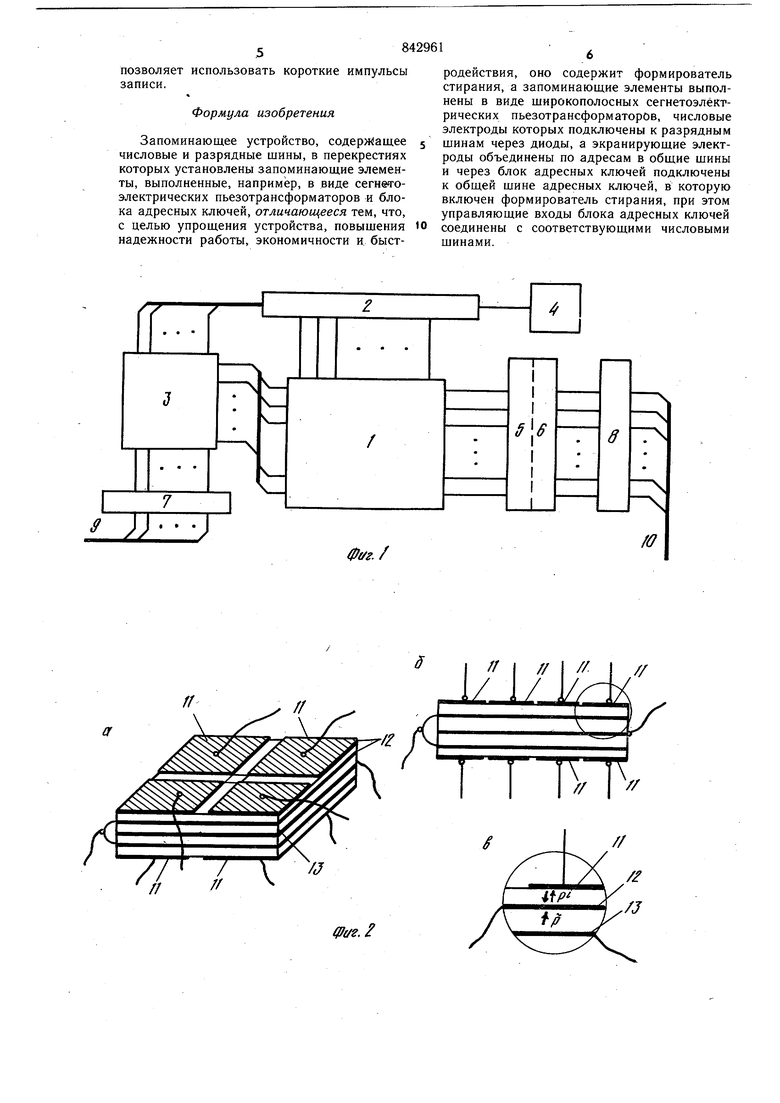

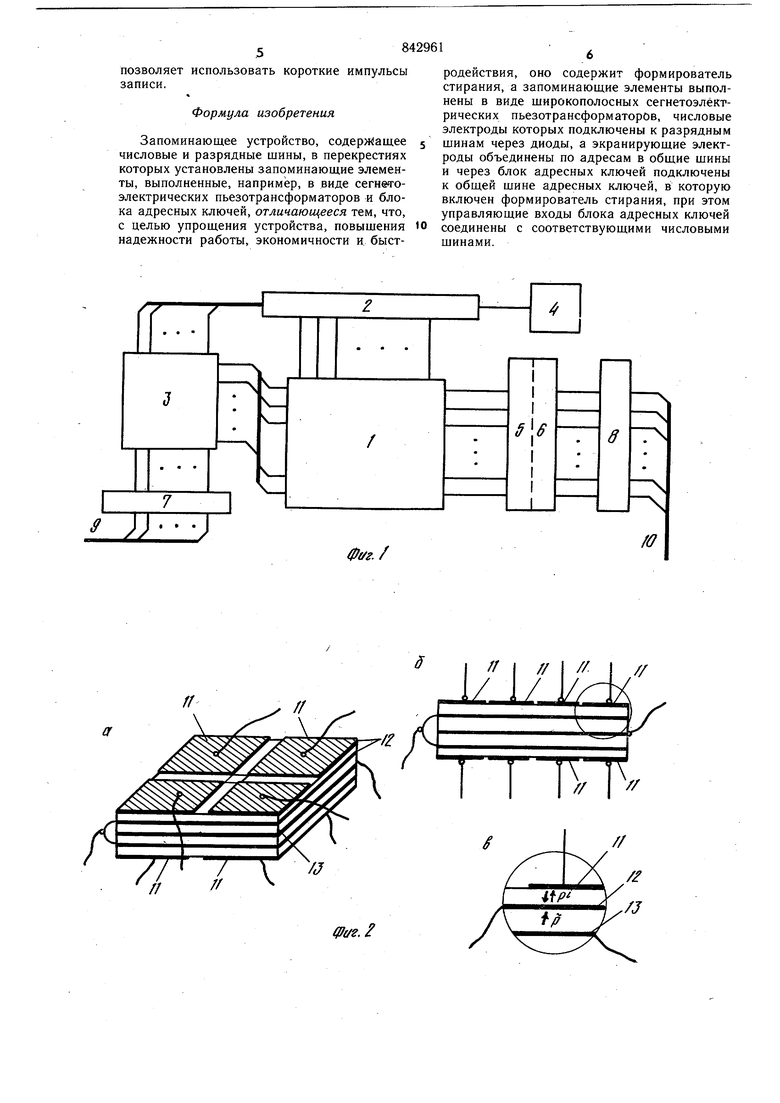

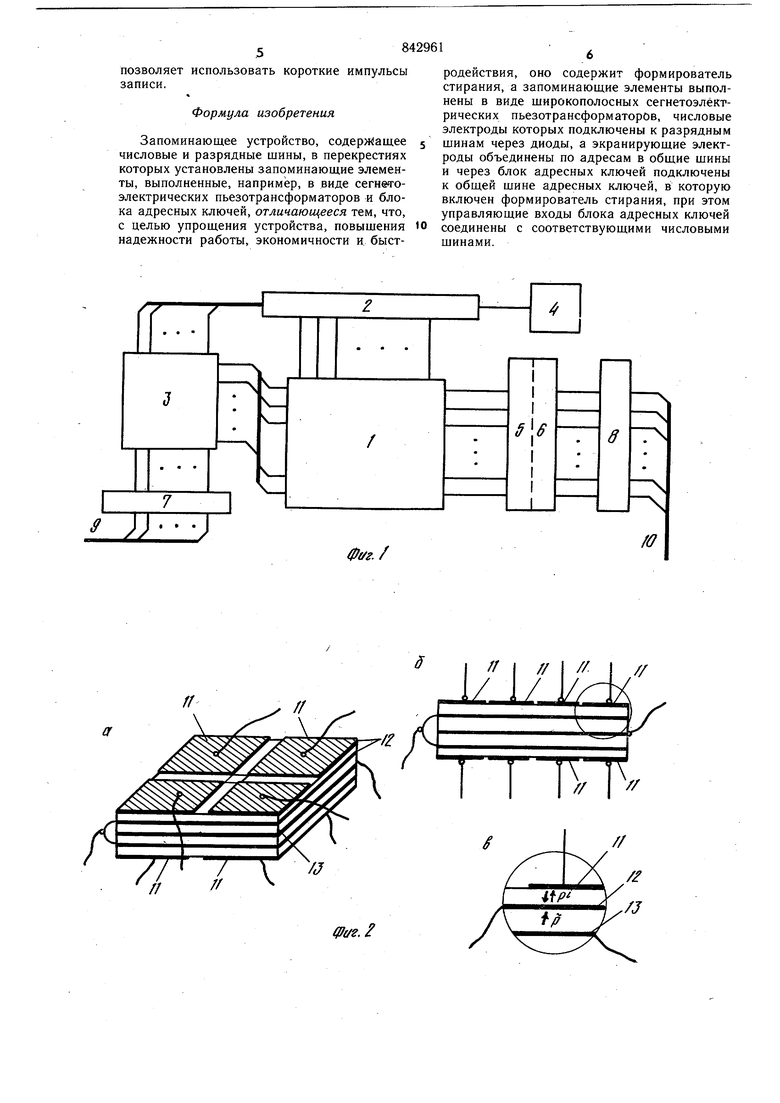

На фиг. 1 показана блок-схема накопителя информации; на фиг. 2 - многослойный широкополосный запоминающий пьезотрансформатор, общий вид и схематическое изображение; на фиг. 3 - принципиальная схема блока запоминающих трансформаторов накопителя; на фиг. 4 - эквивалентные схемы нагрузки и питания запоминающих трансформаторов накопителя в режиме считывания записи.

Накопитель информации (фиг. 1) состоит из блока 1 запоминающих трансформаторов, блока 2 адресных ключей, дешифратора 3 адреса, формирователя 4 стирания, блоков 5 разрядных усилителей и 6 разрядных формирователейи1 - регистра 7 адреса и регистра 8 числа. Ходы чисел принимаются и выдаются по щинам 9 адреса и 10 числа.

Блок запоминающих трансформаторов накопителя (фиг. 3) набран из многослойных

щирокополосных запоминающих пьезотрансформаторов, у которых электроды 11 являются числовыми (выходы трансформатора), электроды 12 экранирующими, а электроды 13 - электродами возбуждения (вход). Блок

1 запоминающих трансформаторов 1 выполт нен в виде числовых шин 14, разрядныхшин 15 и диодов 16 и 17.

Устройство работает следующим образом.

Импульс напряжения, по форме близкий к прямоугольному, приложенный между электродами 12 и 13 широкополосного запоминающего пьезртрансформатора, вызывает упругую деформацию сегнетоматериала пластинчатых секций, сохраняющуюся в течение всего времени его действия. В результате пьезоэффекта механическая деформация преобразуется в импульсное изменение разности потенциалов между электродами 11 и 12. Знак получаемого н выходе импульса напряжения зависит от направления поляризации сегнетоматериала под электродами 11 (фиг. 20) и задается полярностью импульса записи, прикладываемого между электродами 11 и 12.

В режиме считывания код адреса по щине 9 принимается на регистр 7 адреса, соединенный с дешифратором 3. В соответствии с кодом адреса на одном из выходов дешифратора 3 возникает импульс напряжения, поступающий на электроды 13 возбуждения щирокополосных запоминающих пьезотрансформаторов и на открывание соответствующего адресного ключа 2. Адресный ключ через внутреннее сопротивление формирователя 4 стирания гальванически заземляет экранирующие электроды выбранных трансформаторов, а импульсы, возникающие на электродах 11 возбужденных запоминающих пьезотрансформаторов, через диоды 16 и 17 (фиг. 3) блоков запоминающих трансформаторов 1 и разрядных усилителей 5 поступают на регистр 8 числа. Причем на установку триггеров регистра 8 числа поступают лищь импульсы, полярность которых совпадает с направлением включения вентилей (диодов 16 и 17, фиг. 3) т.е. импульсы 1. Импульсы «О (противоположной полярности) значительно ослабляются диодами и триггерами регистра 8 не воспринимаются.

Кроме того, импульсы «1, распространяющиеся по разрядной щине, удерживают вентили (диоды 16, фиг. 3) невыбранных трансформаторов в запертом состоянии, исключая паразитную перегрузку возбужденного (выбранного) запоминающего пьезотрансформатора параллельно включенными выходами остальных трансформаторов. При этом в соответствии с эквивалентной-схемой (фиг. 4а) сопротивление нагрузки запоминающего трансформатора-генератора импульсов «1 в одном разряде составляет

RH (

экв

R

«..

R -входное сопротивление разрядного усилителя;

RdnR -соответственно

сопротивления

запертого диода 16 и закрытого ключа 2.

Принцип разделения выходов запоминающих трансформаторов вентилями (диодами) позволяет строить быстродействующие накопители объемом бит информации. В режиме очистки (стирание информации записью «О по всем адресам одновременно) формирователь 4 стирания, подключенный к общей щйне 18 адресных ключей, генерирует импульс напряжения. Длительность импульса выбрана такой, чтобы напряжение между электродами 11 и 12 достигало начального напряжения формирователя 4. При этом величина обратного сопротивления КэиК соответственно диодов 16 и закрытых адресных ключей 2 существенного влияния на процесс переполяризации сегнетоматериала не оказывают. По окончании импульса очистки (независимо от прежнего) во всех запоминающих трансформаторах записан нулевой код.

в режиме записи кода адресная часть накопителя, включающая регистр адреса 7,

дешифратор 8 и блок 2 адресных ключей работают так же, как и в режиме считывания.

В соответствии с кодом на регистре 8 числа возбуждаются однополярные разрядные формирователи 1, генерирующие одиночные короткие (10с) импульсы записи. Амплитуда импульсного напряжения записи «1 между электродами 11 и 12 выбранного трансформатора .(фиг. 46) выражается формулой Uj пе|()

0 где гэ -соответственно сопротивления открытых диодов адресного ключа;

Х7ф -импульсное напряжение разрядного формирователя; f-nef- импульс тока при переключении (переполяризации) одного трансформатора.

Напряжение на выбранных трансформаторах в соответствии с эквивалентной схемой (фиг. 46) определяется, как

uiioM - uip - «-пер cra RO

где Я 4-сопротивление закрытого ключа 2. При R., г. всегда U,..- Ui.

Г- , J

Разделяющие вентили (диоды) исключают ложную запись «О под действием импульса записи «1 в ранее записанный код по другому адресу через конструкторскую 5 емкость выхода запоминающего трансформатора, подключенного к тому же адресному ключу (фиг. 46). Амплитуда ложного сигнала составляет

пом ((pa -t-Ra Хтр)

® где Rj -сопротивление запертого диода;

Х-гр -эквивалентное емкостное сопротив ление промежутка между электродами 11 и 12 для импульса записи «1,

5 Кроме того, разделяющие вентили способствуют повышению надежности и быстродействия записи, увеличения постоянную времени разряда конструктивной емкости выхода запоминающего трансформатора. Это

позволяет использовать короткие импульсы записи.

«

Формула изобретения

Запоминающее устройство, содер йащее числовые и разрядные шины, в перекрестиях которых установлены запоминающие элементы, выполненные, например, в виде сегнетоэлектрических пьезотрансформаторов и блока адресных ключей, отличающееся тем, что, с целью упрощения устройства, повышения надежности работы, экономичности и быстродействия, оно содержит формирователь стирания, а запоминающие элементы выполнены в виде широкополосных сегнетоэлёктрических пьезотрансформаторов, числовые электроды которых подключены к разрядным шинам через диоды, а экранирующие электроды объединены по адресам в общие шины и через блок адресных ключей подключены к общей шине адресных ключей, в которую включен формирователь стирания, при этом управляющие входы блока адресных ключей соединены с соответствующими числовыми шинами.

в

га

Фиг./

/

Р(/г.2

I // I // I // I //

i/J / 1/ях

II IVT

//

/

х

4f/p

/J

tf у

Авторы

Даты

1981-06-30—Публикация

1968-06-17—Подача