Изобретение относится к области запоминающих устройств. Известно ассоциативное запоминающее устройство (АЗУ), содержащее запоминающие магнитные элементы и блоки управления 1. Недостатком этого устройства являются ограниченные функциональные возможности. Наиболее близким техническим решением к изобретению является АЗУ, содержащее строки и столбцы элементо ассоциативной памяти, каждый из которых содержит запоминающую ячейку, блок считывания, блок сравнения, две группы блоков выдачи, три группы вхо ных элементов НЕ, группу элементов И-НЕ для разрешения выбора строк, ло гические блоки на каждый столбец, со держащие в себе два элемента И-НЕ и элемент НЕ, два элемента И-НЕ для выбора режима работы, а также входные шины режимов чтения, записи, поиска, информационные и маскирующие шины, шины выбора строки, входные шины считывания слова и шины результата поиска С21. Недостатком этого устройства является невозможность разделения матрицы ассоциативных элементов памяти на группы и отсутствие тактируемого си(- нала обращения к АЗУ, в результате чего снижается надежность устройства. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в АЗУ, содержащее матрицу ассоциативных элементов памяти, группы элементов И-НЕ, элементы НЕ и элементы И-НЕ, выходы которых подключены ко входам шин выбора строк матрицы ассоциативных элементов памяти, а выходы элементов И-НЕ группы - ко входам шин считывания, причем первые входы одних из элементов И-НЕ группы соединены со входами элементов НЕ, а первые входы других элементов И-НЕ группы - с выходами элементов НЕ,

390

первые входы элементов И-НЕ, входы элементов НЕ и вторые входы элементов И-НЕ групп являются соответственно адресными, информационными и маскирующими входами устройства, введены логические блоки, элемент ИЛИ-НЕ и элементы И, выходы которых подключены ко входам элемента ИЛИ-НЕ, выход которого соединен со вторыми входами элементов И-НЕ, первые и вторые входы логических блоков подключены соответственно к первым входам элементов И, а выходы - к третьим входам элементов И-НЕ групп, вторые входы элементов И, третьи и четаертые входь логических блоков являются управляющими входами устройства.

При этом каждый логический блок целесообразно выполнить содержащим элементы И и элемент ИЛИ-НЕ, входы которого подклю14ены соответственно к выходам элементов И, а выход является выходом логического блока, входами которого с первого по четвертый являются соответственно вход пер врго элемента И, первый и второй входы второго и вход третьего элементов И.

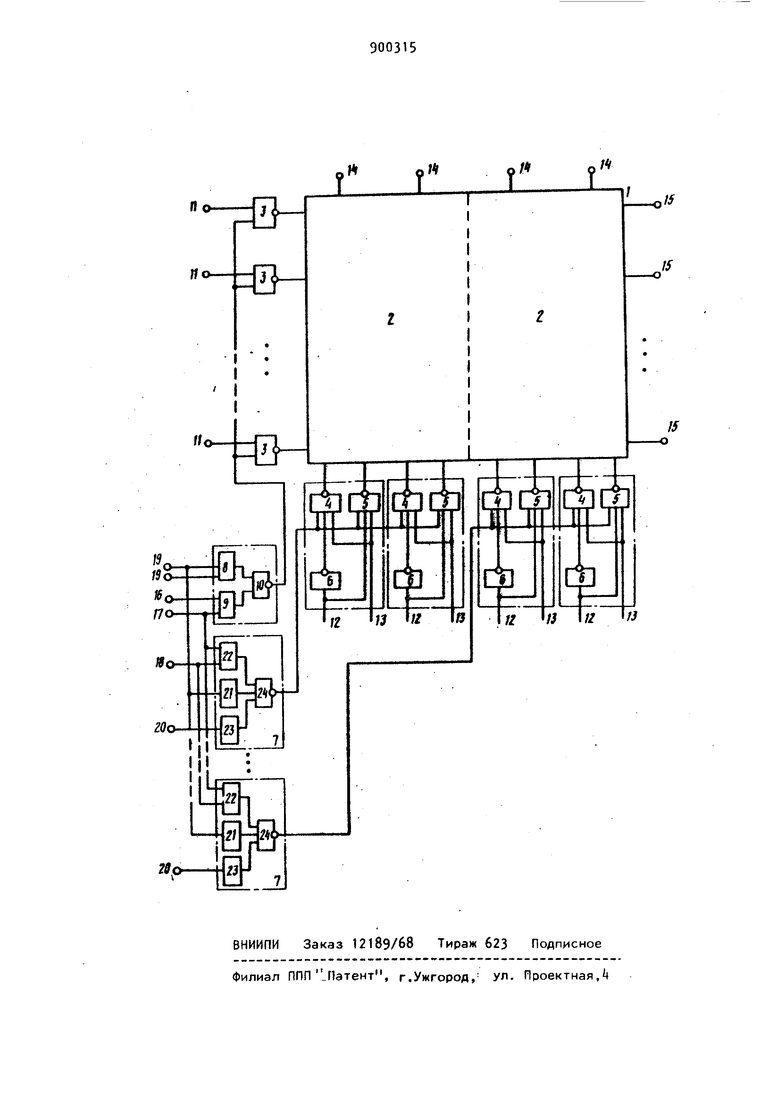

.На чертеже изображена структурная рхема предложенного устройства.

Устройство содержит матрицу Т ассоциативных элементов 2 памяти, элементы И-НЕ 3, группы элементов И-НС и 5, элементы НЕ 6, логические блоки 7 , первый 8 и второй 9 элементы И и элемент ИЛИ-НЕ 10. На чертеже обозначены адресные 11, информационные tZ и маскирующие 13 входы, информационные выходы И и выходы 15 результата опроса, входы чтения 16, записи 17, опроса 18, обращения 19 и выбора 20 ассоциативных элементов памяти устройства.

Выходы элементов И 8 и 9 подключены ко входам элемента ИЛИ-ИЕ 10, выход которого соединен со вторыми входами элементов И-НЕ 3. Первые и вторые входа логических блоков 7 . подключены соответственно к входам первого В и /второго 9 элементов И, а выходы - к третьим входам элементов И-НЕ и 5 групп.

Входы элементов И 8 и 9, третьи и четвертые входы блоков 7 являются соответственно входами обращения 19., чтения 16, записи 17, опроса 18 и выбора 20 ассоциативных элементов памйти устройства. При этом логический

54

блок 7 выполнен содержащим элементы И 21-23, выходы которых подключены соответственно ко входам элемента ИЛИ-НЕ 24, выход которого являетс выходом блока 7. Вход первого элемента И 21, первый и второй входы второго 22 и вход третьего 23 элементов И являются соответственно входами с первого по четвертый блока 7.

Устройство работает следующим образом.

Во всех режимах работы (запись, чтение, опрос) сигнал обращения осуществляет общую синхронизацию работы устройства, поэтому уровень логического О на вход 19 обращения приходит после подачи сигналов информации и маски на входы 12 и 13 и управляющих сигналов режимов работы. Таким образом, сигнал обращения приходит последним и снимается первым. При отсутствии сигнала обращения поле ассоциативной памяти находится в состоянии покоя, т.е. на всех входах матрицы присутствует уровень логической 1. В работе устройства активным считается уровень логического 0

В режиме чтения уровень логического О на входах чтения 16 и обращения 19 разрешает выбор адреса строки матрицы 1 ассоциативных элементов памяти. Композиция значений на входах логических блоков 7 (логическая Ч на входах опроса 18 и записи 17) такова, что с выходов этих блоков 7 поступает уровень логического О, который запрещает прохождение сигналов информации и маски и обеспечивает уровень логической 1 на информационных и маскирующих входах матри1|ы 1.

В режиме записи уровень логического О на входах записи 17 и обращения 19, так же как при чтении, разрешает выбор адреса строки.

Однако запись в любую группу или несколько групп ассоциативных элементов памяти по одной или нескольким выбранным строкам матрицы 1 осуществляется подачей сигнала логического О по соответствующему входу 20. Приэтом по входу 17 записи подается сигнал логического О на первые входы элементов И 22, а на вторые входы - сигнал логической 1 со входа 18 опроса, так как одновременно не могут быть установлены два режима работы устройства. На

59

входы элементов И 21 поступает сигнал логического О со входа 19. При этом на выходах элементов И 2123 выбранного блока 7 установятся сигналы логического О, а на выходе элемента ИЛИ-НЕ 2k - сигнал логической 1, который подается на третьи входы элементов И 4 и 5 групп соответствующей выбранным ассоциативным элементам памяти матрицы 1, и разрешает запись информации в выбранные элементы 2.

На входе 20 не выбранного блока 7 присутствует сигнал логической 1, и с выхода элемента ИЛИ-НЕ 2 этого блока 7 снимается сигнал логического О, который блокирует информационные 12 и маскирующие 13 входы, ссютветствующие не выбранным ассоциативным элементам 2 памяти матрицы 1, исключая таким образом ложную запись информации.

8опросе чтения комбинация сигналов логических 1 на входах 16 и 17 блокирует выбор по входам 11. Выбор ассоциативных элементов 2 памяти матрицы 1 для считывания из них информации происходит так же,как в режиме записи.

Технико-экономическое преииув1ество предложенного устройства заключается в его более широких, по сравнению с известным, функциональных возможностях за счет выполнения в нем логических операций, обеспечиваемых путем возможного разделения матрицы на группы ассоциативных элементов памяти и введения тактируемого сигнала обращения к устройству.

Формула изобретения

1. Ассоциативное запоминающее устройство, содержащее матрицу ассоциативных элементов памяти, группы ; лементов И-НЕ, элементы НЕ и элементы

56

И-НЕ, выходы которых подключены ко входам шин выбора строк матрицы ассоциативных элементов памяти, и выходы элементов И-НЕ группы - ко входам шин считывания, причем первые входы одних их элементов И-Н1 группы соединены со входами элементов НЕ, а первые входы других элементов И-НЕ группы с выходами элементов НЕ, первые входы элементов И-НЕ, входы элементов НЕ и вторые входы элементов И-НЕ групп являются соответственно адресными, информационными и маскирующими входами устройства, отличающеес я тем, что, с целью повышения надежности устройства, оно содержит логические блоки, элемент ИЛИ-НЕ и элемент И, выходы которых подключены ко входам элемента ИЛИ-НЕ, выход которого соединен со вторыми входами элементов И-НЕ, первые и вторые входы логических блоков подключены соответственно к первым входам элементов И, а выходы - к третьим входам элементов И-НЕ групп, вторые входы элементов И, третьи и четвёртые входы логических блоков являются управляющими входами устройства.

2. Устройство по п, 1, о т л и чающееся тем, что каждый логический блок содержит элементы И и элемент И/Ж-НЕ, входы которого подкхточены соответственно .к выходам элементов И, а выход является выходом логического блока, входами которого с первого по четвертый являются соответственно вход первого элемента И, первый и второй входы второго и вход третьего элементов И.

Источники информации, принятые во внимание при экспертизе

1.Заявка Японии tf 52-7903, кл 97(7)С, опублик. 19752.Авторское свидетельство СССР по заявке 28Г П9/18-2,

кл. СП С 15/00, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1979 |

|

SU842962A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Ассоциативное запоминающее устройство | 1984 |

|

SU1277210A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU898504A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU903983A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1785039A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1999 |

|

RU2168216C2 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

Авторы

Даты

1982-01-23—Публикация

1980-05-28—Подача