(54) АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU903983A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU900315A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU842962A1 |

| Запоминающее устройство | 1985 |

|

SU1295456A1 |

| Ассоциативная запоминающая матрица | 1981 |

|

SU1005188A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU898504A1 |

| Накопитель для ассоциативного запоминающего устройства | 1982 |

|

SU1023396A1 |

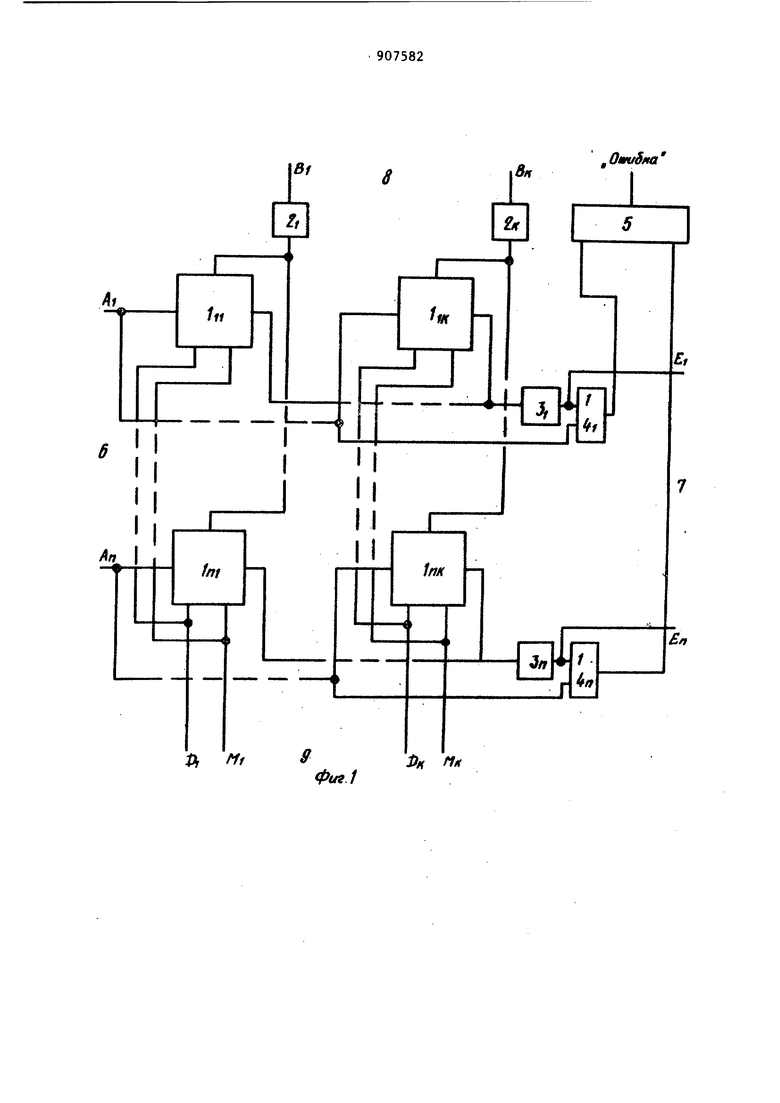

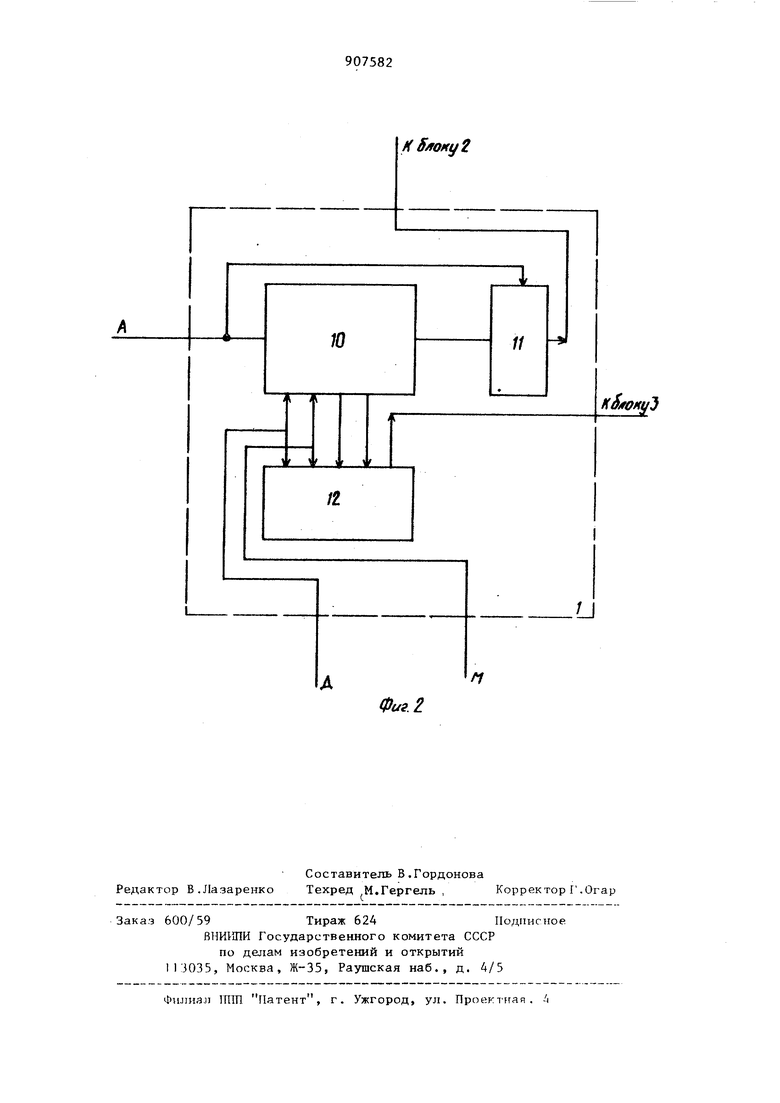

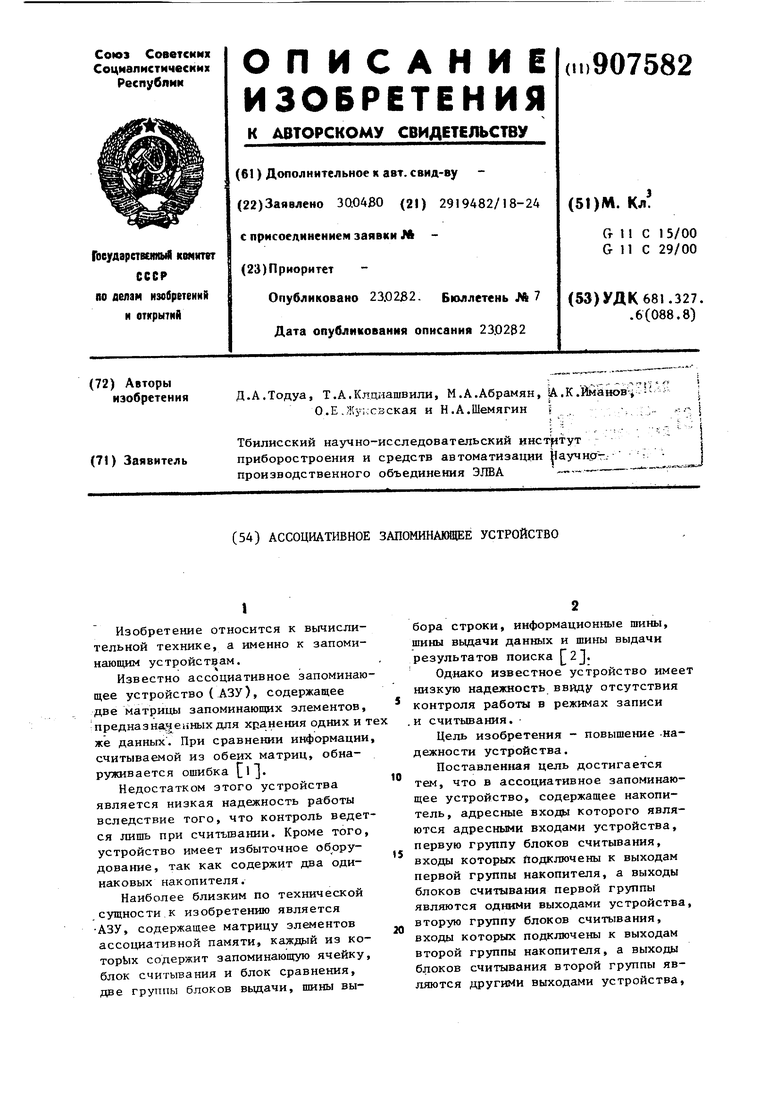

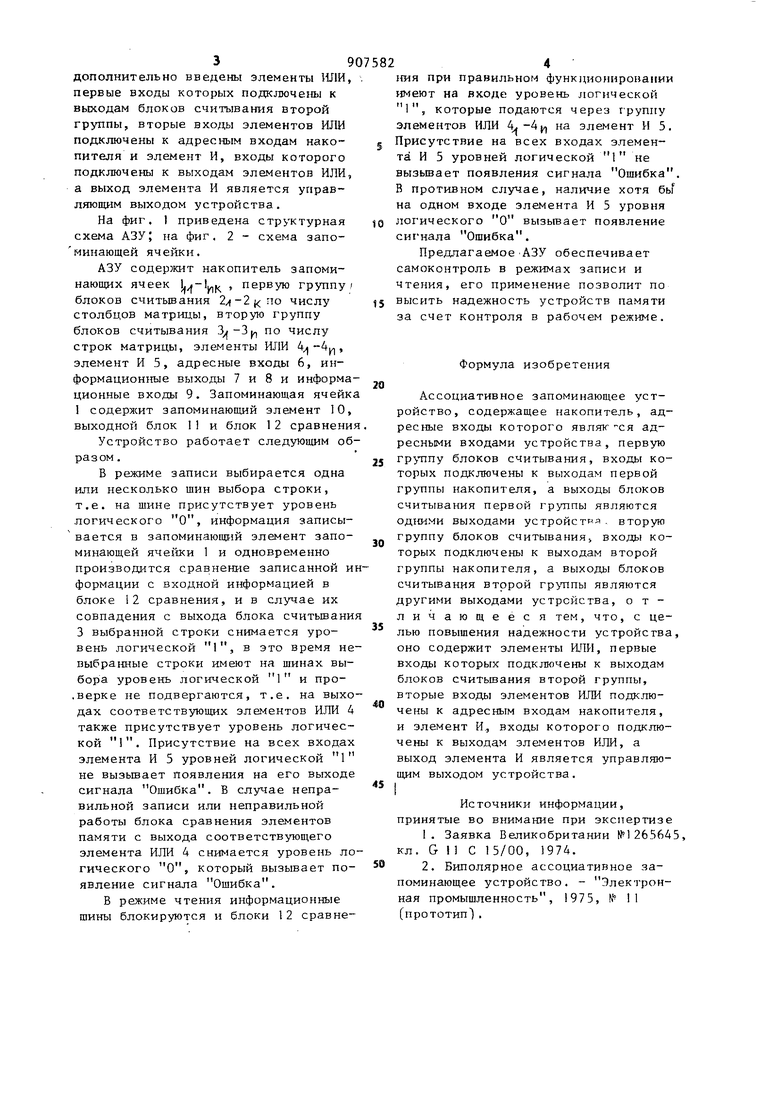

Изобретение относится к вьмислительной технике, а именно к запоминающим устройствам. Известно ассоциативное запоминаю щее устройство (АЗУ), содержащее две матрицы запоминающих элементов предназначенных для хранения одних и же данных. При сравнении информации считываемой из обеих матриц, обнаруживается ошибка ul Недостатком этого устройства является низкая надежность работы вследствие того, что контроль ведет ся лишь при счи1ъшании. Кроме того устройство имеет избыточное оборудование, так как содержит два одинаковых накопителя. Наиболее близким по технической сущности к изобретению является АЗУ, содержащее матрицу элементов ассоциативной памяти, каждаш из коTopkx содержит запоминающую ячейку блок считывания и блок сравнения, две группы блоков вьщачи, шины выбора строки, информационные шины, шины выдачи данных и шины выдачи результатов поиска r2j. Однако известное устройство имеет низкую надежность ввиду отсутствия контроля работы в режимах записи и считывания. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в ассоциативное запоминающее устройство, содержащее накопитель, адресные входы которого являются адресными входами устройства, первую группу блоков считывания, входы которых йодключены к выходам первой группы накопителя, а выходы блоков считывания первой группы являются одними выходами устройства, вторую группу блоков считывания, входы которых подключены к выходам второй группы накопителя, а выходы блоков считывания второй группы являются другими выходами устройства, 39 дополнительно введены элементы 11Г1И, первые входы которых noflKjB04enbi к выходам блоков считывания второй группы, вторые входы элементов ИЛИ подключены к адресным входам накопителя и элемент И, входы которого подключены к выходам элементов ИЛИ, а выход элемента И является управляющим выходом устройства. На фиг. 1 приведена структурная схема АЗУ; на фиг, 2 - схема запоминающей ячейки. АЗУ содержит накопитель запоминающих ячеек 1. , первую группу блоков считьшания 2/f-2«rTo числу столбцов матрицы, вторую группу блоков считывания по числу строк матрицы, элементы ИЛИ , элемент И 5, адресные входы 6, информационные выходы 7 и 8 и информа ционные входы 9. Запоминающая ячейк 1 содержит запоминающий элемент 10, выходной блок II и блок 12 сравнени Устройство работает следующим об разом. В режиме записи выбирается одна или несколько шин выбора строки, т.е. на шине присутствует уровень логического О, информация запись вается в запоминающий элемент запоминающей ячейки 1 и одновременно производится сравнение записанной и формации с входной информацией в блоке 12 сравнения, и в случае их совпадения с выхода блока считьшани 3 выбранной строки снимается уровень логической 1, в это время не выбра {ные строки имеют на шинах выбора уровень логической 1 и про.верке не подвергаются, т.е. на выхо дах соответствующих элементов ИЛИ 4 также присутствует уровень логической . Присутствие на всех входах элемента И 5 уровней логической 1 не вызьшает появления на его выходе сигнала Ошибка. В случае неправильной записи или неправильной работы блока сравнения элементов памяти с выхода соответствующего элемента ИЛИ 4 снимается уровень ло гического О, который вызывает появление сигнала Ошибка. В режиме чтения информационные шины блокируются и блоки 12 сравне1ШЯ при правильном функционировании имеют на входе уровень логической 1, которые подаются через группу элементов ИЛИ ) на элемент И 5. Присутствие на всех входах элемента И 5 уровней логической 1 не вызывает появления сигнала Ошибка. В противном случае, наличие хотя бы на одном входе элемента И 5 уровня логического О вызьгеает появление сигнала Ошибка. ПредлагаемоеАЗУ обеспечивает самоконтроль в режимах записи и чтения, его применение позволит по высить надежность устройств памяти за счет контроля в рабочем режиме. Формула изобретения Ассоциативное запоминающее устройство, содержащее накопитель, адресные входы которого являг ся адресными входами устройства, первую группу блоков считывания, входы которых подключены к в 1ходам первой группы накопителя, а выходы блоков считывания первой группы являются одними выходами устройств. вторую группу блоков считывания; входы которых подключены к выходам второй группы накопителя, а выходы блоков считывания второй являются другими выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит элементы ИЛИ, первые входы которых подключены к выходам блоков считьшания второй группы, вторые входы элементов ИЛИ подключены к адресным входам накопителя, и элемент И., входы которого подключены к выходам элементов ИЛИ, а выход элемента И является управляюш м выходом устройства. Источники информации, принятые во внимание при экспертизе 1.Заявка Великобритании №1265645, кл. G 11 С 15/00, 1974. 2.Биполярное ассоциативное запоминающее устройство. - Электронная промышленность, 1975, № 11 прототип.

Bf

A fff фиг f

,Лис/Л

Bff

Дг ff

/О

м а

А

Н 8/юку2

7/

к5/юнуЪ

Фиг. 2

Авторы

Даты

1982-02-23—Публикация

1980-04-30—Подача