Изобретение относится к области вычислительной техники и может быть использовано при построении систем контроля и

диагностики последовательностных узлов. Цель изобретения - расширение области применения за счет возможности создания тестов для контроля последовательност- ных узлов.

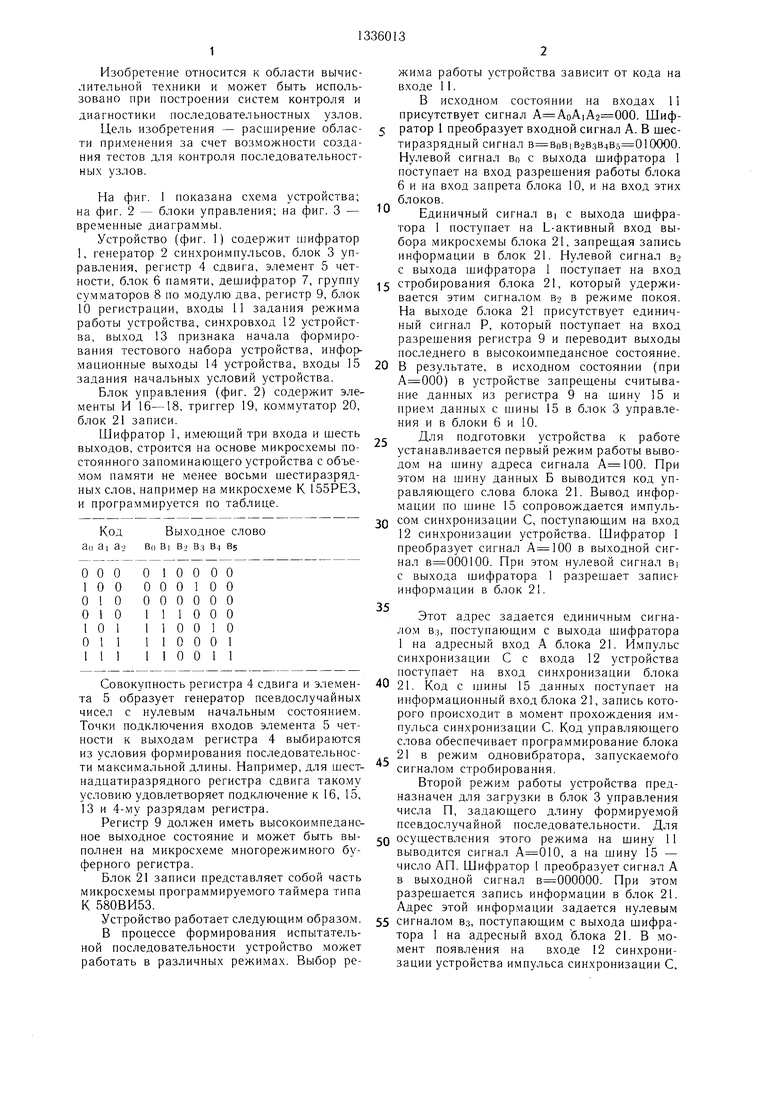

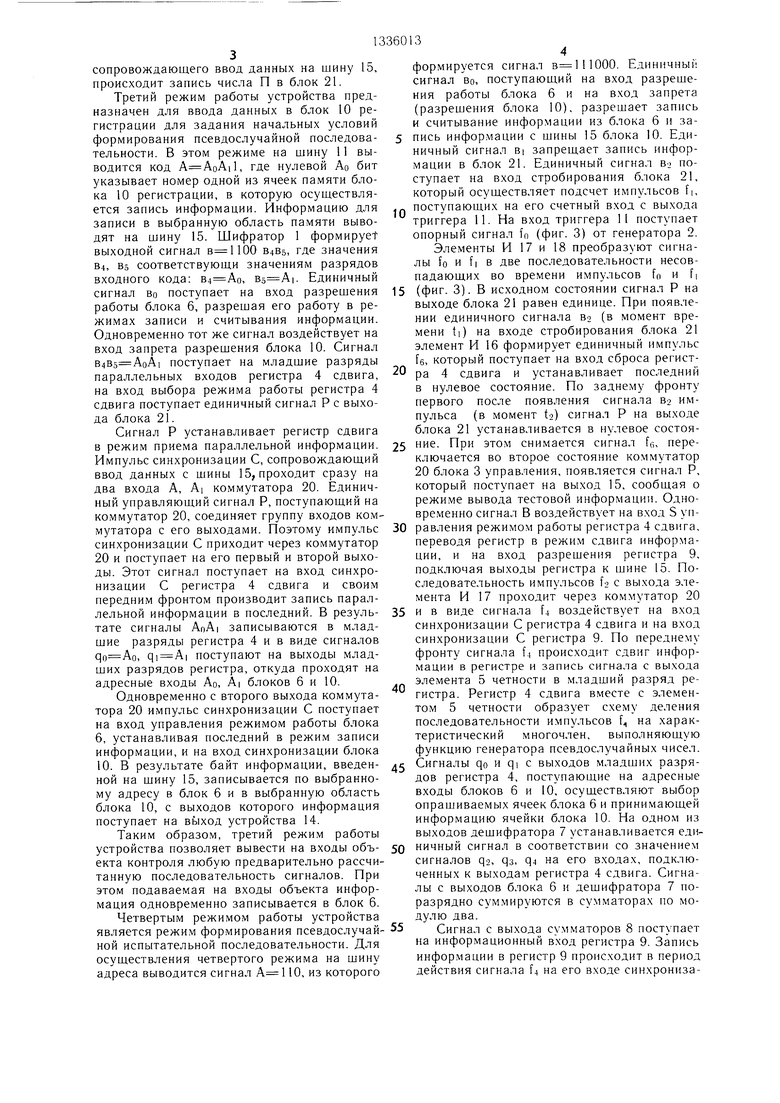

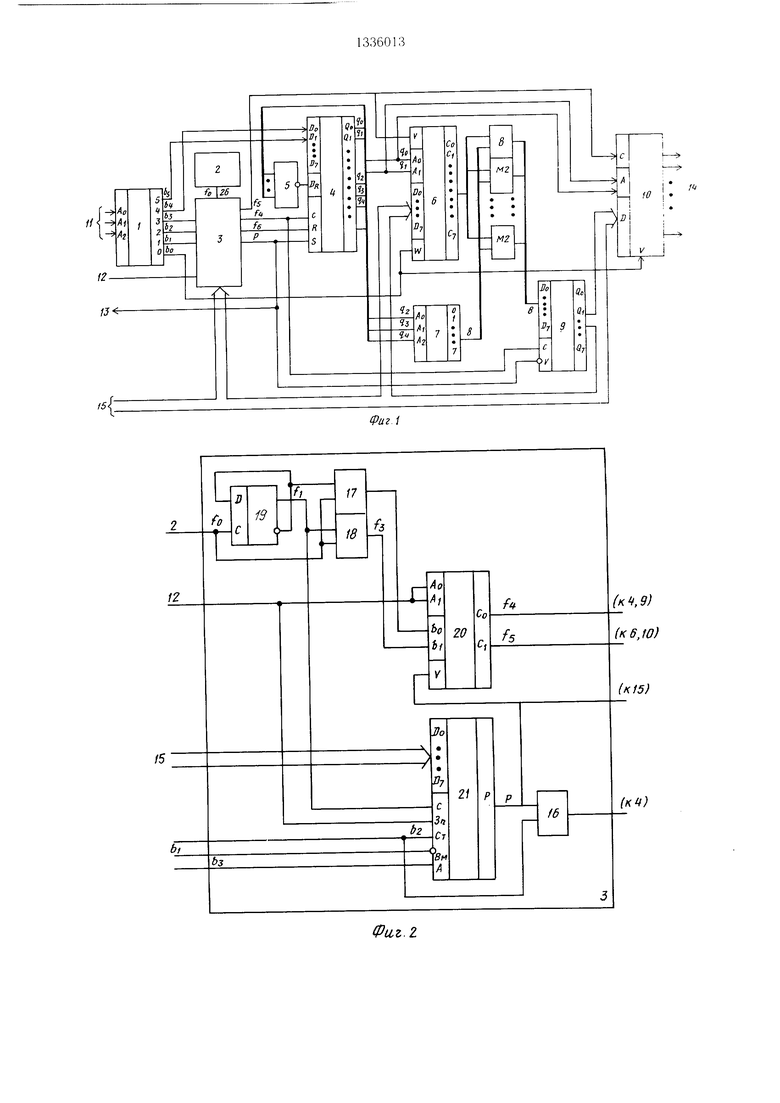

На фиг. 1 показана схема устройства; на фиг. 2 - блоки управления; на фиг. 3 - временные диаграммы.

Устройство (фиг. 1) содержит шифратор 1, генератор 2 синхроимпульсов, блок 3 управления, регистр 4 сдвига, элемент 5 четности, блок 6 памяти, дешифратор 7, группу сумматоров 8 по модулю два, регистр 9, блок 10 регистрации, входы 11 задания режима работы устройства, синхровход 12 устройства, выход 13 признака начала формирования тестового набора устройства, информационные выходы 14 устройства, входы 15 задания начальных условий устройства.

Блок управления (фиг. 2) содержит элементы И 16-18, триггер 19, коммутатор 20, блок 21 записи.

Шифратор 1, имеюпдий три входа и шесть выходов, строится на основе микросхемы постоянного запоминаюш.его устройства с объемом памяти не менее восьми шестиразрядных слов, например на микросхеме К 155РЕЗ, и программируется по таблице.

Совокупность регистра 4 сдвига и элемента 5 образует генератор псевдослучайных чисел с нулевым начальным состоянием. Точки подключения входов элемента 5 четности к выходам регистра 4 выбираются из условия формирования последовательности максимальной длины. Например, для шестнадцатиразрядного регистра сдвига такому условию удовлетворяет подключение к 16, 15, 13 и 4-му разрядам регистра.

Регистр 9 должен иметь высокоимпеданс- ное выходное состояние и может быть выполнен на микросхеме многорежимного буферного регистра.

Блок 21 записи представляет собой часть микросхемы программируемого таймера типа К 580ВИ53.

Устройство работает следующим образом.

В процессе формирования испытательной последовательности устройство может работать в различных режимах. Выбор режима работы устройства зависит от кода на входе 11.

В исходном состоянии на входах 11 присутствует сигнал А :АоА|А2 000. Шифратор 1 преобразует входной сигнал А. В шестиразрядный сигнал в воВ1В2ВзВ4В5 010000. Нулевой сигнал во с выхода шифратора 1 поступает на вход разрешения работы блока 6 и на вход запрета блока 10, и на вход этих блоков.

Единичный сигнал В| с выхода шифратора 1 поступает на L-активный вход выбора микросхемы блока 21, запрещая запись информации в блок 21. Нулевой сигнал во с выхода шифратора 1 поступает на вход

5 стробирования блока 21, который удерживается этим сигналом В9 в режиме покоя. На выходе блока 21 присутствует единичный сигнал Р, который поступает на вход разрешения регистра 9 и переводит выходы последнего в высокоимпедансное состояние.

0 В результате, в исходном состоянии (при ) в устройстве запрещены считывание данных из регистра 9 на шину 15 и прием данных с шины 15 в блок 3 управления и в блоки 6 и 10.

5 Для подготовки устройства к работе устанавливается первый режим работы выводом на шину адреса сигнала . При этом на шину данных Б выводится код уп- равляюшего слова блока 21. Вывод информации по шине 15 сопровождается импульQ сом синхронизации С, поступающим на вход 12 синхронизации устройства. Шифратор 1 преобразует сигнал в выходной сигнал в ОООЮО. При этом нулевой сигнал в: с выхода шифратора 1 разрешает запись информации в блок 21.

5 „

Этот адрес задается единичным сигналом B:J, поступаюпхим с выхода шифратора 1 на адресный вход А блока 21. Импульс синхронизации С с входа 12 устройства поступает на вход синхронизации блока

0 21. Код с шины 15 данных поступает на информационный вход блока 21, запись которого происходит в момент прохождения импульса синхронизации С. Код управляюшего слова обеспечивает програ.ммирование блока г 21 в режим одновибратора, запускаемого сигналом стробирования.

Второй режим работы устройства предназначен для загрузки в блок 3 управления числа П, задающего длину формируемой псевдослучайной последовательности. Для

0 осуществления этого режима на шину И выводится сигнал , а на шину 15 - число АП. Шифратор 1 преобразует сигнал А в выходной сигнал в 000000. При этом разрешается запись информации в блок 21. Адрес этой информации задается нулевым

5 сигналом вз, поступающим с выхода шифратора 1 на адресный вход блока 21. В момент появления на входе 12 синхронизации устройства импульса синхронизации С,

сопровождающего ввод данных на шину 15, происходит запись числа П в блок 21.

Третий режим работы устройства предназначен для ввода данных в блок 10 регистрации для задания начальных условий формирования псевдослучайной последова- тельности. В этом режиме на шину 11 выводится код A: AoAil, где нулевой АО бит указывает номер одной из ячеек памяти блока 10 регистрации, в которую осуш,ествля- ется запись информации. Информацию для записи в выбранную область памяти выводят на шину 15. Шифратор 1 формирует выходной сигнал В4В.5, где значения В4, вз соответствуюш,и значениям разрядов входного кода: , . Единичный сигнал Во поступает на вход разрешения работы блока б, разрешая его работу в режимах записи и считывания информации. Одновременно тот же сигнал воздействует на вход запрета разрешения блока 10. Сигнал поступает на младшие разряды параллельных входов регистра 4 сдвига, на вход выбора режима работы регистра 4 сдвига поступает единичный сигнал Р с выхода блока 21.

Сигнал Р устанавливает регистр сдвига в режим приема параллельной информации. Импульс синхронизации С, сопровождающий ввод данных с шины 15, проходит сразу на два входа А, AI коммутатора 20. Единичный управляющий сигнал Р, поступающий на коммутатор 20, соединяет группу входов коммутатора с его выходами. Поэтому импульс синхронизации С приходит через коммутатор 20 и поступает на его первый и второй выходы. Этот сигнал поступает на вход синхронизации С регистра 4 сдвига и своим передним фронтом производит запись параллельной информации в последний. В резуль- тате сигналы АпА| записываются в младшие разряды регистра 4 и в виде сигналов , поступают на выходы младших разрядов регистра, откуда проходят на адресные входы АО, AI блоков 6 и 10.

Одновременно с второго выхода коммутатора 20 импульс синхронизации С поступает на вход управления режимом работы блока 6, устанавливая последний в режим записи информации, и на вход синхронизации блока 10. В результате байт информации, введен- ной на шину 15, записывается по выбранному адресу в блок бив выбранную область блока 10, с выходов которого информация поступает на вьиод устройства 14.

Таким образом, третий режим работы устройства позволяет вывести на входы объ- екта контроля любую предварительно рассчитанную последовательность сигналов. При этом подаваемая на входы объекта информация одновременно записывается в блок 6.

Четвертым режимом работы устройства является режим формирования псевдослучай- ной испытательной последовательности. Для осуществления четвертого режима на шину адреса выводится сигнал А 110, из которого

0

д 5

5 0

формируется сигнал в 111000. Единичный сигнал Во, поступающий на вход разрешения работы блока 6 и на вход запрета (разрешения блока 10), разрешает запись и считывание информации из блока 6 и запись информации с шины 15 блока 10. Единичный сигнал В запрещает запись информации в блок 21. Единичный сигнал во поступает на вход стробирования блока 21, который осуществляет подсчет импульсов f|, поступающих на его счетный вход с выхода триггера 11. На вход триггера И поступает опорный сигнал fo (фиг. 3) от генератора 2.

Элементы И 17 и 18 преобразуют сигналы fo и f| в две последовательности несовпадающих во времени импульсов fn и f| (фиг. 3). В исходном состоянии сигнал Р на выходе блока 21 равен единице. При появлении единичного сигнала во (в момент времени ti) на входе стробирования блока 21 элемент И 16 формирует единичный импульс fe, который поступает на вход сброса регистра 4 сдвига и устанавливает последний в нулевое состояние. По заднему фронту первого после появления сигнала В2 импульса (в момент to) сигнал Р на выходе блока 21 устанавливается в нулевое состояние. При этом снимается сигнал fa, переключается во второе состояние коммутатор 20 блока 3 управления, появляется сигнал Р, который поступает на выход 15, сообщая о режиме вывода тестовой информации. Одновременно сигнал В воздействует на вход S управления режимом работы регистра 4 сдвига, переводя регистр в режим сдвига информации, и на вход разрещения регистра 9, подключая выходы регистра к шине 15. Последовательность импульсов fa с выхода элемента И 17 проходит через коммутатор 20 и в виде сигнала f4 воздействует на вход синхронизации С регистра 4 сдвига и на вход синхронизации С регистра 9. По переднему фронту сигнала f4 происходит сдвиг информации в регистре и запись сигнала с выхода элемента 5 четности в младший разряд регистра. Регистр 4 сдвига вместе с элементом 5 четности образует схему деления последовательности импульсов f., на характеристический многочлен, выполняющую функцию генератора псевдослучайных чисел. Сигналы qo и qi с выходов младших разрядов регистра 4, поступающие на адресные входы блоков 6 и 10, осуществляют выбор опрашиваемых ячеек блока 6 и принимающей информацию ячейки блока 10. На одном из выходов дещифратора 7 устанавливается единичный сигнал в соответствии со значением сигналов Qo, Яз, 44 на его входах, подключенных к выходам регистра 4 сдвига. Сигналы с выходов блока 6 и дешифратора 7 поразрядно суммируются в сумматорах по модулю два.

Сигнал с выхода сумматоров 8 поступает на информационный вход регистра 9. Запись информации в регистр 9 проис.ходит в период действия сигнала f4 на его входе синхрониза

ции с. С выхода регистра 9 информация поступает на шину 15 и в момент появления сигнала синхронизации записывается в выбранные ранее ячейки блока 6 и область блока 10. Сигнал з, образованный коммутатором 20 из последовательности импульсов f.-j с выхода элемента И 13, задержан относительно сигнала f для надежной записи информации в блок 6. Формирование каждого нового псевдослучайного числа в регистре 4, считывание информации их ячеек блока 6, инвертирвание одного из битов сигнала на выходе блока 6 и запись информации в выбранные ячейки блоков 6 и 10 происходят периодически с появлением каждого нового импульса fi до тех пор, пока блок 21 не отсчитает записанного в него ранее числа импульсов П. После п циклов формирвания псевдослучайной испытательной последовательности блок 21 формирует сигнал Р, в результате чего прекращаются считывание и запись информации в блок 6, прекращают прием информации блоки 10, переходит в вы- сокоимпедансное состояние выход регистра 9, снимается сигнал 13.

Таким образом, в четвертом режиме работы устройства происходит формирование псевдослучайной испытательной последо- вательности на входах объекта, причем последовательность имеет заданную длину П, в каждом такте формирования происходит изменение только одного бита последовательности и формирование последовательности начинается с записанных ранее в блок 10 начальных значений.

Предлагаемое устройство позволяет сформировать на входах объекта любую наперед заданную испытательную последовательность как комбинацию детерминированных тестовых воздействий и псевдослучайных нос ледовательностей различной длины с различными начальными условиями. При этом в каждом такте формирования псевдослучайного воздействия изменяется только один бит испытательного сигнала, за счет чего исклю- чаются состязания внутри объекта контроля, вызванные одновременным изменением сигналов на различных входах. Следовательно, формируемая устройством испытательная последовательность может быть использована для контроля и диагностики объектов, содержащих элементь памяти и внутренние обратные связи.

Формула изобретения

Устройство для формирования тестов, содержащее генератор синхроимпульсов, щифратор, дешифратор, регистр сдвига, регистр, блок управления, содержащий три элемента И, блок записи, триггер, коммутатор, отличающееся тем, что, с целью рас- щирения области применения за счет возможности создания тестов для контроля по

5

0

5

40

35

45

следовательностных узлов, устройство содержит блок памяти, элемент четности, блок регистрации, группу сумматоров по модулю два, причем выход генератора синхроимпульсов соединен с входом триггера и первыми входами первого и второго элементов И, выходы которых соединены с первым и вторым информационными входами коммутатора, третий информационный вход которого соединен с синхровходом устройства и входом записи блока записи, выход которого соединен с входом разрешения коммутатора, первым входом третьего элемента И и входом установки регистра сдвига, инверсным входом разрешения регистра и является выходом признака начала формирования тестового набора устройства, входы задания режима работы которого соединены с информационными входами шифратора, первый выход коммутатора соединен с входами блокировки блока памяти и входом запрета разрешения блока регистрации, выходы которого соеинены с информационными выхода- .ми устройства, первый и второй выходы пшфратора соединены с первым и вторым информационными входами регистра сдвига, первый и второй разрядные выходы которого соединены с адресными входами блоков памяти и регистрации и с первым и вторым входами элемента четности, выход которого соединен с третьим информационным входом регистра сдвига, третий, четвертый и пятый разрядные выходы которого соединены с информационными входами дешифратора и с третьим, четвертым и пятым входами элемента четности, входы которого с шестого по п-й (п-число тестов) соединены с разрядными выходами регистра сдвига с niecToro по п-й соответственно, третий выход шифратора соединен с стробирующим входом блока записи и вторым входом третьего элемента И, выход которого соединен с входом сброса регистра сдвига, вход синхронизации которого соединен с вторым выходом коммутатора и синхровходом регистра, группа информационных входов которого соединена с выходами сумматоров по модулю два группы, первые входы которых соединены с выходами блока памяти, вторые входы су.м- маторов по модулю два группы соединены с выходами дешифратора, выходы регистра соединены с информационны.ми входами блоков регистрации, памяти и записи и входом задания начальных условий устройства, четвертый и пятый выходы шифратора соединены с входом разрешения, адресным входом блока записи, шестой выход пшфратора соединен с входами записи блока памяти и блока регистрации, при этом инверсный выход счетного триггера соединен с вторым входом первого элемента И и D-входо.м триггера, прямой выход которого соединен с вторым входом второго элемента И и синхровходом блока записи.

to

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов | 1988 |

|

SU1573457A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1305687A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Генератор псевдослучайных последовательностей | 1986 |

|

SU1378026A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Герератор тестов | 1986 |

|

SU1361561A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в нроцесса.х организации контроля цифровых узлов. Цель изобретения - расширение области применения за счет возможности создания тестов для контроля последовательностных узлов. Устройство содержит генератор синхроимпульсов, 1нифратор, деи1ифратор, регистр, регистр сдвига, блок управления, элемент четности, группу сумматоров по модулю два, блок регистрации. В каждом такте формирования псевдос,1учайного воздействия изменяется только один бит испытательного сигнала, за счет чего исключаются состязания внутри объекта контроля, вызванные одновременным изменением сигналов на различных входах. 3 ил., I табл. 00 со О5

(K)

(Puz.Z

| Устройство для отладки тестов | 1979 |

|

SU860076A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для перемешивания жидкостей | 1978 |

|

SU866003A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-21—Подача