(54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1982 |

|

SU1107260A2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2002 |

|

RU2223597C1 |

| Цифровой синтезатор частот | 1982 |

|

SU1058075A1 |

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| Цифровой синтезатор частот | 1982 |

|

SU1125733A1 |

| Синтезатор частот | 1982 |

|

SU1084992A1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| УСТРОЙСТВО ЧАСТОТНО-ВРЕМЕННОЙ СИНХРОНИЗАЦИИ | 2006 |

|

RU2341892C2 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

1

Изобретение. относится к радиотехнике и может быть использовано для синтеза частот в радиопередающих, радиоприемных устройствах, а также визмерительной технике.

Известен цифровой синтезатор частот, содержащий последовательно включенные генератор опорных импульсов, делитель частоты с переменным коэффициентом деления (ДПКД) вход и выход которогр подключены к анализатору временного положения рыходных импульсов, включенного между вторым выходом блока управления и входом запрета ДПКД, и триггера. Ме;вду выходом ДПКД и входом триггера включено устройство коррекции временного положения импульсов управляющим вход которого подключен к другому выходу анализатора fl.

Недостатком такого синтезатора является невозможность использования, высоких опорных частот из-за технической сложности создания .высокочастотного устройства коррекции временного положения импульсов.

Наиболее близкий к предлагаемому цифровой синтезатор частот, содержит последовательно соединенные опорный генератор, устройство блокировки к счетчик по модулю N/ а также вычислитель и последовательно соединенные делитель частоты и накопитель, один выход которого соединен с управляющий входом устройства блокировки, при этом вход делителя частоты соединен с выходом опорного генератора, а первый и второй выходы вычислителя соединены

0 соответственно с управлякщимвходом счетчика по модулюТЙ и другим входом накопителя f2j.

Однако известный цифровой синтезатор частот имеет относительно

5 узкий диапазон выходнух частот, вследствие того, что возможность использования . высокой опорной частоты сужается из-за наличия в нем генератора задержки, в котором долж0на осуществляться задержка прямоугольного импульса длительностью примерно равной половине периода входного сигнала. Величина задержки дол5хна быть в десятки раз меньше

5 длительности импульса, что значительно повышает сложность процессазадержки.

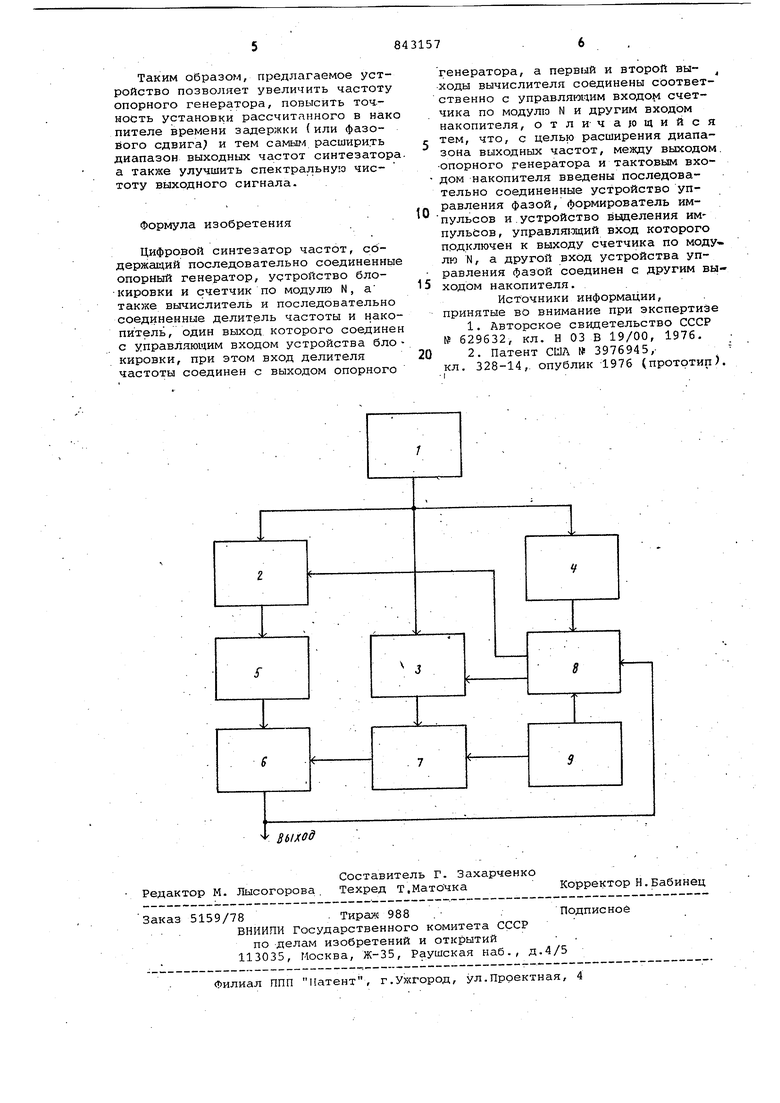

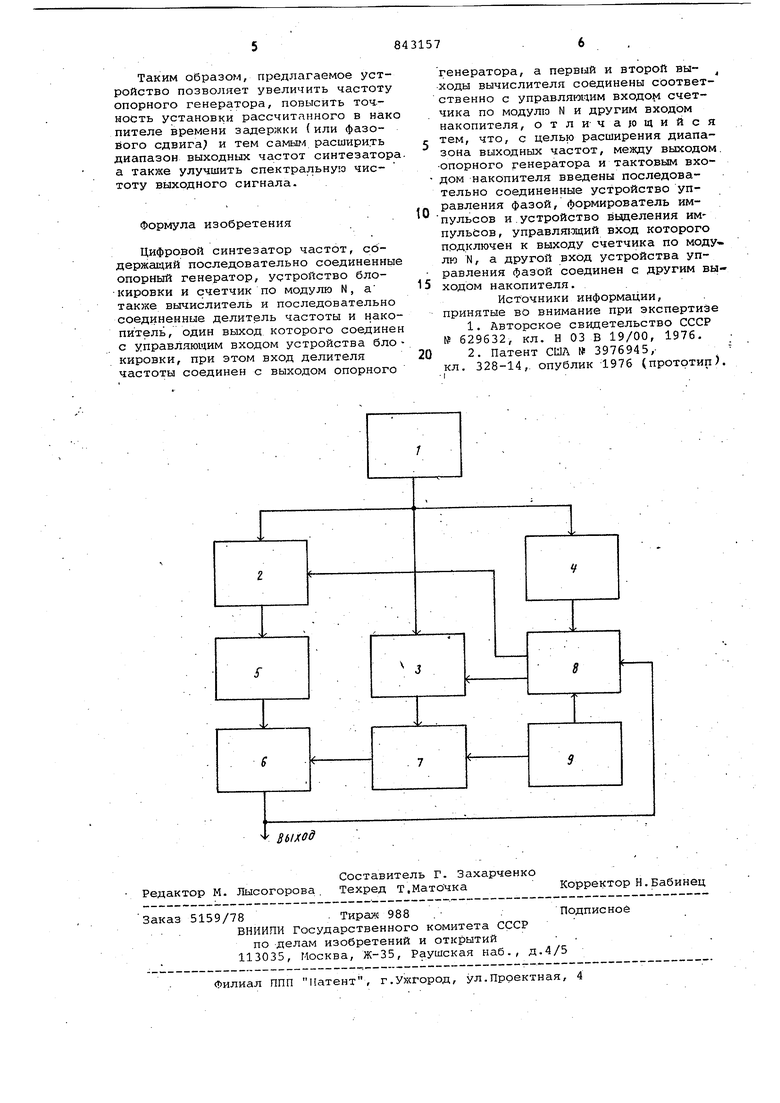

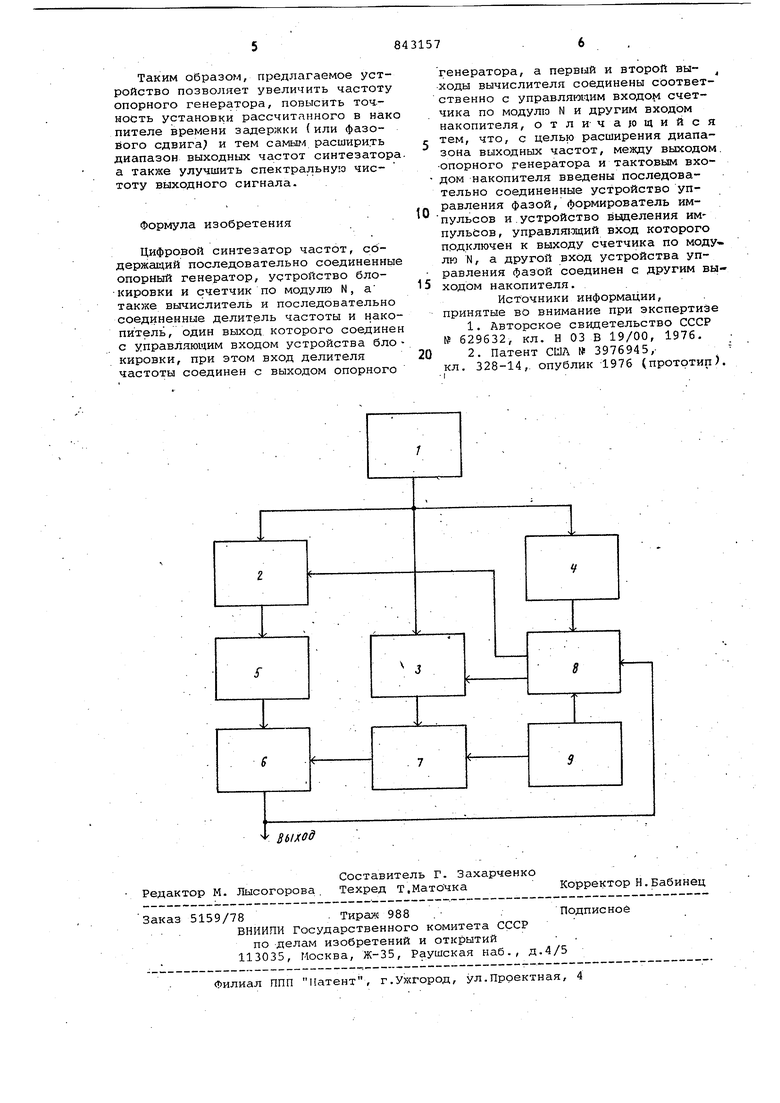

Цель изобретения,- расширение }0 диапазона выходных частот. Поставленная цель достигается тем, что в цифровой генератор, содержащий последовательно соединенные опорный генератор, устройство блокировки и.счетчик по модулю N, а также вычислитель и последовательно соединенные делитель частоты и jнакопитель, один выход которого сое динен с управляющим входом устройства блокировки, при этом вход делителя Частоты соединен с выходом . опорного генератора, а первый-и вто рой выходы вычислителя -соединены соответственно с управляюгдим входом сч.етчика по модулю N и другим входом накопителя, между выходом опорного .генератора и .тактовым входом накопителя введены последовательно соединенные устройство управления фазой, формирователь импульсов и устройство выделения импульсов, управлярШй вход которого подключен к выходу счетчика по модулю N, а другой вход устройства управления фазой соединен с другим выходом накопителя. На чертеже представлена структур ная электрическая схема предлагаемого устройства. Цифровой синтезатор частот содержит опорный генератор 1, устройство 2 управления фазой, устройство 3 блокировки, делитель 4 часто ты, формирователь 5 импульсов, устройство 6- выделения импульсов, счет чик 7 по модулю N, накопитель 8, вы числитель 9. Цифровой синтезатор частот работае-т следующим образом. .Гармонический сигнал опорного генератора 1 через устройство 3 бло кировки и счетчик 7 по модулю N поступает на-управляющий вход устройс ва б вьщеления импульсов. В вычисли ле 9 происходит вычисление отношени частоты опорного генератора 1 к выходной частоте и преобразование это го отношения в код. Код целой части этого отношения подается н.а управляющий вход счетчика 7 по модулю N а код дробной части - на накопитель 8, в котором организуются управляю 1дие сигналы на устройство 3 блокировки и на устройство 2 управления фазой, выходной сигнал с устройства б вьщеления импульсов тактирует накопитель 8. Тот же гармонический сигнал опорного генератора .1 поступ ет на устройство 2 управления фазой, где по команде с накопителя 8 сдвигается по фазе на необходимую величину. Сдвиг по фазе не превышает ЗбО. Осуществить сдвиг по фаз гармонического-сигнала постоянной ч тоты с достаточной, точностью и на достаточно высокой частоте не пред ставляет особых трудностей. Для это го используется или управляеглый фазовращатель, или управляемаялин згздержки, рабочая частота которых практически.не ограничена. Далее сдвинутый сигнал поступает через формирователь 5 импульсов на устройство б вьщеления импульсов, где по команде со счетчика 7 по модулю N пропускается на выход один импульс. Таким образом, средняя выходная частота получается на выходе счетчика 7 по модулю N, а устройство 2 управления фазой, формирова.тель 5 импульсов и устройство 6 выделения Импульсов создают равномерную расстановку выходных импульсов в пределах одного периода входной опорной частоты. Суть предложения заключается в резком снижении требований к быстродействию блока управления фазой, так как фазовый сдвиг всех промежуточных импульсов несущественен. Важно только, чтобы -требуемый сдвиг фазы установился к моменту начала импульса, пропускаемого блоком выделения импульсов на выход синтезатора. Сдвиг фазы гармонического колебания осуществляется с большой степенью точности и легко реализуем на высоких частотах.Не представляет затруднений и выбор необходимого импульса из импульсной последовательности. Все вместе взятое дает возможность получать на выходе синтезатора импульсы,- сдвинутые во времени на нужную величину на-значительно более высокой выходной частоте, чем в известном синтезаторе. Спектральная чистота выходного сигнала как известного, так и пред- лагаемого синтезатора определяется отношением частоты опорного генератора к выходной частоте и быстродействием программируемого генератора задержки (в известном) или устройства управления фазой, (в предлагаемом устройстве). Преимущество предлагаемого устройства состоит в том, что каждая новая команда на изменения фазового уровня, поступающая от накопителя по окончании выходного импульса, должна быть реализована к моменту нгtчала следующего выходного импульса. Это означает, что задолго до появления выходного импульса все выходные импульсы задержан на необходимое время и нужный импульс пропускается устройством вьщеления импульсов, в то время как в известном необходимо произвести задержку одного единственного прямоугольного импульса, длительность которого меньше периода входной частоты. Сдвиг фазы .гармонгического сигнала реализуется значительно проще и точнее, чем задержка одиночного импульса.

Таким образом, предлагаемое устройство позволяет увеличить частоту опорного генератора, повысить точность установки рассчитанного в нако пителе времени задержки (или фазового сдвига и тем расширить диапазон выходных частот синтезатора, а также улучшить спектральную чистоту выходного сигнала.

Формула изобретения

Цифровой синтезатор частот, содержащий последовательно соединенные опорный генератор, устройство блокировки и счетчик по модулю N, а также вычислитель и последовательно соединенные делитель частоты и накопитель, один выход которого соединен с управляющим входом устройства бло кировки, при этом вход делителя частоты соединен с выходом опорного

генератора, а первый и второй выходы вычислителя соединены соответственно с управляющим входом счетчика по модулю N и другим входом накопителя, отл и- чающийся тем, что, с целью расширения диапазона выходных частот, между выходом, опорного генератора и тактовым входом накопителя введены последовательно соединенные устройство управления фазой, формирователь им0пульсов и.устройство вьщеления импульсов , управляющий вход которого подключен к выходу счетчика по модулю N, а другой вход устройства управления фазой соединен с другим вы5ходом накопителя.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-06-30—Публикация

1979-09-27—Подача