Изобретение относится к радиотехнике, в частности к технике цифрового вычислительного синтеза частот, и может быть использовано для формирования сетки частот в радиопередающих и радиоприемных устройствах, а также в устройствах синхронизации различного применения.

Известны устройства пассивного цифрового синтеза частот путем сложения потоков двухуровневых сигналов, в которых исходный поток импульсов с эталонной частотой поступает на ряд делителей частоты. Потоки импульсов с входа и выхода делителей поступают на соответствующие ключи-счетчики, которые имеют по два входа и одному выходу. Выходные импульсы делителя служат метками времени, которые делят поток выходных сигналов на пачки. Счетчик, ориентируясь по этим меткам, ведет счет импульсов в каждой пачке и, в зависимости от нужной частоты, не пропускает нужное число импульсов, выбирая их так, чтобы обеспечивалось несовпадение моментов времени появления импульсов на выходах любых двух ключей. Все потоки складываются с помощью элемента ИЛИ и образуют общий поток импульсов со средней частотой, равной требуемой [1].

Недостатком устройств является наличие в спектре синтезированного сигнала большого количества побочных составляющих.

Известны также устройства оптимального цифрового синтеза с потоком двухуровневых импульсов, в которых с целью минимизации суммарной мощности всех побочных составляющих в спектре выходного сигнала осуществляется выбор из исходного потока импульсов эталонной частоты импульсов, ближайших к импульсам гипотетической (расчетной) последовательности. Данные устройства содержат последовательно соединенные генератор импульсов эталонной частоты f0 и делитель частоты с переменным коэффициентом деления (ДПКД), управляющий вход и выход которого подключены соответственно к выходу и входу анализатора. Анализатор представляет собой вычислитель, программируемый кодом с устройства управления и вырабатывающий сигнал переключения коэффициента деления ДПКД, который принимает значения N и N+1 [1].

Недостатком устройств является то, что для существенного подавления побочных составляющих необходимо выбирать большие значения N, что ограничивает диапазон выходных частот.

Наиболее близким к изобретению является синтезатор пассивного цифрового синтеза частот с фазовой коррекцией потока двухуровневых импульсов, содержащий генератор импульсов (ГИ) эталонной частоты f0, входную шину кода установки частоты fвых, схему исключения импульса, счетчик по модулю N, цифровой делитель, накопитель фазовой задержки и программируемый генератор задержки, причем выход ГИ соединен с информационным входом схемы исключения импульса, управляющий вход которой соединен с выходным разрядом переноса накопителя фазовой задержки, а выход - со счетным входом счетчика по модулю N, управляющий вход счетчика по модулю N соединен с первым выходом (N) цифрового делителя, а выход - с информационным входом программируемого генератора задержки, на управляющий вход которого подается код задержки фазы с выхода накопителя фазовой задержки, информационный вход которого соединен со вторым выходом (К) цифрового делителя, а управляющий вход - с выходом программируемого генератора задержки и выходом синтезатора [2].

При отношении частот

f0/fвых = N+αQ, (1)

где N - целое значение, α/Q - неделимая дробь, цифровой делитель вычисляет значения N и

K = 2n•(α/Q), (2)

где n - разрядность накопителя фазовой задержки и программируемого генератора задержки.

Соответственно устанавливается коэффициент деления счетчика по модулю N и приращение содержимого накопителя фазовой задержки К. На i-м периоде выходного сигнала синтезатора N импульсов с выхода ГИ проходят через схему запрета импульса на счетный вход счетчика по модулю N, после чего последний формирует импульс, поступающий на информационный вход программируемого генератора задержки. Программируемый генератор задержки задерживает этот импульс на время

где Т0 - период импульсов ГИ, Аi - текущее содержимое накопителя фазовой задержки, а Т0/2n - дискрет формирования фазовой задержки.

Появившийся на выходе программируемого генератора задержки i-й импульс синтезируемой последовательности поступает на управляющий вход накопителя фазовой задержки для подготовки к формированию (i+1)-го импульса. При этом происходит увеличение текущего значения накопителя фазовой задержки Ai+1= Ai+K, если нет переполнения, и Ai+1=Ai+K-2n, если произошло переполнение накопителя. В последнем случае сигнал переполнения с выхода накопителя фазовой задержки поступает на управляющий вход схемы запрета импульса. Схема запрета импульса запрещает прохождение одного импульса от генератора импульсов, обеспечивая формирование (i+1)-го выходного импульса счетчиком по модулю N через N+1 периодов импульсов ГИ, что соответствует фазовой коррекции выходного сигнала синтезатора на Т0.

Наличие в (1) ненулевой дроби α/Q соответствует формированию импульсной последовательности с частотой, некратной частоте ГИ. При этом на каждом периоде формируемой последовательности будет происходить увеличение разности фаз между импульсами гипотетической последовательности и импульсами на выходе счетчика по модулю N на величину

Δt = T0•α/Q. (3)

Цифровой делитель по формуле (2) вычисляет значение кода К, соответствующее с определенной точностью значению Δt:

K≈2n•Δt/T0 (4)

На i-м периоде выходной последовательности накопитель фазовой задержки вычисляет значение кода Аi, соответствующее текущей временной разности фаз τi = i•Δt между импульсами гипотетической последовательности и импульсами на выходе счетчика по модулю N. Программируемый генератор задержки по коду Аi выполняет задержку i-го выходного импульса счетчика по модулю N на величину τi, корректируя его фазу до совмещения с фазой импульса гипотетической последовательности. Точность коррекции и, следовательно, формирования выходной импульсной последовательности определяется величиной дискрета формирования фазовой задержки τмин = T0/2n и увеличивается с ростом n.

По сигналу переполнения накопителя фазовой задержки, когда текущая временная разность фаз τi+1 превысит значение Т0, схема запрета импульса уменьшает τi+1 на величину Т0 за счет исключения одного импульса из входной последовательности счетчика по модулю N. Накопитель фазовой задержки и программируемый генератор задержки автоматически отслеживают коррекцию временной разности фаз на Т0 за счет выполнения операции Ai+1=Ai+K-2n, соответствующей переполнению.

Точность формирования синтезатором импульсной последовательности связана с ошибками округления величины α/Q при вычислении кода К из-за конечной разрядности цифрового вычислителя, накопителя фазовой задержки и программируемого генератора задержки. Повышение точности формирования импульсной последовательности связано в первую очередь с увеличением точности и разрядности программируемого генератора задержки, имеющими технологические пределы, а также разрядности цифрового вычислителя и накопителя фазовой задержки.

Кроме того, повышение точности формирования импульсной последовательности за счет уменьшения Т0 повышением опорной частоты f0 приводит к увеличению разрядности счетчика по модулю N и повышению требований по его и схемы выделения импульса быстродействию.

Недостатком данного синтезатора является существенное усложнение схемы при увеличении разрядности программируемого генератора задержки для обеспечения более высокой точности формирования импульсной последовательности и, как следствие, большой объем электрорадиоэлементов для его реализации.

Изобретением решается задача повышения точности формирования устройством импульсной последовательности при сохранении разрядности программируемого генератора задержки и требований к быстродействию функциональных узлов схемы.

Для достижения этого технического результата в цифровой синтезатор частот, содержащий генератор импульсов эталонной частоты f0, входную шину кода установки частоты, схему исключения импульса, счетчик по модулю N, цифровой делитель, накопитель фазовой задержки и программируемый генератор задержки, причем выход схемы исключения импульса соединен со счетным входом счетчика по модулю N, управляющий вход счетчика по модулю N соединен с первым выходом (N) цифрового делителя, а выход - с информационным входом программируемого генератора задержки, на управляющий вход которого подается код задержки фазы с выхода накопителя фазовой задержки, информационный вход которого соединен со вторым выходом (К) цифрового делителя, а управляющий вход - с выходом программируемого генератора задержки и выходом синтезатора, дополнительно введены схема исключающего ИЛИ, первый вход которой соединен с выходом генератора импульсов, второй вход - с старшим выходным разрядом накопителя фазовой задержки, а выход - с информационным входом схемы запрета импульса и умножитель импульсов на 2, вход которого соединен с старшим выходным разрядом накопителя фазовой задержки, а выход - с управляющим входом схемы запрета импульса.

Отличительными признаками предлагаемого изобретения от указанного прототипа являются дополнительно введенные в него схема исключающего ИЛИ, первый вход которой соединен с выходом генератора импульсов, второй вход - со старшим выходным разрядом накопителя фазовой задержки, а выход - с информационным входом схемы запрета импульса и умножитель импульсов на 2, вход которого соединен со старшим выходным разрядом накопителя фазовой задержки, а выход - с управляющим входом схемы запрета импульса.

Благодаря наличию этих признаков, при смене значения старшего разряда кода А на выходе накопителя фазовой задержки, что соответствует превышению текущей временной разности фаз τi значения Т0/2, схема запрета импульса с умножителем на 2 уменьшают τi на величину Т0/2 за счет исключения одного импульса из входной последовательности счетчика по модулю N и инверсии импульсной последовательности схемой исключающего ИЛИ, используемого в качестве управляемого инвертора. При таком построении устройства программируемый генератор задержки имеет максимальную задержку Т0/2, что при сохранении его разрядности соответствует двухкратному уменьшению его дискрета τмин, двухкратному увеличению точности коррекции задержки фазы и формирования выходной последовательности.

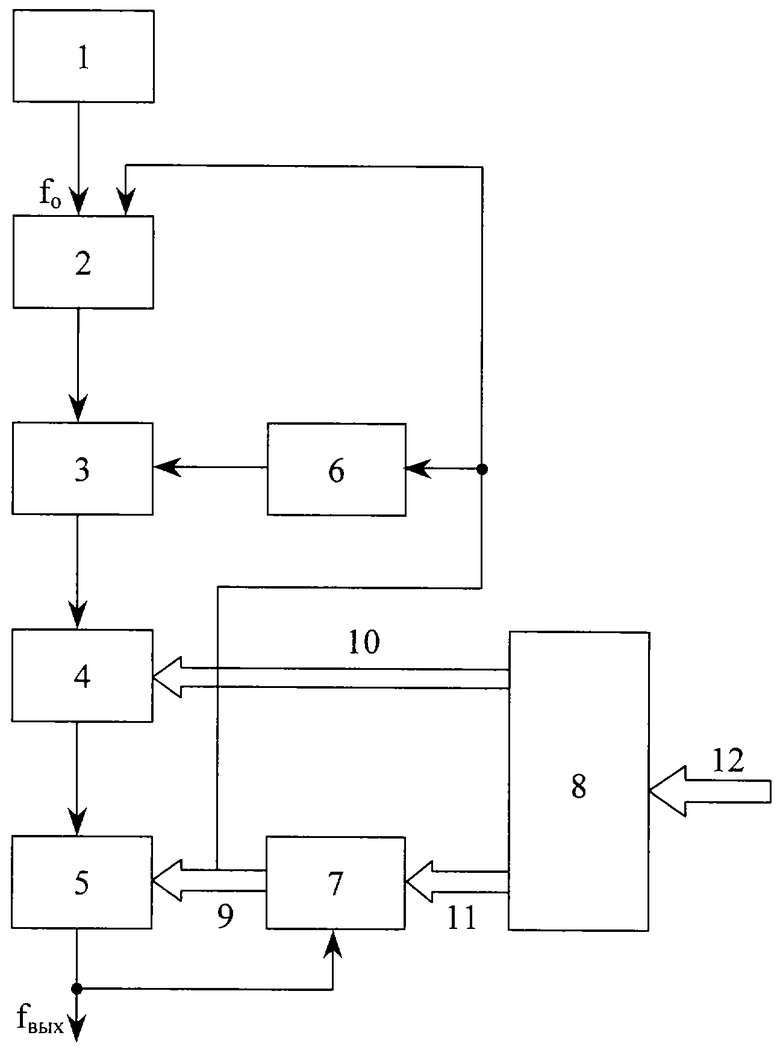

На чертеже представлена структурная схема цифрового синтезатора частот.

Цифровой синтезатор частот содержит генератор импульсов 1, схему исключающего ИЛИ 2, схему запрета импульса 3, счетчик 4 по модулю N, программируемый генератор задержки 5, умножитель импульсов на 2 6, накопитель фазовой задержки 7, цифровой делитель 8, шину 9 кода установки фазовой задержки, шину 10 установки кода N, шину 11 установки кода К и входную шину 12 кода частоты.

Принцип действия предлагаемого цифрового синтезатора частот, как и устройства-прототипа, основан на алгоритме, использующем представление отношения частот опорной и формируемой импульсных последовательностей в виде (1).

f0/fвых = N+α/Q.

где N - целое значение, α/q - неделимая дробь.

Синтезатор частот работает следующим образом.

На входной шине 12 кода установки частоты устанавливается кодированное значение синтезируемой частоты (код установки частоты). Это число поступает на вход цифрового делителя 8, на выходе которого формируется код N и код фазового приращения

K = 2n+1•(α/Q),

где n - разрядность программируемого генератора задержки 5.

Код N по шине 10 поступает на управляющий вход счетчика 4 по модулю N, а код К по шине 11 поступает на информационный вход накопителя фазовой задержки 7. Соответственно устанавливается коэффициент деления счетчика 4 по модулю N и приращение К содержимого накопителя фазовой задержки 7. Накопитель фазовой задержки 7 емкостью n+1 формирует на выходе код, n младших разрядов которого Аi по шине 9 поступают на управляющий вход программируемого генератора задержки 5, а старший n+1-й разряд поступает на вход умножителя 6 импульсов на 2 и второй вход схемы исключающего ИЛИ 2. На первый вход схемы исключающего ИЛИ 2 с выхода генератора импульсов 1 поступает последовательность импульсов, имеющая форму меандра со скважностью 2.

На i-м периоде выходного сигнала синтезатора N импульсов, имеющих форму меандра со скважностью 2, с выхода генератора импульсов 1 проходят через схему исключающего ИЛИ 2 и схему запрета импульса 3 на счетный вход счетчика по модулю N 4, после чего последний формирует импульс, поступающий на информационный вход программируемого генератора задержки 5.

Программируемый генератор задержки, обеспечивающий максимальную задержку τмакс = T0/2 и дискрет задержки τмин = τмакс/2n = T0/2n+1, задерживает этот импульс на время

Появившийся на выходе программируемого генератора 5 задержки i-й импульс формируемой последовательности поступает на управляющий вход накопителя фазовой задержки 7 для подготовки к формированию (i+1)-го импульса. При этом происходит увеличение текущего значения накопителя фазовой задержки Аi+1= Аi+к. Если при этом в накопителе фазовой задержки произойдет перенос единицы из разряда n в разряд (n+1), то текущее значение Аi+1 примет значение Ai+K-2n, а (n+1)-й разряд накопителя фазовой задержки сменит значение на противоположное.

При изменении значения старшего разряда накопителя фазовой задержки, умножитель на 2 формирует сигнал, по которому схема запрета импульса исключает один импульс из импульсной последовательности генератора импульсов, а схема исключающего ИЛИ выполняет сдвиг импульсной последовательности по фазе на 180o, что в итоге равносильно задержке импульсной последовательности на счетном входе счетчика по модулю 2 на Т0/2, так как импульсная последовательность имеет форму меандра со скважностью 2.

Накопитель фазовой задержки и программируемый генератор задержки автоматически отслеживают коррекцию временной разности фаз на Т0/2 за счет выполнения операции

Аi+1=Аi+К-2n,

соответствующей смене значения старшего разряда накопителя фазовой задержки.

Аналогично, при повторной смене значения старшего разряда накопителя фазовой задержки совместная работа умножителя импульса на 2, схемы исключающего ИЛИ и схемы запрета импульса приведет к вторичной задержке импульсной последовательности, поступающей на счетный вход счетчика по модулю N с выхода генератора импульсов, на Т0/2. При этом накопитель фазовой задержки и программируемый генератор задержки вновь отследят коррекцию временной разности фаз на Т0/2.

Таким образом, двум циклам смены значения старшего разряда накопителя фазовой задержки 7 и задержки импульсной последовательности генератора импульсов на Т0/2 заявляемого синтезатора частот соответствует один цикл формирования сигнала переноса накопителя фазовой задержки и задержки импульсной последовательности генератора импульсов на Т0 устройства-прототипа.

В заявляемом устройстве в 2 раза повышается точность формирования импульсной последовательности за счет двухкратного уменьшения дискрета и диапазона задержек, реализуемых программируемым генератором задержек при сохранении его разрядности. Увеличение разрядности цифрового делителя в части формирования кода К не сказывается на быстродействии устройства, так как значение К вычисляется единовременно в начале работы устройства. Быстродействие (n+1)-разрядного накопителя фазовой ошибки устройства практически равно быстродействию n-разрядного накопителя фазовой ошибки с выходом переполнения устройства-прототипа.

Введение схемы исключающего ИЛИ и умножителя на 2 позволяет увеличить точность формирования устройством импульсной последовательности путем увеличения разрядности только накопителя фазовой задержки и цифрового делителя или уменьшить разрядность программируемого генератора задержки при сохранении точности формирования устройством импульсной последовательности.

Источники информации

1. Шапиро Д. Н., Паин А.А. Основы теории синтеза частот. - М.: Радио и связь, 1981.

2. Патент США 3976945, кл. 328-14, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1979 |

|

SU843157A1 |

| ИЗМЕРИТЕЛЬНЫЙ ГЕНЕРАТОР ПАРНЫХ ИМПУЛЬСОВ | 2022 |

|

RU2788980C1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

| ГЕНЕРАТОР ПАРНЫХ СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 2022 |

|

RU2795263C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2149503C1 |

| Цифровой синтезатор частот | 1982 |

|

SU1107260A2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2004 |

|

RU2262190C1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

Изобретение относится к радиотехнике и может использоваться для формирования сетки частот в радиопередающих и радиоприемных устройствах. Достигаемый технический результат - повышение точности формирования импульсной последовательности при сохранении разрядности программируемого генератора задержки и требований к быстродействию. Цифровой синтезатор частот содержит генератор импульсов, схему запрета импульса, счетчик по модулю N, цифровой делитель, накопитель фазовой задержки, программируемый генератор задержки, схему исключающего ИЛИ и умножитель импульсов на 2. 1 ил.

Цифровой синтезатор частот, содержащий генератор импульсов, входную шину кода установки частоты, схему запрета импульса, счетчик по модулю N, цифровой делитель, накопитель фазовой задержки и программируемый генератор задержки, причем выход схемы запрета импульса соединен со счетным входом счетчика по модулю N, управляющий вход счетчика по модулю N соединен с первым выходом цифрового делителя, а выход - с информационным входом программируемого генератора задержки, на управляющий вход которого подается код задержки фазы с выхода накопителя фазовой задержки, информационный вход которого соединен со вторым выходом цифрового делителя, а управляющий вход - с выходом программируемого генератора задержки и выходом синтезатора, отличающийся тем, что в него дополнительно введены схема исключающего ИЛИ, первый вход которой соединен с выходом генератора импульсов, второй вход - с старшим выходным разрядом накопителя фазовой задержки, а выход - с информационным входом схемы запрета импульса и умножитель импульсов на 2, вход которого соединен с старшим выходным разрядом накопителя фазовой задержки, а выход - с управляющим входом схемы запрета импульса.

| US 3976945, 24.08.1976 | |||

| RU 2058659 C1, 20.04.1996 | |||

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2143173C1 |

| US 4349887, 14.09.1982 | |||

| Станок для скручивания концов проволок у панцирных сеток | 1959 |

|

SU125790A1 |

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

Авторы

Даты

2004-02-10—Публикация

2002-06-21—Подача