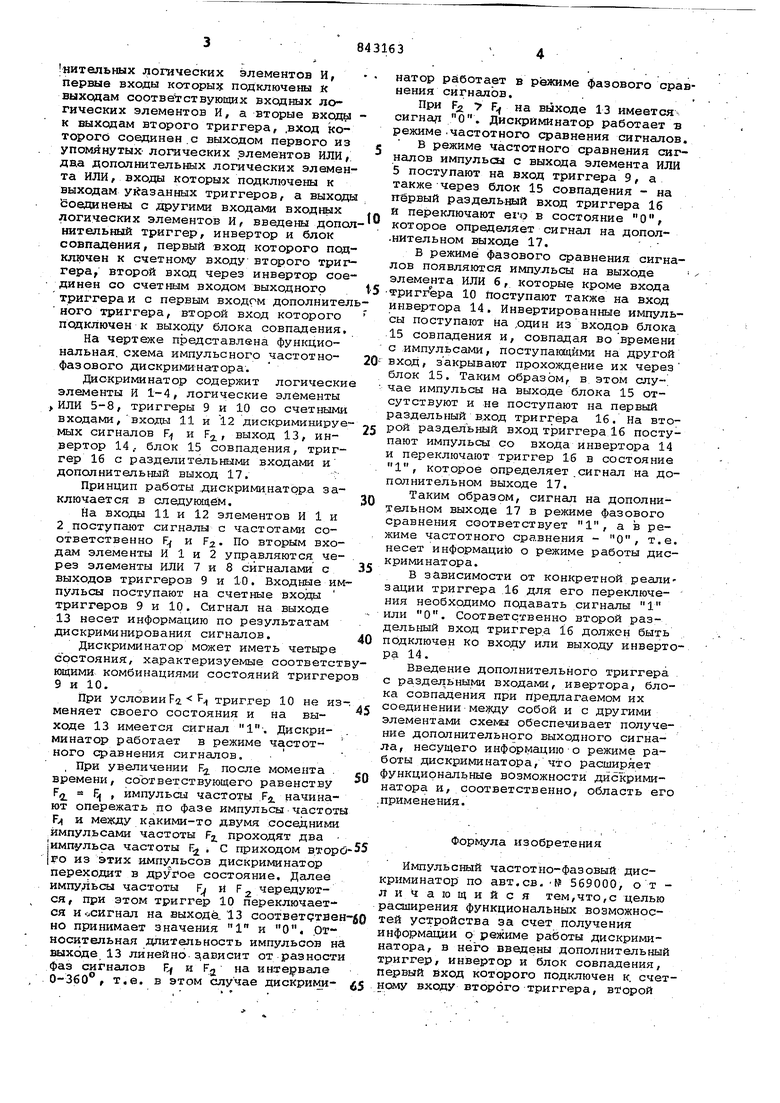

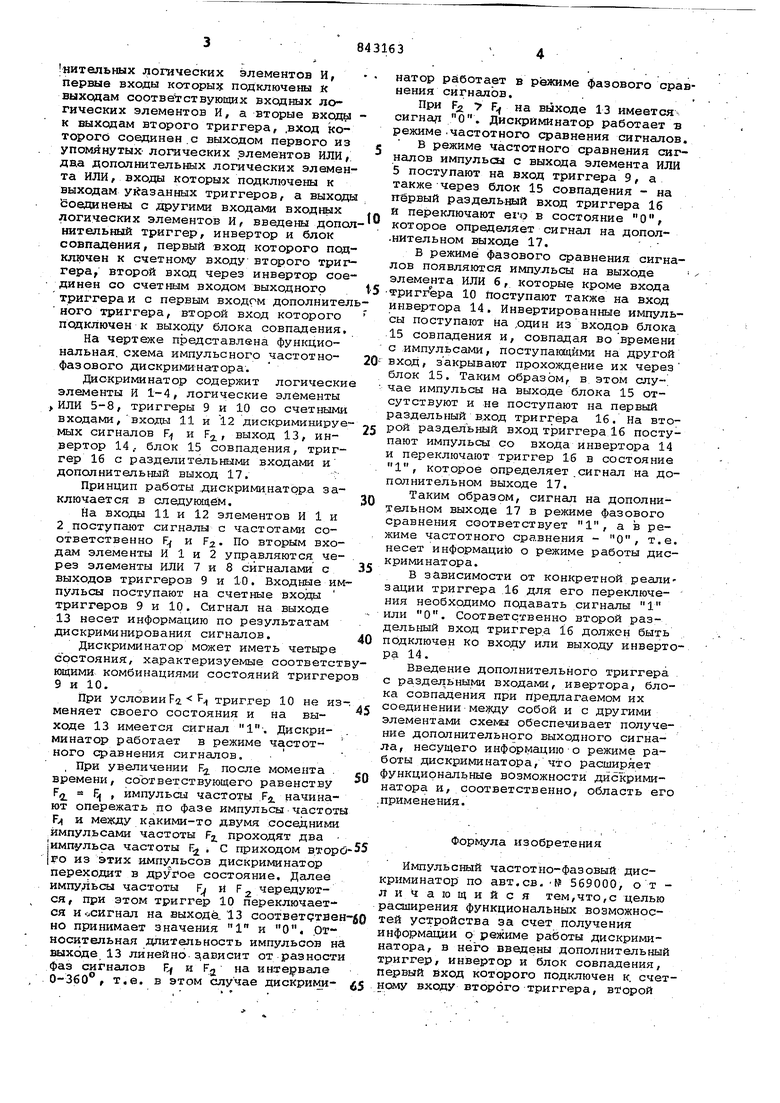

Изобретение относится к импульсно технике. По основному авт. св. fJ 569-000 известен импульсный частотно-фазовый дискриминатор содержит два входных логических элемента-И, один из входов каждого из которых подключен к источнику входных сигналов, а вы:ход - ко входу логического элемента ИЛИ., выходной Триггер со счетным- вхо дом, который соединен с выходом второго логического элемента ИЛИ, входы которого соединены с выходами двух дополнительных логичесг их элементов И, первые входы которых подключены к выходам соответствующих входных логических элементов И, а вторые входы к выходам входного триггера,- вход которого соединен с выходом первого из упомянутых логических элементов ИЛИ, и два дополнительных логических элемента ИЛИ, входы которых подключены к выходам указанных триггеров, а выходы соединены с другими входаг входных логических эле и1ентов И . Этот дискриминатор имеет логический выход с выходного триггера и мож работать в двух режимах - частотного и фазового сравнения сигналов. В режиме частотного сравнения сигналов характеристика дискриминатора релейная. В режиме фаз-ов.ого сравнения сигналов выходной сигнал дискриминатора импульсный, при этом относи-, тельная длительность импульсов пропорциональна разности фаз сравниваемых сигналов на интервале 0-360°. Переключение из одного режима в другой происходит автоматически l. В ряде случаев применения дискриминатора необходима информация о режиме работы. Однако., дискриминатор не дает сигнала, несущего указанную информацию, iTo ограничивает его функциональные возможности. Цель изобретения - расширение функциональных возможностей дискриминатора за счет получения информации о режиме работы дискри№1 натора. Указанная цель достигается тем, что в импульсный частотно-фазовый дискриминатор, содержащий два выходных логических элемента И, один из.входов ка дого из которых подключен к источнику входных сигналов, а выходк входу логического элемента ИЛИ, выходной триггер со счетным входом, который соединен с выходом второго логического элемента ИЛИ, входы которого соединены с выходами двух допол нительных л;1огических элементов И, первые входы которы: подключены к выходам соответствующих входных логических элементов И, а вторые вхощл к выходам второго триггера, .вход которого соединен.с выходом первого из упомйнутых- логических элементов ИЛИ, два дополнительных логических элемента ИЛИ, входы которых подключены к выходам У1 азанных триггеров, а выходы боединены с другими входами входных логических элементов И, введены допол нительный триггер, инвертор и блок совпадения, первый вход которого под ключен к счетному входу второго триг гера, второй вход через инвертор сое динен со счетным входом выходного триггера и с первым входом дополнител ного триггера, второй вход которого подключен к выходу блока совпадения. На чертеже п эедставлена функциональная, схема импульсного частотнофазового дискриминатора. Дискриминатор содержит логически элементы И 1-4, логические элементы ИЛИ 5-8, триггеры 9 и 10 со счетными входами,входы 11 и 12 дискриминируе мых сигналов R; и Fi, выход 13, инвертор 14, блок 15 совпадения, триггер 16 с разделительными входами и дополнительный выход 17. Принцип работы дискриминатора заключается в следукидём. На входы 11 и 12 элементов И 1 и 2 поступают сигналы с частотами соответственно Ef и р2. По вторым вхоДс1М элементы И 1 и 2 управляются через элементы ИЛИ 7 и 8 сигналами с выходов триггеров 9 и 10. Входные им пульсы поступают на счетные входы триггеров 9 и 10. Сигнал на выходе 13 несет информацию по результатам дискриминирования сигналов, Дискриминатор может иметь четыре состояния, характеризуемые соответст ющими комбинациями состояний триггер 9 и 10, При условии Fa F триггер 10 не из меняет своего состояния и на выходе 13 имеется сигнал . Дискриминатор работает в режиме частотного сравнения сигналов. При увеличении F после момента . времени, соответствующего равенству F, fil , импульсы частоты Fj. начинают опережать по фазе импульсы частот Ру( и между какими-то двумя соседними импульсами частоты FJL проходят два импульса частоты Г , С приходом втор |го из этих импу льсов дискриминатор переходит в друхое состояние. Далее импу. частоты F rt F 2 чередуются, при этом триггер 10 переключается и- сигнал на выходё 13 соответртве но принимает значения 1 и О, Относительная дпительность импульсов н выходе 13 линейно-э(ави си т от разност фаз сигналов Е( и Fg на ин.тервале О-ЗбО , т.е, в этом случае дискриминатор работает в режиме фазового сравнения сигналов,., При 7 F на выходе 13 имеется сигнад О. Дискриминатор работает в режиме.частотного сравнения сигналов. В режиме частотного сравнения сигналов импульсы с выхода элемента ИЛИ 5 поступают на вход триггера 9, а также через блок 15 совпадения - на ггёрвый раздельный вход триггера 16 и переключают его в состояние О, которое определяет сигнал на допол.нительном выходе 17, В режиме фазового сравнения сигналов появляются импульсы на выходе элемента ИЛИ 6, которые кроме входа «триггера Ю поступают также на вход инвертора 14, Инвертированные импульсы поступают на ..один из входов блока 15 совпадения и, совпадая во времени с импульсами, поступающими на другой ВХО.Ц, закрывают прохождение их через блок 15, Таким образом, в этом случае импульсы на выходе блОка 15 отсутствуют и не поступают на первый раздельный вход триггера 16. На второй раздельный вход триггера 16 поступают импульсы со входа инвертора 14 и переключают триггер 16 в состояние 1, которое определяет.сигнал на дополнительном выходе 17. Таким образом, сигнал на дополнительном выходе 17 в режиме фазового сравнения соответствует 1, а в режиме частотного сравнения - О, т.е. несет информацию о режиме работы дискриминатора. В зависимости от конкретной реализации триггера 16 для его переключе- ния необходимо подавать сигналы 1 или О, Соответственно второй раздельный вход триггер.а 1б должен быть подключен ко ВХО.ЦУ или выходу инвертора 14. Введение дополнительного триггера с разде.льными входами, ивертора, блока совпадения при Пре.цлагаемом их соединении между собой и с другими элементами схемы обеспечивает получение дополнительного выходного сигнала, несущего информацию-о режиме работы дискриминатора, что расширяет функциональные возможности дискриминатора и, соответственно, область его .приме не ни:я. Формула изобретения Импульсный частотно-фазовый дискриминатор по авт,св.№ 569000, от лишающийся тем,что,с целью расширения функциональных возможностей устройства за счет получения информации о режиме работы дискриминатора, в него введены дополнительный триггер, инвертор и блок совпадения, первый вход которого подключен к. счетному входу второго триггера, второй

вход через инвертор соединен со счетным входом выходно: Ь триггера и с первым входом дополнительного триггера, второй вход которого подключен к ВЫХОДУ блока сойпадения.

Источники информации, принятые во внимание при экспертизе

f

1. Авторское свидетельство СССР № 569000 кл. Н 03 D 13/00, 1974-.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод постоянного тока | 1978 |

|

SU771834A1 |

| Электропривод постоянного тока | 1981 |

|

SU995247A1 |

| Электропривод постоянного тока | 1980 |

|

SU928575A1 |

| СИНХРОННО-СИНФАЗНЫЙ ЭЛЕКТРОПРИВОД | 2006 |

|

RU2310971C1 |

| Импульсный частотно-фазовой дискриминатор | 1974 |

|

SU569000A1 |

| Позиционный электропривод | 1984 |

|

SU1270859A1 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2016 |

|

RU2621288C1 |

| Устройство для регулирования частоты статического преобразователя многодвигательного асинхронного тягового электропривода | 1979 |

|

SU875571A1 |

| Цифровой частотно-фазовый дискриминатор | 1987 |

|

SU1494204A2 |

| ЭЛЕКТРОПРИВОД | 1997 |

|

RU2130688C1 |

Авторы

Даты

1981-06-30—Публикация

1979-08-08—Подача