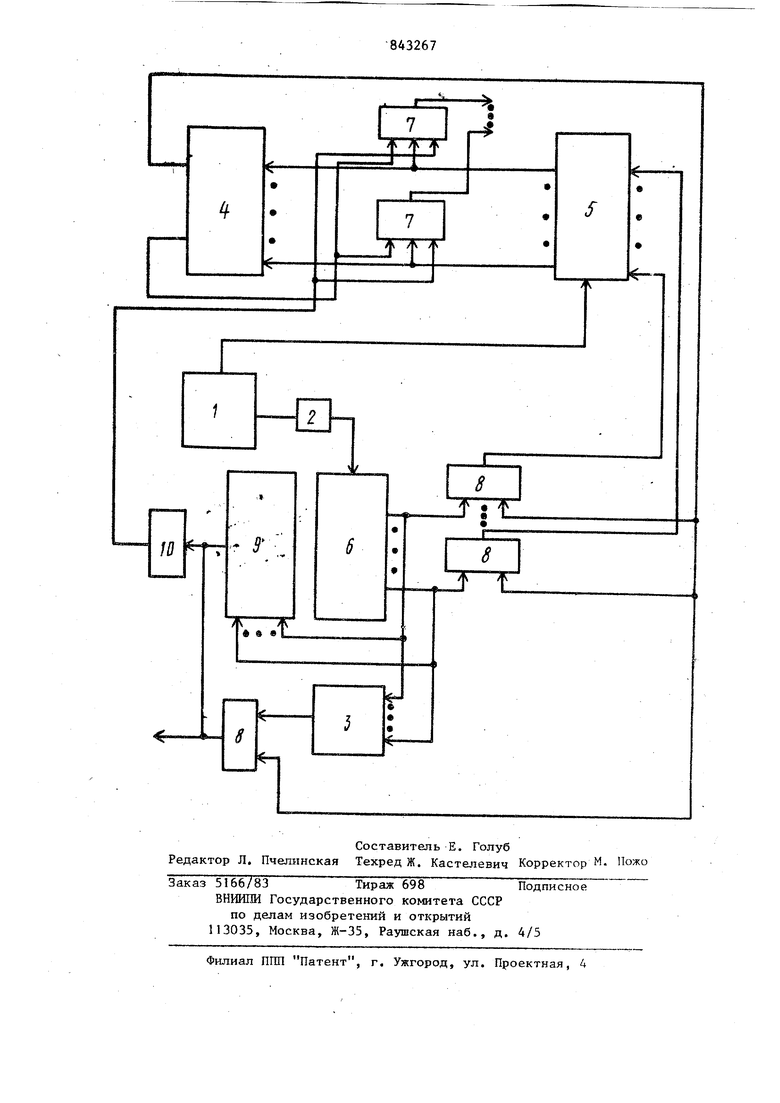

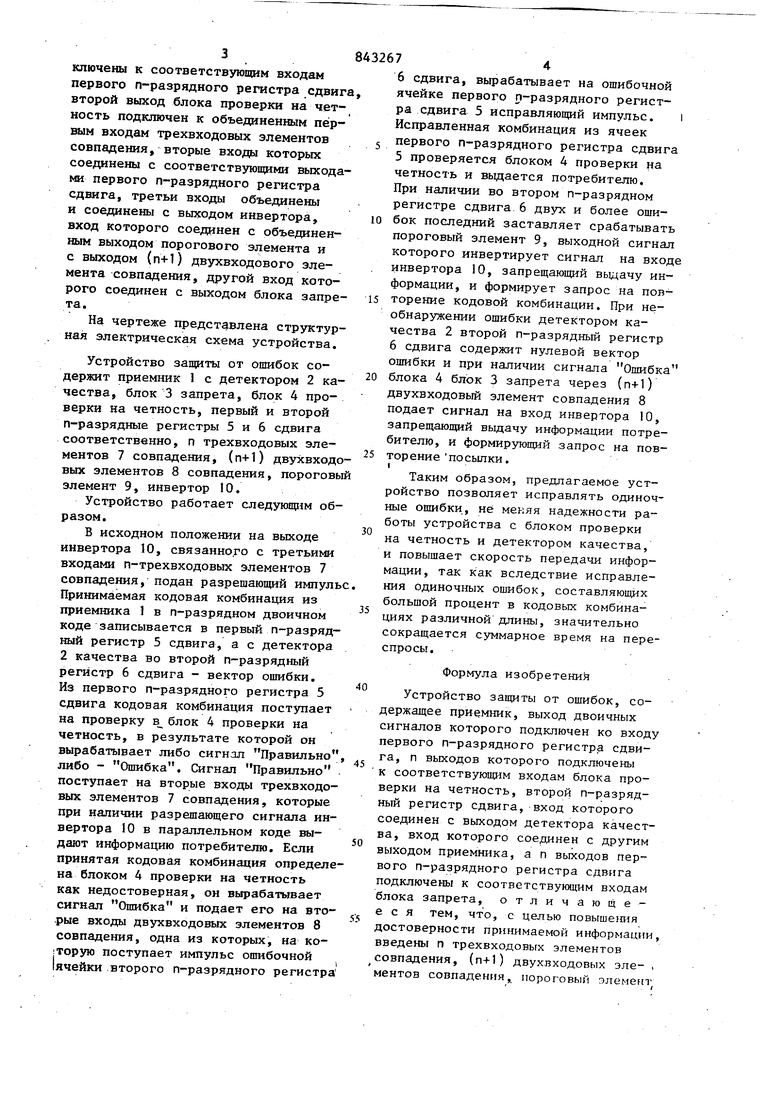

Изобретение относится к технике связи и может использоваться в аппаратуре передачи данньзх для защиты от ошибок. Известно устройство зашиты от оши бок, содержащее приемник, .выход, двоичных сигналов которого подключен ко входу первого п-разрядного регистра сдвига, п выходов которого подключены к соответствующим входам блока проверки на четность, второй п-разрядный регистр сдвига, вход которого соединен с выходом детектора качества, вход которого соединен с другим выходом приемника, а п выходов первого п-разрядного регистра сдвига подключены к соответствукг щим входам блока запрета 13. Однако известное устройство имеет низкую достоверность принимаемой информации. Цель изобретения - повьшение достоверности принимаемой информации. Для этого в устройство защиты от опшбок, содержащее приемник, вы-, ход двоичных сигналов которого подключен ко входу первого п-разрядного регистра сдвига, п выходов которого подключены к соответствующим входам блока проверки на четность, второй п-разрядный регистр сдвига, вход которого соединен с выходом детектора качества, вход которого соединен с другим выходом приемника, а п выходов первого п разрядного регистра сдвига подключены к соответствующим входам блока запрета, введены п трехвходовых элементов совпадения, (п+1) двухвходовых элементов совпадения, пороговый элемент и инвертор, тгри этом первьй выход блока проверки на четность подключен к объединенным первым входам (п+1) двухвходовых элементов совпадения, вторые входы п которых объединены с соответствуюnpiMH входами блока запрета и входами порогового элемента, а выходы - подключены к соответствующим входам первого п-разрядного регистра сдвига второй выход блока проверки на четность подключен к объединенным первым входам трехвходовых элементов совпадения, вторые входы которых соединены с соответствующими выходами первого п-разрядного регистра сдвига, третьи входы объединены и соединены с выходом инвертора, вход которого соединен с объединенным выходом порогового элемента и с выходом (п+1) двухвходового элемента совпадения, другой вход которого соединен с выходом блока эапрета. На чертеже представлена структурная электрическая схема устройства. Устройство защиты от ошибок содержит приемник 1 с детектором 2 качества, блок 3 запрета, блок 4 проверки на четность, первый и второй п-разрядные регистры 5 и 6 сдвига соответственно, п трехвходовых элементов 7 совпадения, (п+1) двухвходо вых элементов 8 совпадения, пороговы элемент 9, инвертор 10. Устройство работает следующим образом. В исходном положении на выходе инвертора 10, связанного с третьими входами п-трехвкодовых элементов 7 совпадения, подан разрешающий импул Принимаемая кодовая комбинация из приемника 1 в п-разрядном двоичном коде записывается в первый п-разряд ный регистр 5 сдвига, а с детектора 2 качества во второй п-разрядный регистр 6 сдвига - вектор ошибки. Из первого п-разрядного регистра 5 сдвига кодовая комбинация поступает на проверку в блок 4 проверки на четность, в результате которой он вырабатывает либо сигндл Правильно либо - Ошибка. Сигнал Правильно поступает на вторые входы трехвходо вык элементов 7 совпадения, которые при наличии разрешающего сигнала ин вертора 10 в параллельном коде выдают информацию потребителю. Если принятая кодовая комбинация определ на блоком 4 проверки на четность как недостоверная, он вырабатывает сигнал Ошибка и подает его на вто рые входы двухвходовых элементов 8 совпадения, одна из которых, на коiTopjno поступает импульс ошибочной 1ячейки второго п-разрядного регистр 74 6 сдвига, вырабатывает на ошибочной ячейке первого п-разрядного регистра сдвига 5 исправляющий импульс. i Исправленная комбинация из ячеек первого п-разрядного регистра сдвига 5проверяется блоком 4 проверки на четность и вьздается потребителю. При наличии во втором п-разрядном регистре сдвига.6 двух и более ошибок последний заставляет срабатывать пороговый элемент 9, выходной сигнал которого инвертирует сигнал на входе инвертора 10, запрещающий выдачу информации, и формирует запрос на повторение кодовой комбинации. При необнаружении ошибки детектором качества 2 второй п-разрядный регистр 6сдвига содержит нулевой вектор ошибки и при наличии сигнала Ошибка блока 4 блок 3 запрета через (п+1) двухвходовый элемент совпадения 8 подает сигнал на вход инвертора 10, запрещающий вьщачу информации потребителю, и формирующий запрос на повторение посылки. Таким образом, предлагаемое устройство позволяет исправлять одиночные ошибки, не меняя надежности работы устройства с блоком проверки на четность и детектором качества, и повышает скорость передачи информации, так как вследствие исправления одиночных ошибок, составляющих большой процент в кодовых комбинациях различной длины, значительно сокращается суммарное время на переспросы. Формула изобретени Устройство защиты от ошибок, содержащее приемник, выход двоичных сигналов которого подключен ко входу первого п-разрядного регистра сдвига, п выходов которого подключегй к соответствующим входам блока проверки на четность, второй п-разрядный регистр сдвига, вход которого соединен с выходом детектора качества, вход которого соединен с другим выходом приемника, а п вьгходов первого п-разрядного регистра сдвига подключены к соответствующим входам блока запрета, отличающееся тем, что, с целью повьсшения достоверности принимаемой информации, введены п трехвходовых элементов совпадения, (п+1) двухвходовых эле- , ментов совпадения, пороговый элемент

и инвертор, при этом первый выход блока проверки на четность подклю- , чей к объединенным первым входам (п+1) двухвходовых элементов совпадения, вторые входы п которых объединены с соответствующими входами блока запрета и входами порогового элемента, а выходы - подключены к соответствующим входам первого п-разрядного регистра сдвига, второй выход блока проверки на четность подключены к объединенным первым входам трехвходовых элементов совпадения, вторые входы которых соединены с соответствующими выходами первого п-разрядного

регистра сдвига, третьи входы объединены и соединены с выходом инвертора, вход которого соединен с объединенным выходом порогового элемента и с выходом (п+1)-двухвходового элемента совпадения, другой вход которого соединен с выходом блока запрета.

Источники информации, принятые во внимание при экспертизе

1. Котов П.А. Повышение достоверности передачи цифровой информации. М., Связь, 1966, с.137-139 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема телеметрической информации | 1986 |

|

SU1481828A1 |

| Устройство для формирования и передачи дискретных сигналов | 1985 |

|

SU1277420A1 |

| Устройство для синхронизации биимпульсного сигнала | 1985 |

|

SU1350837A1 |

| Приемник частотно-манипулированных сигналов | 1990 |

|

SU1786680A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ КОМБИНИРОВАННОГО ПРИМЕНЕНИЯ ДВОЙСТВЕННОГО БАЗИСА ПОЛЯ GF(2) И ВЫДЕЛЕНИЯ "СКОЛЬЗЯЩЕГО ОКНА" С ОШИБКАМИ | 2014 |

|

RU2580806C2 |

| Устройство декодирования линейногоциКличЕСКОгО КОдА | 1979 |

|

SU809568A1 |

| СПОСОБ ДЕТЕКТИРОВАНИЯ СИГНАЛОВ С МАГНИТНОГО НОСИТЕЛЯ ИНФОРМАЦИИ, ЗАПИСАННЫХ RLL КОДАМИ, И ДЕТЕКТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2015 |

|

RU2623660C2 |

| ПРИЕМНИК МАЖОРИТАРНО УПЛОТНЕННЫХ СИГНАЛОВ С ПРОВЕРКОЙ НА ЧЕТНОСТЬ | 1990 |

|

RU2025050C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ С ФУНКЦИЕЙ ИСПРАВЛЕНИЯ ОШИБОК | 2011 |

|

RU2486682C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТЬЮ С ФУНКЦИЕЙ ВЫДЕЛЕНИЯ ЗАЧЕТНЫХ ИМПУЛЬСОВ В СКОЛЬЗЯЩЕМ ОКНЕ | 2013 |

|

RU2553089C2 |

Авторы

Даты

1981-06-30—Публикация

1979-08-30—Подача