1

Изобретение относится к автоматике и вычислительной технике и предназначено для преобразования кодов.

Известны преобразователи двоичного кода в двоично-десятичный, содержащие двоичный регистр сдвига и двоично-десятичный регистр сдвига со схемами коррекции по числу тетрад.

Цель изобретения - упростить устройство.

Для этого выходы схемы управления вычитанием соединены с соответствующими входами накапливающего сумматора схемы формирования управляющих сигналов и со входами соответствующих групп вентилей, выходы схемы формирования управляющих сигналов соединены со входами схемы управления вычитанием и с одним из входов схемы анализа знака числа, другие входы которой соединены с выходами знакового разряда накапливающего сумматора, а выходы этой схемы соединены со входом схемы управления вычитанием и со счетным входом четырехразрядного двоичного счетчика.

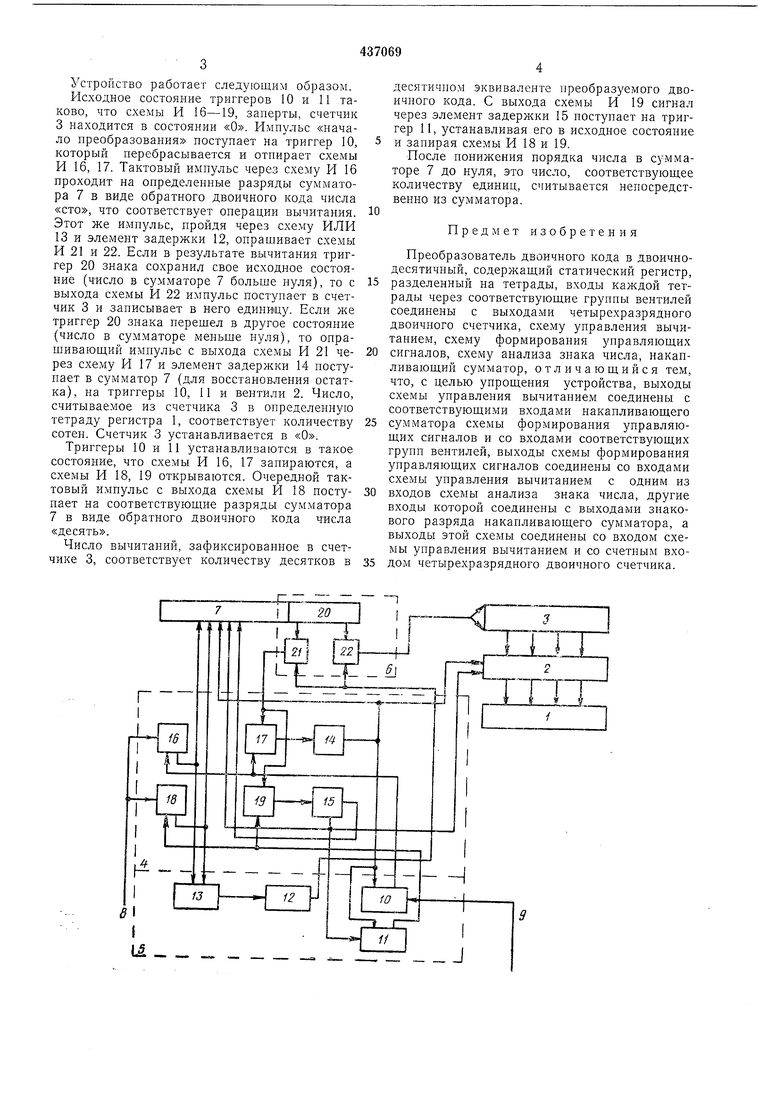

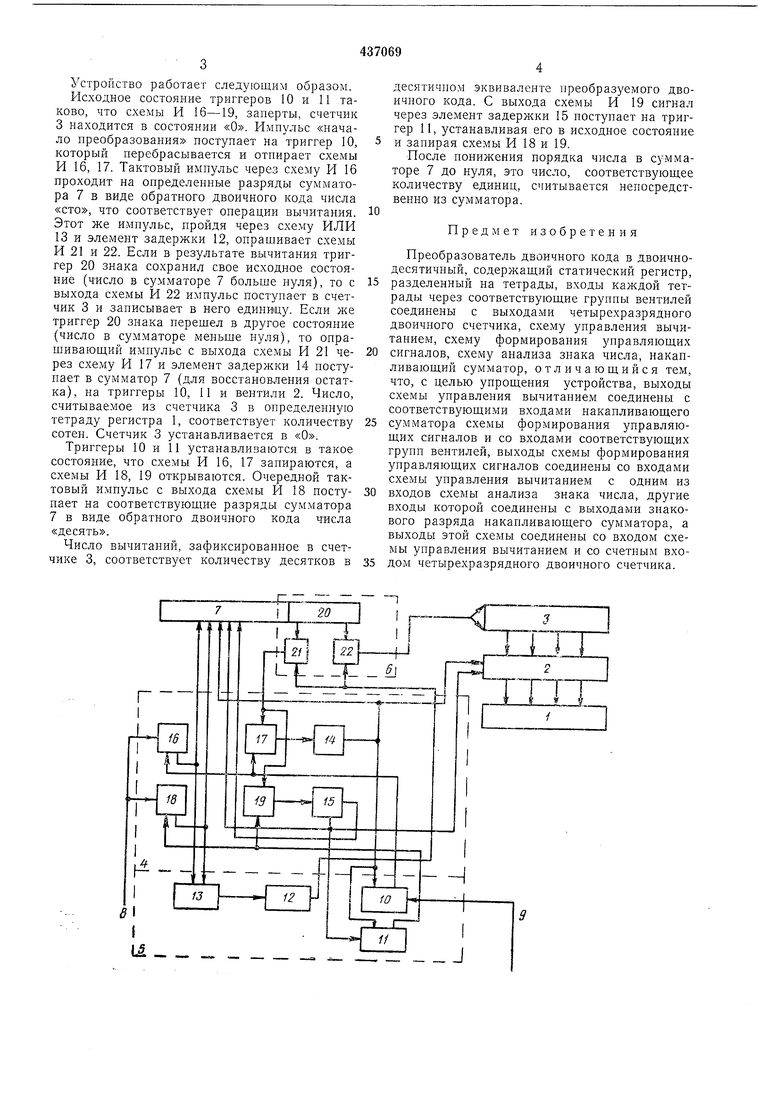

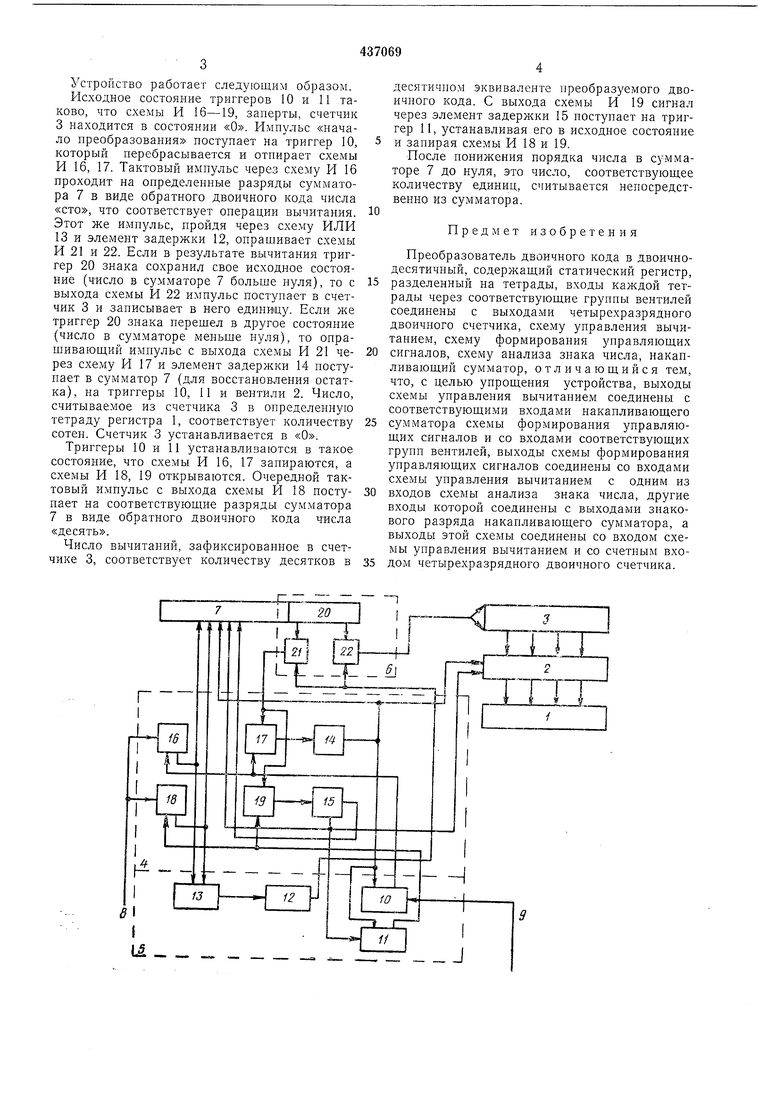

На чертеже изображена схема устройства.

Устройство содержит статический регистр 1, разделенный на тетрады, группы вентилей 2, четырехразрядный двоичный счетчик 3, схему управления вычитанием 4, схему формирования управляющих сигналов 5, схему анализа 6 знака числа, накапливающий сумматор 7, шину подачи тактовых импульсов 8, шину подачи импульса 9 «начало преобразования.

При преобразовании в трехразрядное десятичное число, схема формирования управляющих сигналов 5 реализуется на двух триггерах 10 и 11, элементе задержки 12 и схеме ИЛИ 13, схема управления вычитанием 4 содержит элементы задержки 14 и 15, схемы И 16-19; схема анализа 6 знака числа включает в себя триггер 20 знака (накапливающего сумматора 7), схемы И 21 и 22.

Устройство реализует следующий алгоритм преобразования.

В сумматор 7 вводится преобразуемое число в двоичном коде, после чего осуществляется последовательное вычитание из числа в двоичном коде его порядка в том же коде до получения младщего порядка. После каждого вычитания анализируется знак остатка числа в сумматоре 7 при помощи схемы анализа 6 и, если число больше нуля, то операция вычитания повторяется, если же число меньше нуля, то в следующем цикле происходит восстановление остатка, после чего схема формирования управляющих сигналов 5 дает разрещение на вычитание порядка, на единицу меньше 20. Это происходит до тех пор, пока порядок не будет понижен до нуля. Количество вычитаний каждого порядка подсчитывается четырехразрядным двоичным счетчиком 3. После считывания очередного порядка числа через вентили 2 в статический регистр 1, счетчик 3 устанавливается в «О.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU847318A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU690474A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Множительное устройство | 1979 |

|

SU832554A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

Авторы

Даты

1974-07-25—Публикация

1972-09-25—Подача