,г

Изобретение относится к области автоматики и вычислительной техинкк и может быть использовано в устройствах для ripeобразования кодов.

Известно, устройство для преобразования двоичного кода в двоично-десятичный, содержащее последовательный сумматор, регистр, формирователь эквивалентов и распределитель (1). Одиако эти преобразователи имеют невысокое быстродействие, так как 9 них осуществляется последовательный анализ и обработка разрядов двоичного числа.

Наиболее близким к изобретению является преобразователь двоичного кода в двоично-десятичный, содержащий первый счетчик, комбинационный Сумматор, регистр, информацнонные входы которого соединены с выходами комбинационного сумматора, и блокуправления вычитанием, входы которого соединены с выходами регистра и входами «сложеИиё комбинационного сумматора, первый выход блока управления вычитанием соединен с первым входом «вычитание комбинационного сумматора, второй выход соединен со вторым входом «вычитание {2. Кроме того, известный пре

образователь содержит анализатор знака результата, вход сложения в сумматоре, регистр результата и коммутатср.

Недостатком этого устройства является относительно невысокое быстррдействие, поскольку в нем производится вычитание двоичного эквивалента только одного десятичного разряда и возможны ошибочные шаги в. алгоритме преобразования.

Целью изобретения является повышение быстродействия преобразователя за счет совмещения обработки разных разрядов и устранения ошибочных шагов в алгоритме преобразования.

Это достигается тем, что йреобразоватедь сЬдержит второй счетчик, управляющие входы первого и второго счетчиков соединены с первым и вторым выходами блока управления вычитанием, соответственно, счетные входы обоих счетчиков соединены с шиной. тактовых импульсов и входом записи регистра, третий выход блока управления вычитанием соединен с шиной конца преобраэо| ания..

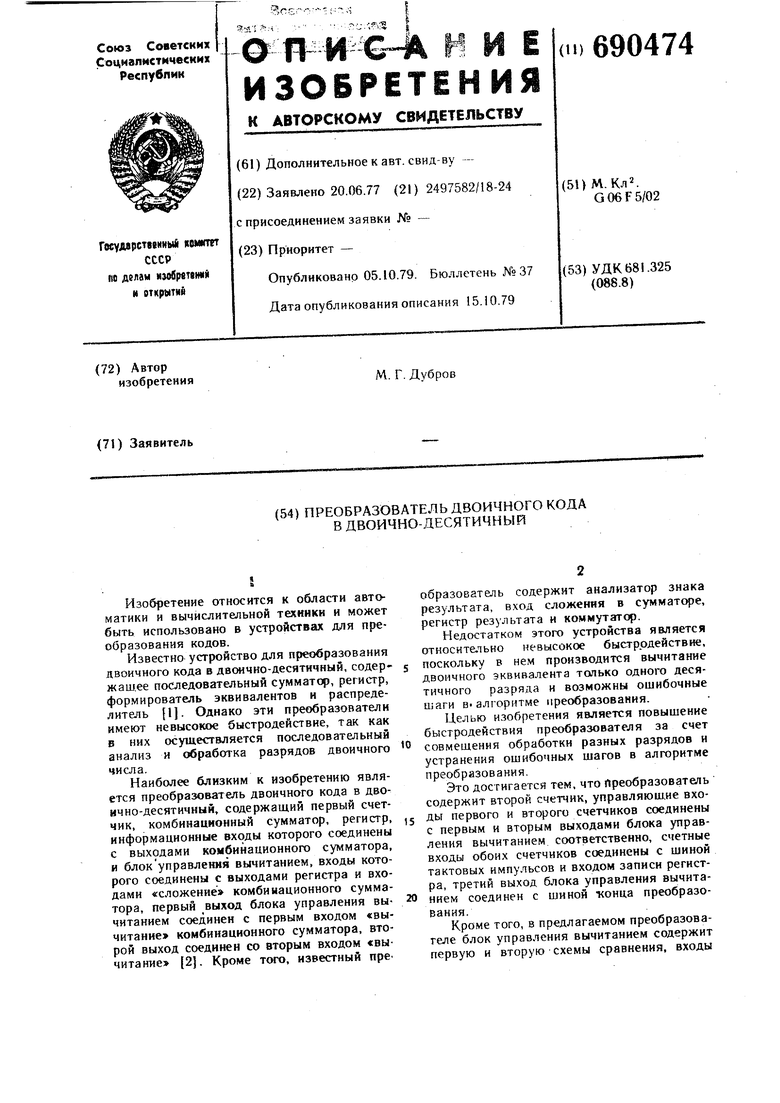

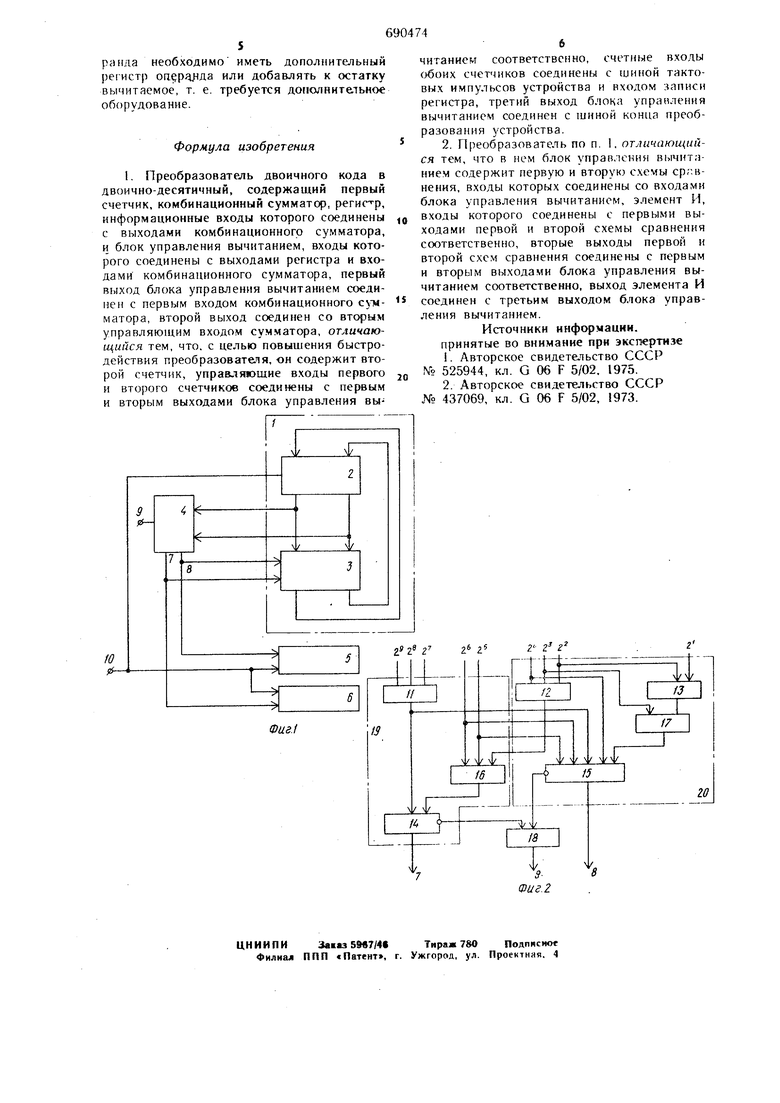

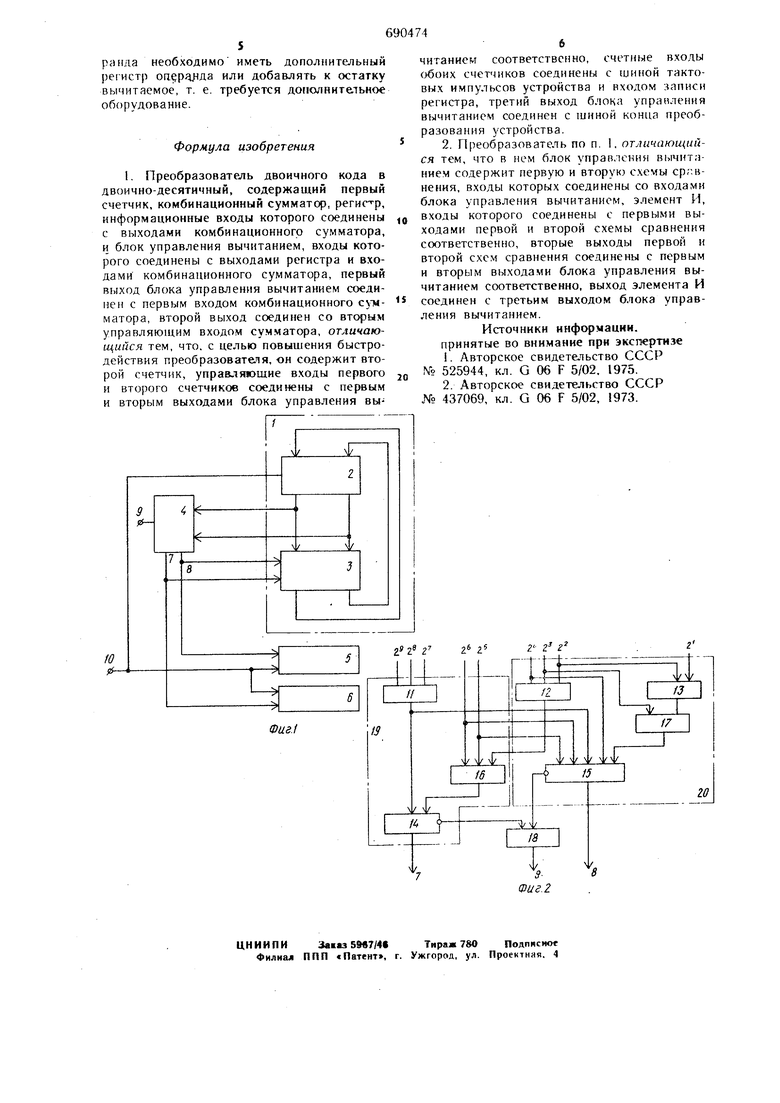

Кроме того, в предлагаемом преобразователе блок управления вычитанием содержит первую и вторую схемы сравнения, входы которых соединены со входами блока управления вычитанием, элемент И, входы которого соединены с первыми выходами первой и второй схем сравнения соответственно, вторые выходы первой и второй схем сравнения соединены с первым и вторым выходами блока управления вычитанием соответственно, выход элемента И соединен с третьим выходом блока управления вычитанием. На фиг. 1 приведена блок-схема преобразователя; на фиг. 2 - вариант реализации блока управления вычитанием для преобразования трехзарядных десятичных чисел. Преобразователь содержит накапливающий сумматор I, состоящий из регистра 2 и комбинационного сумматора 3, блок 4 управления вычитанием, счетчики 5, 6, выходы-7, 8 блока 4, щину 9 конца преобразования и щину 10 тактовых импульсов. Блок 4 построен из логических элементов ИЛИ 11 -15 элементов И 16-18 и содержит схемы сравнения 19 и 20. Выход регистра 2 соединен с входом слага.емого комбинационного сумматора 3 и с входом блока 4. Выходы 7, 8 блока 4 соединеньт со входами вычитагшя первой и второй константы комбинационного сумматора 3 и с управляющими входами счетчиков 5, 6. Счетные входы счетчиков 5, 6 и управляющий вход регистра 2 соединены с Ц1илой 10 тактовых импульсов. Иринцип работы преобразователя осно,ван на jj,i4HTaHHM из двоичного числа двоичныхэквивалентов степеней десятичного числа. Для рассматриваемого примера преобразование трехразрядных десятичных чисел из Исходного двоичного числа вычитаются двоичные коды Чисел сто и десять. В четырехразрядных двоичных счетчиках осуществляется подсчет количества вычтенных сотен-, и десятков. Как только результат операции вычитания станет меНьще десяти, преобразование заканчивается. Преобразователь работает следующим образом. В исходном состоянии в регистре 2 записа-. но преобразуемое двоичное число, двоичные счетчики 5, 6 установ.дены в «О. Код, запи.санный в регистре 2, анализируется в блоке 4. Если анализируемый код содержит «сотни, появится потенциальный сигнал на выходе 7 блока 4, если содержит «десятки - появится сигнал на выходе 8. Сигналы на выходах 7, 8 могут присутствовать одновременно. Сигнал с выхода 7 блока 4 разрешает счет в счетчике 6 и поступает в виде двоичного кода числа сто (1100100) на вторые в-ходы комбинационного сумматора 3, а сигнал с ныхода 8 разрешает счет в счетчике 5 и поступает на вторые входы сумматора 3 в виде кода числа десять (1010). На выходе сумматора 3 имеется код разности содержимого регистра 2 и кодов на вторых его входах. С приходом тактового импульса в четчики 5, 6 добавится 1 (если присутствут разре1нающие потенциалы), а р1езультат перации вычитания запишется в регистр 2. перации вычитания будут повторяться до ех пор, пока содержимое регистра 2 не удет меньше десяти, при этом в счетчиках 5, осуществляется подсчет вычтенных сотен десятков: в счетчике 6 фиксируется число отен, в счетчике 5 - число десятков. Как олько содержимое регистра 2 станет меньше есяти, появится сигнал «конец преобразования на выходе 8 блока 4, а в регистре 2. удет зафиксировано число единиц двоичноесятичного числа. Операция вычитания сотен и десятков осуществляется одновременно: в зависимости от содержимого регистра 2 в каждом такте из него будет вычтен и двоичный код числасто, десять, или числа сто десять, при этом добавится единица или только в.счетчик 6 или в оба счетчика 5, 6 одновременно. Так, например, число 683 будет преобразовано за восемь тактов, при этом в каждом -из первыхшести тактов будет вычитаться число сто десять, а в последних двух - число десять. В блоке 4 осуществляется анализ всех разрядов преобразуемого числа. Наличие на входах единичного значения одного из разрядов (7-9) (веса 128, 256, 512) свидетельствует о том, что анализируемое число содержит «сотни, об этом же свидетельствует одновременное наличие единичного значения разрядов 5-6 и одного из разрядов 2-4. В этих случаях появится сигнал на выходе 7. О наличии в анализируемом числе десятков свидетельствуют разряды 4-9 или одновременное присутствие единичного значения разряда 3 (вес 8) и одного из разрядов 1-9 или одновременное присутствие единичного значения разряда 3 (вес 8) и одного из разрядов 1-2 (веса 4,2). В этих случаях появляется сигнал на выходе 8. Анализ всех разрядов осуществляется одновременно, и сигналы на выходах 7, 8 могут присутствовать одновременно. Если анализируемое число меньше десяти, отсутст-. вуют сигналы на выходах 7, 8, появляется сигнал на выходе элемента И 18 и сигнал «конец преобразования на выходе блока 4. РеалИзация блока 4 на комбинационных схемах позволяет повысить тактовую частоту, т. е. повысить быстродействие преобразователя в пределах частотных возможносteй элементов. Время преобразования в предлагаемом преобразователе меньше,, чем в известных так как вычитание всех степеней десятичного числа осуществляется одновременно. Кроме того, предлагаемое устройство проще в реаутизации, так как в нем отпадает необходи-.. мость анализа знака остатка- после каждой операции вычитания и нет необходимости в восстановл ении операнда при отрицатель,ном знаке остатка. Для восстановления one

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1448412A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1985 |

|

SU1330762A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1990 |

|

SU1725399A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU847318A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1985 |

|

SU1396280A2 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

Авторы

Даты

1979-10-05—Публикация

1977-06-20—Подача